接下来我们开始讲GPU硬件部分和执行模型,GPU能够在并行领域中取得领先,离不了硬件的支持,这也是我们要理解和学习GPU的重点。前面几篇我们学了编写,启动核函数,计时,统计时间,然后学习了线程,内存模型,线程内存部分我们会在后面用几章的篇幅进行更详细的介绍,而本章,我们从硬件方面深入介绍内核启动配置和性能分析的信息。

CUDA中有两个很重要的模型概念。

- CUDA编程模型:主要作用在写代码、编译的过程,让我们可以很方便的利用多种语言,更好的控制GPU,并编译出GPU可以理解的代码。其中两个主要的抽象概念:内存层次结构和线程层次结构。

- CUDA执行模型:主要作用在写好代码,执行的过程,即将代码作用到硬件的过程,有助于在指令吞吐量和内存访问方面提高代码效率。

1. GPU架构概述

GPU架构是围绕一个流式多处理器(SM)的扩展阵列搭建的。通过复制这种结构来实现GPU的硬件并行。相同架构的GPU包含的SM数量通常代表了GPU的性能定位,有的低端GPU配备了1个SM,部分高端GPU则可以拥有多达数百个SM。而GPU类型则定义了这些SM的功能。SM结构下又会细分出不同的功能区域以及核心,这里简单介绍最重要的组成之一:流处理器。

流处理器(Streaming Processor ,简称SP)是GPU最基本的处理单元。每个SM中包含多个SP,由GPU架构决定其功能区别。我们所说的GPU中有几千个核心或者cuda单元中,这个几千指的就是流处理器的数量。流处理器只相当于CPU处理器中的执行单元,负责执行指令进行运算,并不包含控制单元(GPU的控制单元为Warp与指令调度单元)。

当启动一个内核网格时,它的线程块被分布在了可用的SM上来执行。线程块一旦被调度到一个SM上,其中的线程只会在那个指定的SM上并发执行,直到执行完成。多个线程块可能会被分配到同一个SM上,而且是根据SM资源的可用性进行调度的。

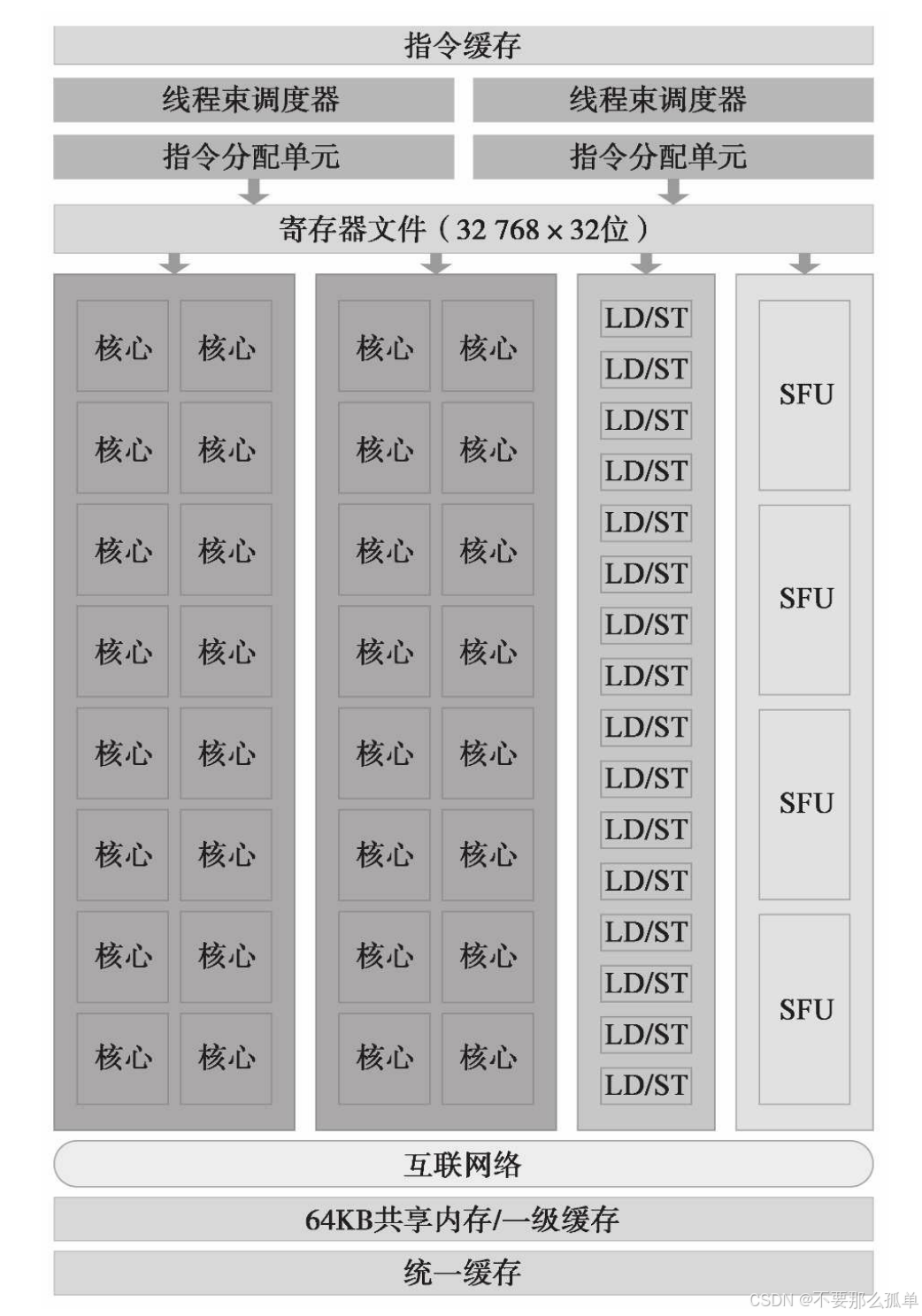

Fermi SM的关键组件,如下图所示:

- CUDA核心

- 共享内存/一级缓存

- 寄存器文件

- 加载/存储单元

- 特殊功能单元

- 线程束调度器

1.1 线程束

CUDA采用单指令多线程(SIMT)架构来管理和执行线程,每32个线程为一组,被称为线程束(warp)。线程束中的所有线程同时执行相同的指令。每个线程都有自己的指令地址计数器和寄存器状态,利用自身的数据执行当前的指令。

每个SM上有多个block,一个block有多个线程,但在执行的时候,在某时刻Tÿ

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?