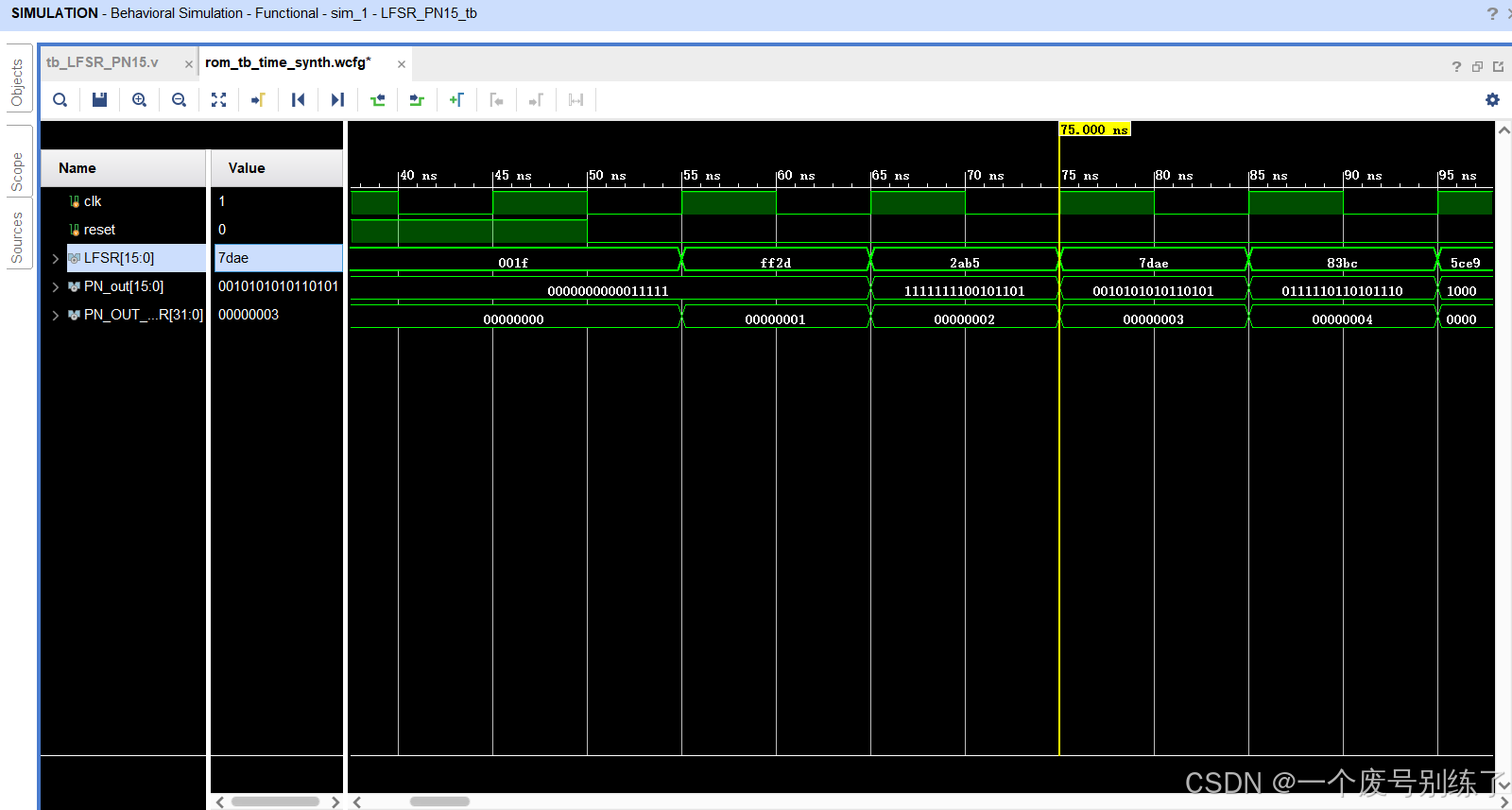

已经结合单bit输出验证:

已经结合单bit输出验证:

源码:

module LFSR_PN15 (

input clk,

input reset,

output reg [15:0] LFSR,

output reg [15:0] PN_out,

output reg [31:0] PN_OUT_COUNTER

);

always @(posedge clk) begin

if (reset)begin

LFSR <= 16'b0000_0000_0001_1111; // 同步复位

PN_OUT_COUNTER<=0;

end else begin

LFSR[15] <= LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15];

LFSR[14] <= LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14];

LFSR[13] <= LFSR[1] ^ LFSR[10]^LFSR[12] ^ LFSR[13];

LFSR[12] <= LFSR[0] ^ LFSR[9]^LFSR[11] ^ LFSR[12];//前4个没有变化

LFSR[11] <= (LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15])

^ LFSR[8]^LFSR[10] ^ LFSR[11];

LFSR[10] <= (LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14])

^ LFSR[7]^LFSR[9] ^ LFSR[10];

LFSR[9] <= (LFSR[1] ^ LFSR[10]^LFSR[12] ^ LFSR[13])

^ LFSR[6]^LFSR[8] ^ LFSR[9];

LFSR[8] <= (LFSR[0] ^ LFSR[9]^LFSR[11] ^ LFSR[12])

^ LFSR[5]^LFSR[7] ^ LFSR[8];

LFSR[7] <= (LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15] ^ LFSR[8]^LFSR[10] ^ LFSR[11] )

^ LFSR[4]^LFSR[6] ^ LFSR[7];

LFSR[6] <= (LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14] ^ LFSR[7]^LFSR[9] ^ LFSR[10])

^ LFSR[3]^LFSR[5] ^ LFSR[6];

LFSR[5] <= (LFSR[1] ^ LFSR[10]^LFSR[12] ^ LFSR[13] ^ LFSR[6]^LFSR[8] ^ LFSR[9] )

^ LFSR[2]^LFSR[4] ^ LFSR[5];

LFSR[4] <= (LFSR[0] ^ LFSR[9]^LFSR[11] ^ LFSR[12] ^ LFSR[5]^LFSR[7] ^ LFSR[8] )

^ LFSR[1]^LFSR[3] ^ LFSR[4];

LFSR[3] <= ( LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15] ^ LFSR[8]^LFSR[10] ^ LFSR[11] ^ LFSR[4]^LFSR[6] ^ LFSR[7])

^ LFSR[0]^LFSR[2] ^ LFSR[3];//前13个

LFSR[2] <= (LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14] ^ LFSR[7]^LFSR[9] ^ LFSR[10] ^ LFSR[3]^LFSR[5] ^ LFSR[6] )

^ (LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15])^LFSR[1] ^ LFSR[2];

LFSR[1] <= (LFSR[1] ^ LFSR[10]^LFSR[12] ^ LFSR[13] ^ LFSR[6]^LFSR[8] ^ LFSR[9] ^ LFSR[2]^LFSR[4] ^ LFSR[5])

^ (LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14])

^LFSR[0] ^ LFSR[1];

LFSR[0] <= (LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15] ^ LFSR[8]^LFSR[10] ^ LFSR[11] ^ LFSR[4]^LFSR[6] ^ LFSR[7] ^ LFSR[0]^LFSR[2] ^ LFSR[3])

^ (LFSR[0] ^ LFSR[9]^LFSR[11] ^ LFSR[12] )

^ (LFSR[2] ^ LFSR[11]^LFSR[13] ^ LFSR[14])

^ (LFSR[3] ^ LFSR[12]^LFSR[14] ^ LFSR[15])

^ LFSR[0]; // 最高位反馈移位

PN_OUT_COUNTER<=PN_OUT_COUNTER+1;

end

PN_out <= LFSR;

end

endmodule仿真testbench:

`timescale 1ns / 1ps

module LFSR_PN15_tb;

// Inputs

reg clk;

reg reset;

// Outputs

wire [15:0] LFSR;

wire [15:0] PN_out;

wire [31:0] PN_OUT_COUNTER;

// Instantiate the Unit Under Test (UUT)

LFSR_PN15 uut (

.clk(clk),

.reset(reset),

.LFSR(LFSR),

.PN_out(PN_out),

.PN_OUT_COUNTER(PN_OUT_COUNTER)

);

// Clock generation: 10ns period (100 MHz)

always #5 clk = ~clk;

initial begin

// Initialize Inputs

clk = 0;

reset = 1;

// Wait 50 ns for global reset to finish

#50 reset = 0;

// Wait for a few cycles to observe the output

#500;

// Apply reset again after some time

reset = 1;

#50 reset = 0;

// Wait to observe more outputs

#500;

// End simulation

$stop;

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?