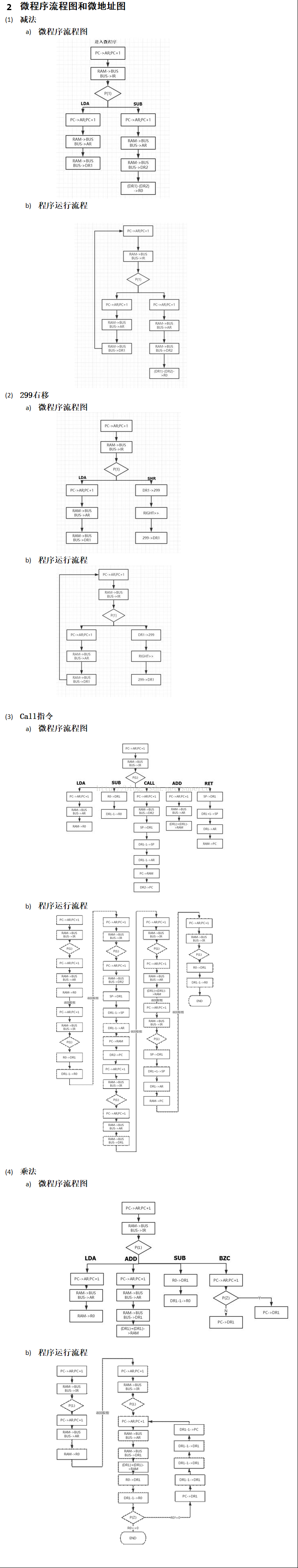

- 设计原理

算术运算

将需要计算的数放入指定寄存器中后调用不同的微操作就可以实现不同的算术运算,需要修改的仅仅是一行代码,下面以减法为例,只需要令CBA=010,AN=1,S1=1,S2=1,DR0=1就可以实现DR1-DR2,并且将计算结果放入R0,即微操作为40 26 02 80。

逻辑运算

逻辑运算依旧借助于ALU实现,所以基本流程也是将需要进行逻辑运算的数放入DR1和DR2,然后修改CBA,CN,M,S0,S1,S2,S3就可以实现多种操作,下面不再给出整个微程序。

可以实现的指令

AND,OR,NOT

AND微操作40 17 02 80

OR微操作40 1D 02 80

NOT微操作40 00 02 80

移位运算

移位运算通过74LS299芯片实现,首先将需要进行移位的数值放入299芯片,即置数,然后通过控制S0,S1实现操控299实现左移和右移,通过控制M实现带进位左移和带进位右移。

移位运算的实现需要三步,第一步是将需要移位的数放入299,即A0 0C 00 90;第二步是进行移位操作,即60 04 00 50;第三步是将运算后的数取出放入寄存器,即60 00 02 80。

CALL、RET指令

微程序执行过程中执行到CALL指令时会跳转到CALL指令给出的子程序地址,即将CALL指令给出的子程序入口地址放入PC,再进行PC->AR,执行子程序,但是在跳转到子程序执行之前需要将本来要执行的下一指令的地址保存起来,然后当执行完子程序需要返回时,需要将保存的地址拿出,放入PC,再返回执行,这样就可以实现执行完子程序后继续执行原有程序的功能。

MUL、BZC指令

乘法指令通过连加实现,即将被乘数与乘数放在内存中,先将乘数取出放入R0,作为计数,即表示需要连加多少次才能实现乘法,然后将被乘数取出放入DR1和DR2,进行加法运算,将得出的结果再放入储存被乘数的内存地址中,即表示执行完乘法运算后,被乘数没有被保留,如果要保留被乘数的话,由于寄存器只有R0,DR1,DR2可用,所以需要将中间结果放入某个内存地址,其必然会更繁琐,减慢速度。接下来将R0-1再放入R0,然使用P(Z)标注测试,如果乘数变为0,表示连加完成,否则通过修改PC使其再次执行连加运算,直到R0为全0,即跳出循环,完成乘法。乘法指令这里使用的是简单方法,容易实现但效率不高,更合理的方法在下面。

HLT指令

HLT即停机指令,即执行到该指令就停止,不再执行其他指令,可以使其下地址执行本身地址即可。

微指令实现

例:M2C 00 00 00 34

JMP指令

JMP指令可以实现跳转到指定位置,具体实现为将JMP给出的地址放入AR,取出在RAM存储的需要跳转到的位置,放入PC,再次取指执行就可以了,JMP为无条件跳转,而且跳转后由于未保存本来要执行的下一条地址,所以无法返回。

微指令实现

20 00 60 __ ;PC→AR,PC+1

00 C0 20 80 ;RAM→PC

- 机器指令程序和微程序码点表

减法

;PXX XX

;DIEZHI JIQIDAIMA

P00 40 09 ;LDA DR1,09H ;

P02 60 0A ;SUB DR1,0AH ;

;------------以下为数据空间------------

P09 AA

P0A 55

M00 00 00 00 80 ;

M01 20 00 60 40 ;PC→AR,PC+1

M02 00 80 10 12 ;RAM→IR

M03 00 80 40 20 ;RAM→AR

M04 00 80 04 70 ;RAM→DR1

M05 00 80 40 E8 ;RAM→AR (0AH)->AR

M06 00 80 08 E0 ;RAM→DR2

M07 40 26 02 80 ;DR1-DR2->R0

M08 00 00 00 80 ;

M09 00 00 00 80 ;

M0A 20 00 60 C0 ;

M0F 00 00 00 80 ;

M10 00 00 00 80 ;

M11 00 00 00 80 ;

M12 00 00 00 80 ;

M13 00 00 00 80 ;

M14 00 00 00 80 ;

M15 00 80 08 E0 ;

M16 00 80 08 E0 ;

M17 00 80 08 E0 ;RAM→DR2

可以实现的指令

ADD,SUB,ADC,SBC

依旧将需要计算的数放入DR1和DR2,最后修改的只是进行计算的那一行微操作。

ADD微操作50 29 02 80

SUB微操作40 26 02 80

ADC微操作50 09 02 80

SBC微操作50 06 02 80

299右移

;PXX XX

;DIEZHI JIQIDAIMA

P00 40 09 ;LDA R0,09H ;

P02 60 ;RR R0 ;

;------------以下为数据空间------------

P09 55

M00 00 00 00 80 ;

M01 20 00 60 40 ;PC→AR,PC+1

M02 00 80 10 12 ;RAM→IR

M03 00 80 40 20 ;RAM-AR,QU09

M04 00 80 04 80 ;RAM-DR1

M08 A0 0C 00 90 ;DR1-299,TO 09

M09 60 04 00 50 ;<<1 55-54

M0A 60 00 02 80 ;299-DR

M0B 20 00 60 A0 ;

M0C 20 00 60 C0 ;

M0D 00 00 00 80 ;

M0E 20 00 60 10 ;PC-AR ,TO 08

M0F 00 00 00 80 ;

M10 60 00 02 80 ;299-DR1

M11 00 00 00 80 ;

M12 00 00 00 80 ;

M13 00 00 00 80 ;

M14 00 00 00 80 ;

M15 00 80 08 E0 ;

M16 00 80 08 E0 ;

M17 00 80 08 E0 ;

可以实现的指令

SHR,SHL

SHR微操作60 04 00 50

SHL微操作60 08 00 50

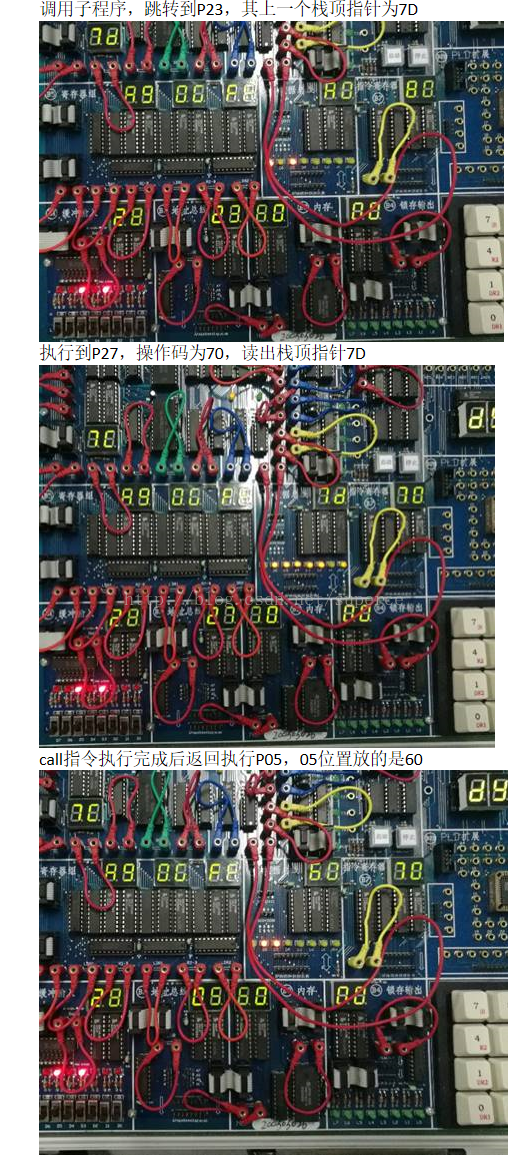

CALL、RET指令

;CALL

;PXX XX

;DIEZHI JIQIDAIMA

P00 40 0B ;LDA R0,0BH ;

P02 60 ;SUB R0 ;

P03 80 23 ;CALL 23H ;

P05 60 ;SUB R0 ;

;------------->->->->->->->------------

P0A 55

P0B AA

P0C 55

;------------->->->------------

P23 A0 0A ;LDA 0A,DR1

P25 90 0A ;ADD 0A,DR1

P27 70 ;RET

M00 00 00 00 80 ;->->->

M01 20 00 60 40 ;PC->AR,PC+1

M02 00 80 10 12 ;RAM->IR

M03 00 80 40 20 ;RAM->AR

M04 00 80 02 80 ;RAM->R0

M05 80 00 04 60 ;R0->DR1

M06 50 2F 02 80 ;DR1-1->R0

M07 50 29 02 80 ;

M0D 60 04 00 48 ;299

M0E 00 00 00 A0 ;PC->AR,PC+1

M0F 00 00 00 58 ;PC->AR,PC+1

M10 60 08 00 48 ;

M11 00 80 08 48 ;RAM->DR2

M12 E0 00 04 C8 ;SP->DR1

M13 42 2F 00 28 ;DR1-1->SP

M14 40 2F 40 84 ;DR1-1->AR qu 21

M15 40 55 20 80 ;DR2->PC

M16 00 80 40 E8 ;RAM->AR

M17 00 80 04 80 ;RAM->DR1

M18 00 80 40 98 ;RAM->AR

M19 40 A3 01 80 ;DR1+DR1->RAM

M1A E0 00 04 D8 ;SP->DR1

M1B 42 00 00 38 ;DR1+1->SP

M1C 40 20 40 B8 ;DR1->AR

M1D 00 C0 20 80 ;RAM->PC

M1E 00 00 00 80 ;(CY.Z=0->->)

M1F 00 00 80 72 ;(CY.Z=1)

M20 00 00 02 81 ;SW->Rd

M21 20 80 01 A8 ;Rd->299 qu 15

M22 20 00 60 20 ;PC->AR,PC+1

M23 20 00 60 88 ;PC->AR,PC+1

M24 20 00 60 10 ;PC->AR,PC+1

M25 04 00 00 8E ;0->ED,

M26 20 00 60 50 ;PC->AR,PC+1

M27 20 00 60 1C ;PC->AR,PC+1

M28 20 00 40 30 ;PC->AR

M29 04 40 00 80 ;1->EA,

M2A A0 0C 00 B0 ;Rd->299

M2B 04 00 00 80 ;0->EA,

M2C A0 0C 00 F0 ;Rd->299

M2D A0 00 04 58 ;Rd->DR1

M2E A0 0C 00 08 ;Rd->299

M2F 20 00 60 D8 ;PC->AR,PC+1

M30 00 00 00 80 ;

M31 E0 00 04 4C ;SP->DR1

M32 42 00 00 CC ;DR1+1->SP

M33 40 20 40 6C ;DR1->AR

M34 80 00 04 AC ;Rs->DR1

M35 50 06 00 18 ;DR1-DR2

M36 00 C0 20 80 ;RAM->PC

M37 00 00 00 80 ;

M38 00 80 02 80 ;RAM->Rd

M39 00 00 00 80 ;

M3A 00 00 00 80 ;

M3B 00 00 00 80 ;

M3C 00 00 08 C9 ;SW->DR2

M3D 40 6F 20 3C ;DR1-1->PC

M3E 20 00 04 BC ;PC->DR1

M3F 04 40 00 7E ;1->ED,

MUL、BZC指令

;乘法

;PXX XX

;DIEZHI JIQIDAIMA

P00 400B ;LDA R0,0BH ;

P02 700A ;LDA DR1,0AH ;

P04 800A ;ADD 0AH ;

P06 A0 ;SUB R0 ;

P07 90 ;BZC ;

;------------->->->->->->->------------

P0A 03

P0B 02

P0C 55

M00 00 0000 80 ;

M01 20 0060 40 ;PC-AR,PC+1

M02 00 8010 12 ;RAM-IR

M03 00 8040 20 ;RAM-AR

M04 00 8002 80 ;RAM--R0

M05 80 0004 60 ;R0-DR1

M06 50 2F02 80 ;DR1-1->R0

M07 50 2902 80 ;

M0D 60 0400 48 ;299->->

M0E 20 0004 5C ;PC->DR1 ==3A

M0F 20 0060 68 ;PC->AR,PC+1

M10 60 0800 48 ;

M11 00 8040 48 ;RAM->AR

M12 40 A301 80 ;DR1+DR1->RAM

M13 80 0004 28 ;R0->DR1

M14 50 2F02 F8 ;DR1-1->R0

M15 40 5520 80 ;

M16 00 8040 E8 ;RAM-AR

M17 00 8004 80 ;RAM-DR1

M18 00 8040 98 ;RAM->AR

M19 40 A301 80 ;DR1+DR1->RAM

M1A E0 0004 D8 ;SP->DR1

M1B 42 0008 38 ;DR1+1->SP

M1C 40 2040 B8 ;DR1->AR

M1D 00 C020 80 ;RAM->PC

M1E 00 0000 80 ;(CY.Z=0->->)

M1F 00 0080 72 ;(CY.Z=1)

M20 00 0002 81 ;

M21 A0 0C00 C0 ;

M22 20 0060 20 ;

M23 20 0060 88 ;

M24 20 0060 10 ;

M25 04 0000 8E ;

M26 20 0060 50 ;PC->AR,PC+1

M27 20 0060 1C ;PC->AR,PC+1

M28 20 0040 30 ;PC->AR

M29 04 4000 80 ;

M2A A0 0C00 B0 ;Rd->299

M2B 04 0000 80 ;

M2C A0 0C00 F0 ;Rd->299

M2D A0 0004 58 ;Rd->DR1

M2E A0 0C00 08 ;Rd->299

M2F 20 0060 D8 ;PC->AR,PC+1

M30 00 0000 80 ;

M31 E0 0004 4C ;SP->DR1

M32 42 0000 CC ;DR1+1->SP

M33 40 2040 6C ;DR1->AR

M34 80 0004 AC ;

M35 50 0600 18 ;

M36 00 C020 80 ;

M37 00 0000 80 ;

M38 00 8002 80 ;

M39 00 0000 80 ;

M3A 40 6F04 DC ;DR1-1->DR1 F0

M3B 40 6F04 3C ;DR1-1->DR1

M3C 40 6F04 BC ;DR1-1->DR1

M3D 40 6F20 F0 ;DR1-1-DR1

M3E 40 6F20 F0 ;DR1-1->PC

M3F 04 4000 7E ;

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?