这两天不知咋了,小编老关注到一些奇奇怪怪的玩意儿。

今儿是一家公司新发布了一款 8KB 容量的 U 盘。

你说这年头还有谁会买内存只有 8KB 的 U 盘呀?

现在随随便便拍一张照片都 100KB 了好吧。

咋现在还要做一款这样的 U 盘呢?

仔细一看,更觉得离谱了。

这么小内存的 U 盘,最大的卖点是能用 200 年......

看细节 ~

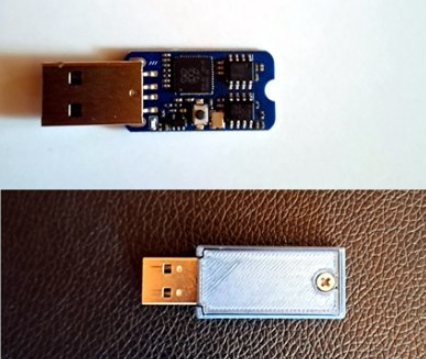

这玩意儿是德国一家名叫 Machdyne 的存储公司发布的。

咱正常买 U 盘,肯定优先看容量、性能那些,不会专挑这种内容贼小但是可以用到天荒地老的 U 盘吧。

但这家公司的人才有种 “ 我不要你喜欢,只要我喜欢 ” 的心态,偏偏就做出了这款 8KB 容量、寿命 200 年以上的特殊 U 盘。

而且!这小玩意儿还不便宜哦,发布定价 29.95 欧元(约人民币 235.57 元)。

你说这价格,买个正常的 U 盘,可选择的太多了吧,为啥要买你这个呢?

针对这个价格,人家说,这个 8KB 的特殊 U 盘之所以卖这么贵,因为成本高啊!

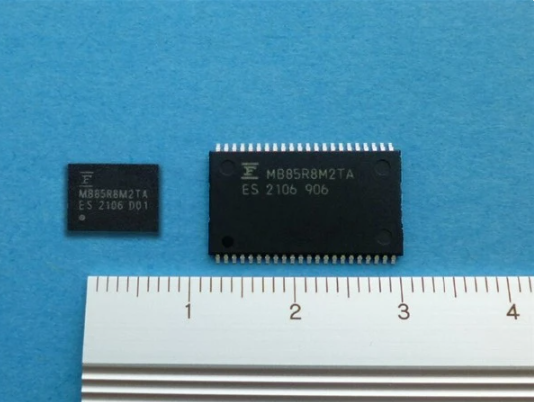

说是这款特殊 U 盘用了一种 FRAM 存储介质,也可以看作铁电存储器。

综合对比之下,采用这种特殊介质,可以让这款 U 盘在高速读写入、高读写耐久性、低功耗和防窜改等方面都具有优势。

这种 FRAM 存储介质,不仅成本高,而且还有一个致命的缺点就是容量密度做不大。

第一个 FRAM 产品,是在 1993 年由 “ 漂亮国 ” 一家叫 RAmtron 的公司开发出来的,当时这款 FRAM 产品只有 4KB 。

这东西开发出来谁在用?

与之对应的,就用在那些对容量没有高要求,但是对寿命、速度等方面有要求的设备上。

仔细想一下,主要面向一些科技工业场景上了。

提一句,近些年来 FRAM 目前在汽车、IC 卡等领域都有所应用,主要厂商有英飞凌、富士通半导体等等。

再说回这款 8KB 的 U 盘。

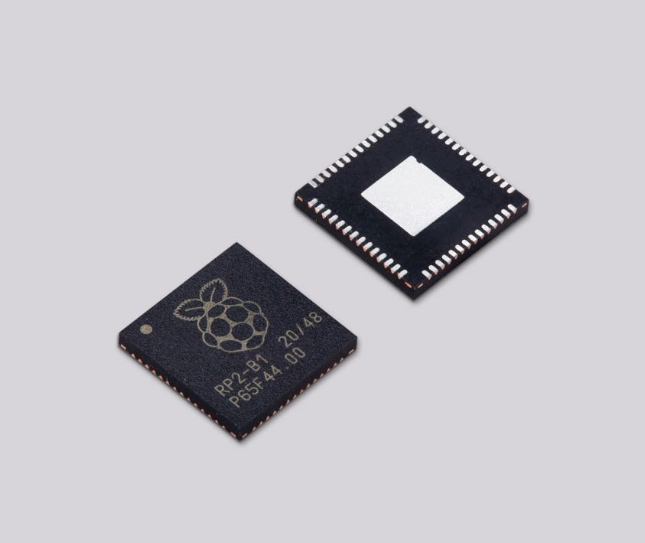

这玩意儿还配了树莓派 RP2040 微控制器。

RP2040 是树莓派首次推出的微控制器,其标志性价值在于高性能、低动态功耗和低泄漏等特点,并提供多种低功耗模式。

还有!这款 8KB 的 U 盘有 4MB NOR Flash 闪存(固件)、一个 USB-A 接口。

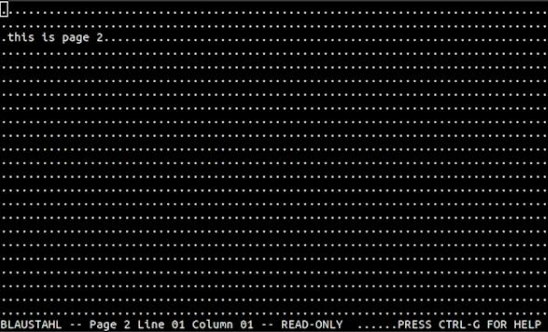

内置文本编辑器,可通过 PuTTY、Tera Term 之类的串行通信程序访问。

谁懂这个点?存个 8KB 数据用 4MB 固件驱动,还是 USB-A 接口......

讲这么多,重点考虑这一句:

相关单位或部门,或许可以用这个 U 盘在特殊环境下保存一些敏感的数据,包括密码、记录等等这些特殊内容......

更有看点的是网友的评论:

“ 200 年?闪存颗粒没坏,USB 淘汰了。 ”

“ 还是刻石头来得保险些。 ”

“ 控制器撑不住先走了。 ”

“ 200 年也没啥用,宇宙级文明十万年起步。 ”

这届网友真的很绝,好了,压力给到我们评论区了。

你们怎么看?

不过,小编也挺好奇的,你们有没有什么密码啊啥的,是需要用这玩意儿来保存的?

有的话,这需求还真就匹配上了......

9996

9996

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?