锁相环 PLL SPLL,DSP28335程序 单相锁相环 频率跟踪 相位跟踪

锁相环(PLL)和单相锁相环(SPLL)是在现代电子、通信、控制系统中广泛应用的重要技术。其中,SPLL是一种常见的数字锁相技术,它通过数字信号处理实现对输入信号的相位锁定和频率跟踪。而DSP28335则是一种高性能数字信号处理器,可用于实现SPLL等锁相环技术。

在电力电子领域中,电网同步性是一个重要的技术问题。SPLL技术能够有效地解决这个问题,实现电网同步和控制,提高电力电子设备的性能和可靠性。在具体应用中,需要根据电力电子系统的特点和工作环境选择合适的SPLL方案和参数设置。

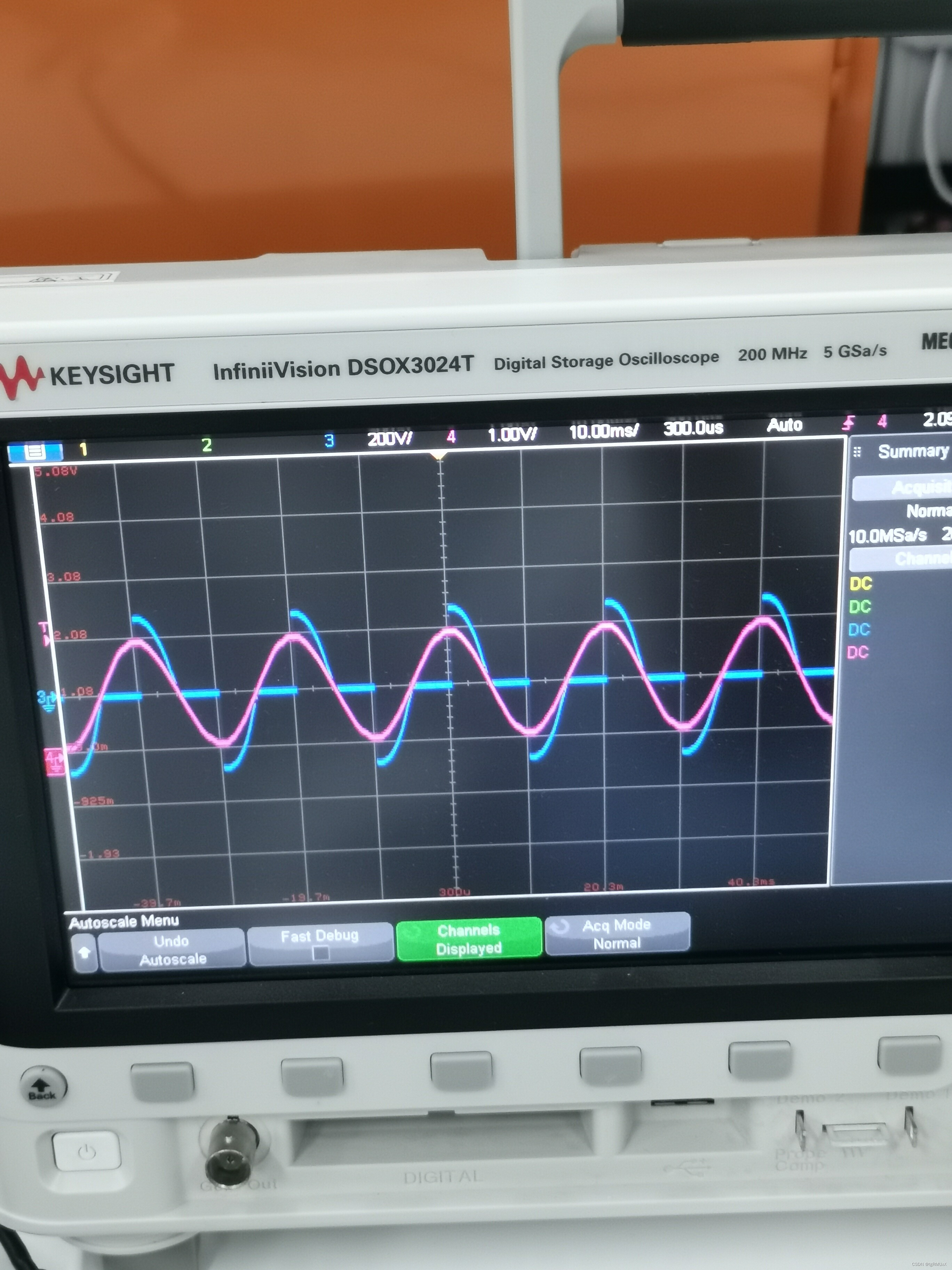

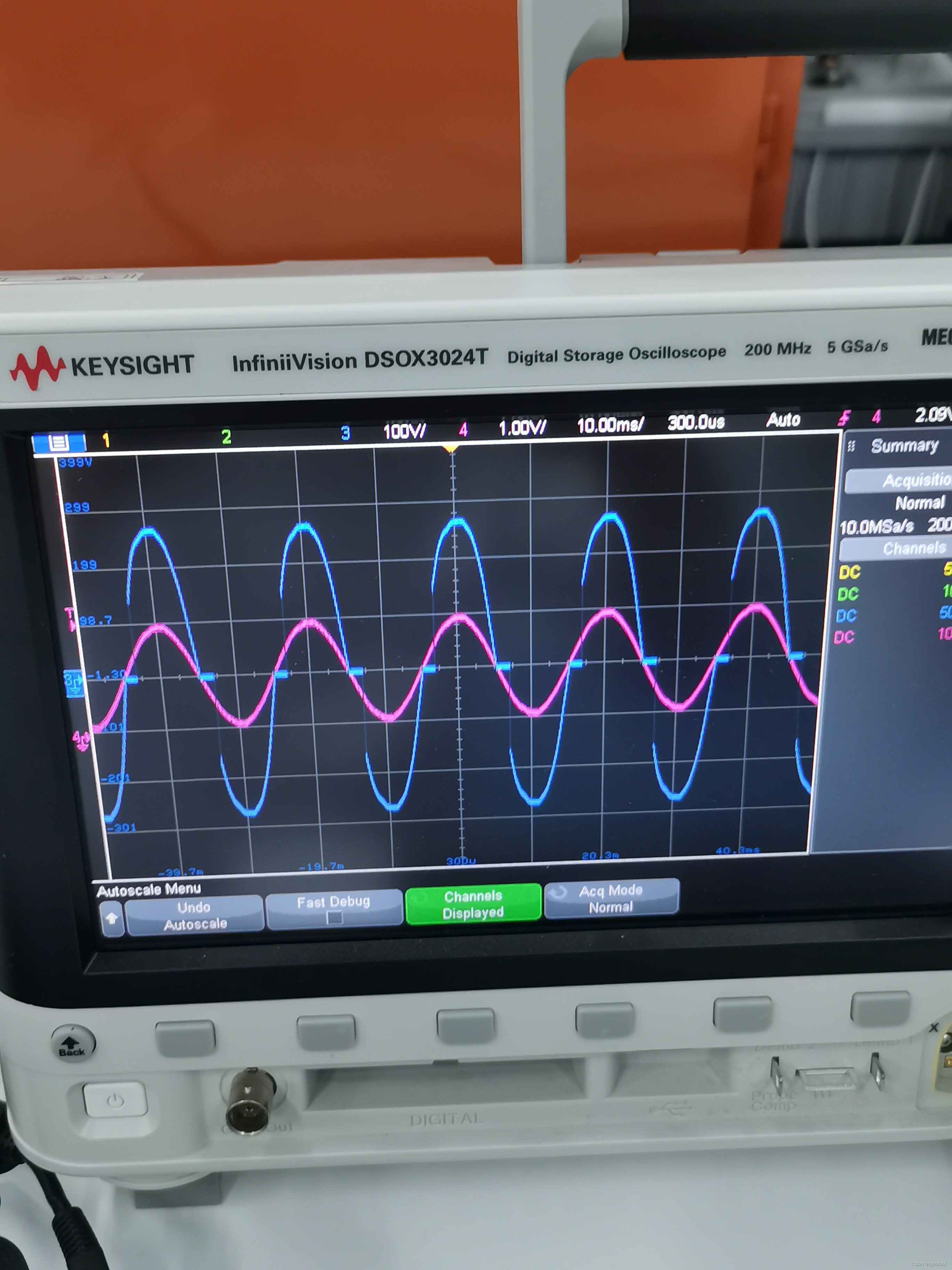

在SPLL的实现中,频率跟踪和相位跟踪是两个关键的环节。频率跟踪的主要任务是实时测量输入信号的频率变化,并对锁相环的参考频率进行调整,以实现对输入信号的同步跟踪。相位跟踪则是基于已知的频率信息,实现对输入信号相位的锁定和跟踪,从而实现相位同步和控制。

在进行SPLL设计和实现时,需要考虑多种因素,如锁相环参数的选择、数字信号处理算法的优化、硬件电路设计和噪声抑制等。同时,还需要注意SPLL对系统稳定性和动态性能的影响,尤其是在高功率电力电子系统中应用时,需要对SPLL进行充分的测试和验证。

总之,锁相环技术是一种重要的数字信号处理技术,在现代电力电子、通信和控制系统中具有广泛的应用前景。在DSP28335的支持下,SPLL技术的实现也更加便捷和高效。未来,我们可以进一步探索数字锁相技术的创新和应用,为智能制造和可持续发展做出贡献。

相关代码,程序地址:http://lanzouw.top/624897173929.html

2606

2606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?