DSP原理学习笔记(四)

第四章 锁相环

4.1 概 述

锁相环由锁相环乘法器(PLLM)、分频器(OSCDIV1、D0、D1、D2、D3)和复位控制器等组成

CLKIN:从外部晶体振荡器的输入信号(3.3V),CLKMODE0 = 1

锁相环控制器的输出时钟包括:

SYSCLK1:分频器D1的内部时钟输出,用于DSP内核

SYSCLK2:分频器D2的内部时钟输出,用于DSP外围设备

SYSCLK3:分频器D3的内部时钟输出,生成ECLKOUT

CLKOUT3:分频器OSCDIV1的外部时钟输出,用于系统其它设备

AUXCLK:直接来自于CLKIN的内部时钟信号,用于McASP

4.2 功能描述

当PLLEN = 1时为锁相环模式,分频器D0必须被使能(D0EN=1),由寄存器PLLDIV0中锁相环分频器比例位(PLLDIVx)分频;根据锁相环乘法控制寄存器(PLLM)中的锁相环倍频位(PLLM)的数值来倍频。

当PLLEN=0时为旁路模式,输入参考时钟被直接输入到分频器D1、D2和D3

当使能分频器D1、D2和D3时(DnEN=1),根据寄存器PLLDIVn中的数值,对锁相环的输出时钟进行分频。

4.3 配置锁相环

1. 锁相环的初始化

(1) 锁相环模式(PLLEN=1),当系统要使用分频器D0和锁相环的时候,进行此初始化过程

在PLLCSR寄存器中,设置PLLEN=0(禁用模式)

等待4个周期的PLLOUT信号,CLKMODE = 1时为CLKIN

在PLLCSR寄存器中,设置PLLRST=1(PLL被复位)

对PLLDIV0、PLLM和OSCDIV1编程

对PLLDIV1-3编程,必须执行此操作来使分频器更新比例系数

等待锁相环正确地复位

在PLLCSR寄存器中,设置PLLRST=0,使锁相环退出复位状态

等待锁相环锁定

在PLLCSR寄存器中,设置PLLEN=1来使能锁相环模式

(2) 旁路模式(PLLEN=0),当系统需旁路分频器D0和锁相环的时候,进行此初始化过程

在PLLCSR寄存器中,设置PLLEN=0(禁止模式)

等待4个周期的PLLOUT信号,CLKMODE = 1时为CLKIN

在PLLCSR寄存器中,设置PLLRST=1(PLL被复位)

对OSCDIV1编程

对PLLDIV1-3编程,必须执行此操作来使分频器更新比例系数

2. 执行下列操作来关闭锁相环

在寄存器PLLCSR中,令PLLEN=0(旁路模式)。

等待4个周期的PLLOUT信号,CLKMODE = 1时为CLKIN

在寄存器PLLCSR中,令PLLPWRDN=1来关闭锁相环。

3. 执行下列操作从关闭模式唤醒锁相环:

在寄存器PLLCSR中,令PLLEN=0(旁路模式)。

等待4个周期的PLLOUT信号,CLKMODE = 1时为CLKIN

在寄存器PLLCSR中,令PLLPWRDN=0来唤醒锁相环。

执行在初始化中讲述的锁相环复位顺序来复位锁相环。等待锁相环锁定,然后从旁路模式切换到锁相环模式。

4.4 控制寄存器

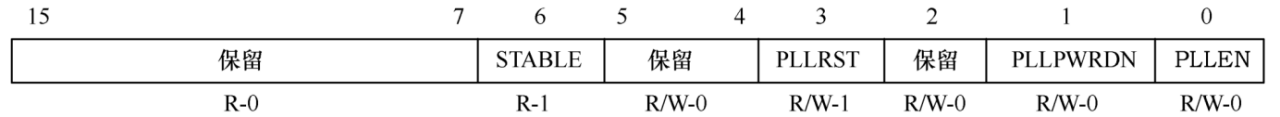

锁相环控制状态寄存器(PLLCSR)

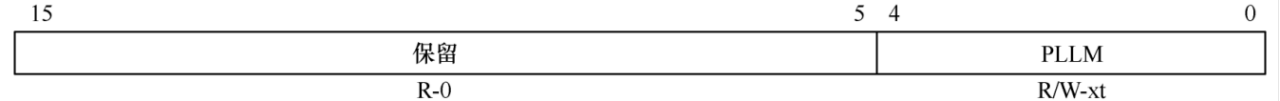

锁相环乘法寄存器(PLLM)

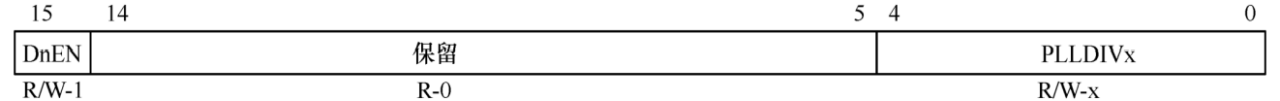

锁相环分频寄存器(PLLDIV0-3)

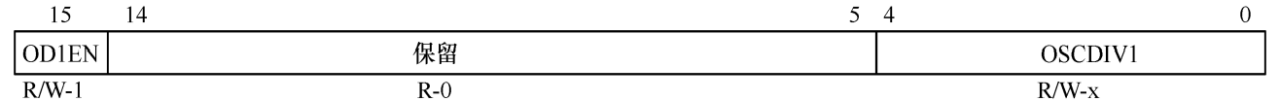

震荡分频1寄存器(OSCDIV1)

泰克混合示波器Tektronix MSO4104

1139

1139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?