6678中断概述

中断(Interrupt)指CPU停止当前程序的执行转而去执行新的突发情况的程序的过程。6678提供了大量来自内核或芯片级(如片上外设)的系统事件,这些事件通过中断控制器路由到合适的DSP中断或者异常,同时也可以用这些事件来驱动外设,比如EDMA。6678的中断可以分为两个层次,一层为每个核都有的内核中断,一类为芯片级中断,芯片级中断可通过配置路由到可以响应的内核。

1.内核中断控制器INTC

1.1 INTC的功能结构

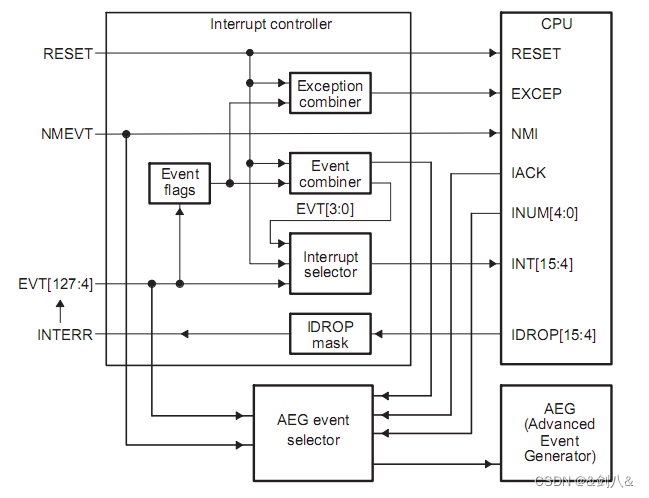

6678的中断的核心为C66X CorePac Interrupt Controller(INTC中断控制器),中断控制器的输入为多达128种事件,这128种事件包含了内核事件和芯片级事件,除了这128个事件还有直接路由到DSP的不可屏蔽中断和复位事件。

以上输入事件、复位或异常通过中断控制器组合路由等处理后输出到内核。输出包括以下内容:

- 1个可屏蔽的硬件异常(EXCEP)。

- 12个可屏蔽的硬件中断(INT4-INT15)。

- 1个不可屏蔽的信号,可作为中断或者异常(NMI)。

- 1个复位信号(RESET)。

中断控制器的结构如图1所示。

图1 中断控制器结构图

图1输入事件可以经过哪些处理输出到CPU,从左侧向右侧看,RESET信号既可以直接连接到CPU(INT0),又可以通过中断选择器路由到INT[15:4];NMEVT非可屏蔽事件,可以作为中断信号直连到CPU,也可以作为事件输入到AEG模块;EVT[127:4]一方面可以通过中断选择器路由到CPU,一方面可以通过事件组合器输出EVT0-EVT3或异常组合器路由到CPU;INTERR为CPU检测到中断丢失(drop)时产生的一个系统事件(EVT96),该中断异常事件发生时提醒开发者不能被打断的程序太长了,影响了中断的响应或者中断在一个较长的时间内被屏蔽响应了。

1.2内核中断控制器INTC

C66x CorePac interrupt controller(INTC)控制了中断事件的组合、选择、路由等,主要分为事件寄存器、事件组合寄存器、中断选择寄存器、异常控制寄存器。

1.2.1事件寄存器

事件寄存器包括事件标志寄存器(EVTFLAGx)、清事件寄存器(EVENTCLRx)、设置事件设置寄存器(EVTSETx)。以上寄存器每一个都有4组32位寄存器。分别从低位到高位对应EVT0-EVT127。其中EVT4-EVT127为原始事件,EVT0-EVT3为由原生事件组合生成的事件。这三个寄存器的上电复位值为0。

事件标志寄存器一共可以捕获124个系统事件,每一位对应一个中断事件,硬件中已经分配好(详见手册),当事件触发时,对应的位为1。注意的是EVENTFLAG0的bit0-bit3和其他输入系统事件没有直接的一对一映射关系,它们的输入由事件组合模块产生,映射到Interrupt Selector。

事件清除寄存器控制124个系统事件的清除,每一位和事件标志寄存器对应。EVTFLAGx寄存器为只读寄存器,只能通过EVENTCLRx对应的位写1来清除。

If a new event is received during the same cycle, a clear is specified via an EVTCLRx

register, the new event input takes precedence as an additional precaution against

missing events.

通过写事件寄存器EVTSETx的某一位为1,可以触发相应的中断事件,也就是说这些这些事件的触发除了硬件捕获外,也可以通过软件编程的方式实现。

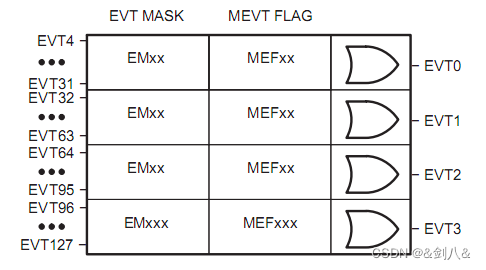

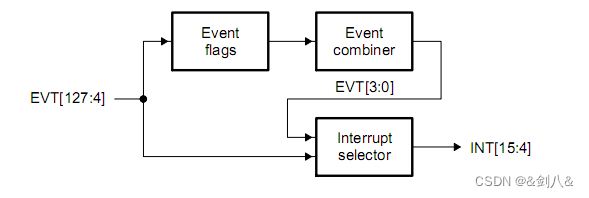

事件组合寄存器允许多个事件组合成一个事件。将EVT4-EVT127分成四组(EVT4-EVT32,EVT32-EVT63,EVT64-EVT95,EVT96-EVT127),并通过EVT MASK和MEVTFLAG组合生成新的四个事件EVT0-EVT3,在同一个组内的事件才可以组合,并映射到如图1-2所表示的事件。组合在一起的事件具有逻辑或的关系。124个原始的事件和4个组合事件组成了输入中断选择寄存器的128个事件。

图2 组合事件的分组关系

Event Mask Register(EVT MASK)事件屏蔽寄存器,上电默认值为0,即默认组内所有事件组合在一起,某事件对应的位置1则该事件被禁止参与组合。注意的是bit0-bit3是保留的位,这三位对应EVT0-EVT3,不作为组合事件的输入,作为组合事件的输出。

Masked Event Flag Register(MEVT FLAG)屏蔽事件标志寄存器,该寄存器的值和事件标志寄存器的值相同(事件屏蔽寄存器使能的位)。上电默认值为0。

如:

EVTFLAG3 = 01101010010011001110001110010101

EVTMASK3 = 00001111111111111111111111111111

则:

MEVTFLAG3 = 01100000000000000000000000000000实际读出的值,位为1的事件是即将通过组合事件发送到DSP的事件。

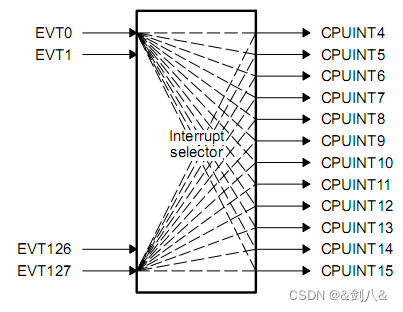

1.2.2中断选择器(Interrupt Selector)

DSP有12个可屏蔽中断(INT4-INT15),它允许128个系统事件(124个原生事件和4个组合事件)路由到12个可屏蔽中断中的任何一个,如图3和4所示。

图3 中断选择框图

图4 中断路由框图

Interrupt Mux Registers中断复用寄存器(INTMUXn),中断选择器由3个中断复用寄存器组成,用户可以通过软件编程为12个可屏蔽中断选择中断事件源。该寄存器共有3组,上电复位值为0。

表1 INTMUX1

| Bit 位 | Field 域 | Description 说明 |

| Reserved | 31 | 保留 |

| INTSEL7 | 24-30 | 映射到中断INTn的事件号 |

| Reserved | 23 | 保留 |

| INTSEL6 | 16-22 | 映射到中断INTn的事件号 |

| Reserved | 15 | 保留 |

| INTSEL5 | 8-14 | 映射到中断INTn的事件号 |

| Reserved | 7 | 保留 |

| INTSEL4 | 0-6 | 映射到中断INTn的事件号 |

表2 INTMUX2

| Bit 位 | Field 域 | Description 说明 |

| Reserved | 31 | 保留 |

| INTSEL11 | 24-30 | 映射到中断INTn的事件号 |

| Reserved | 23 | 保留 |

| INTSEL10 | 16-22 | 映射到中断INTn的事件号 |

| Reserved | 15 | 保留 |

| INTSEL9 | 8-14 | 映射到中断INTn的事件号 |

| Reserved | 7 | 保留 |

| INTSEL8 | 0-6 | 映射到中断INTn的事件号 |

表3 INTMUX3

| Bit 位 | Field 域 | Description 说明 |

| Reserved | 31 | 保留 |

| INTSEL16 | 24-30 | 映射到中断INTn的事件号 |

| Reserved | 23 | 保留 |

| INTSEL14 | 16-22 | 映射到中断INTn的事件号 |

| Reserved | 15 | 保留 |

| INTSEL13 | 8-14 | 映射到中断INTn的事件号 |

| Reserved | 7 | 保留 |

| INTSEL12 | 0-6 | 映射到中断INTn的事件号 |

1.2.3中断事件

中断事件的编号在CPU中已经做出了规定,如表4所示。

表4 INTMUX3

1.2.4 中断控制器

IER: 全局中断使能,控制INT0-INT15的使能。

ITSR:

GIE:

2.片级中断控制器CIC

2.1 INTC的功能结构

KeyStone架构中有大量的外设和中断源,虽然EDMA3和C66x CorePark可以直接接收事件,但是数量有限制。因此需要根据具体的应用通过软件配置将这些事件聚合到一起再发送给EDMA3或者C66x CorePark。

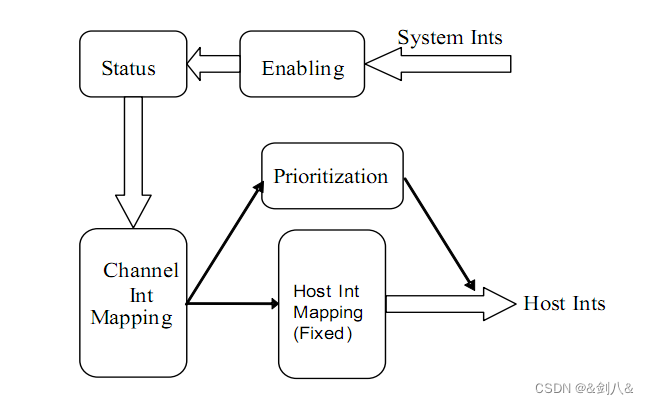

CIC模块控制系统级中断映射到主机中断(主机中断的部分事件包含了系统中断的通道映射的输出),系统中断由外设产生后,CIC接收接收到系统中断,然后映射到内部通道,这些通道将系统中断分组映射到数量更少的主机中断。通道和主机中断之间的映射是固定的一对一映射关系。

外设产生的中断称为外设中断,外设中断被扩展或同步到系统使用称为系统中断。系统中断被中断控制器使用,通常为脉冲中断,在一个单周期内被挂起。系统中断可以被单核或者多核共享。CIC完成使能、状态、通道映射(可编程)、主机中断映射(固定)、优先级设定几个功能来实现对系统中断的处理。如图所示。

(1)使能

芯片通过编程CIC中断使能寄存器控制哪些中断被禁止或者使能。

(2)中断状态

CIC通过中断状态寄存器捕获识别哪些系统中断被挂起,状态寄存器可以被独立清除。

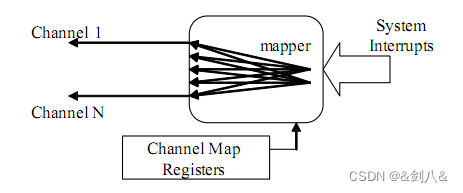

(3)通道映射

系统中断作为输入可以通过通道映射寄存器分配到256个中断通道中,通过组合达到减小路由到主机中断的中断数量的效果,它们是或的关系,通道中任何一个中断被激活,输出也会被激活。

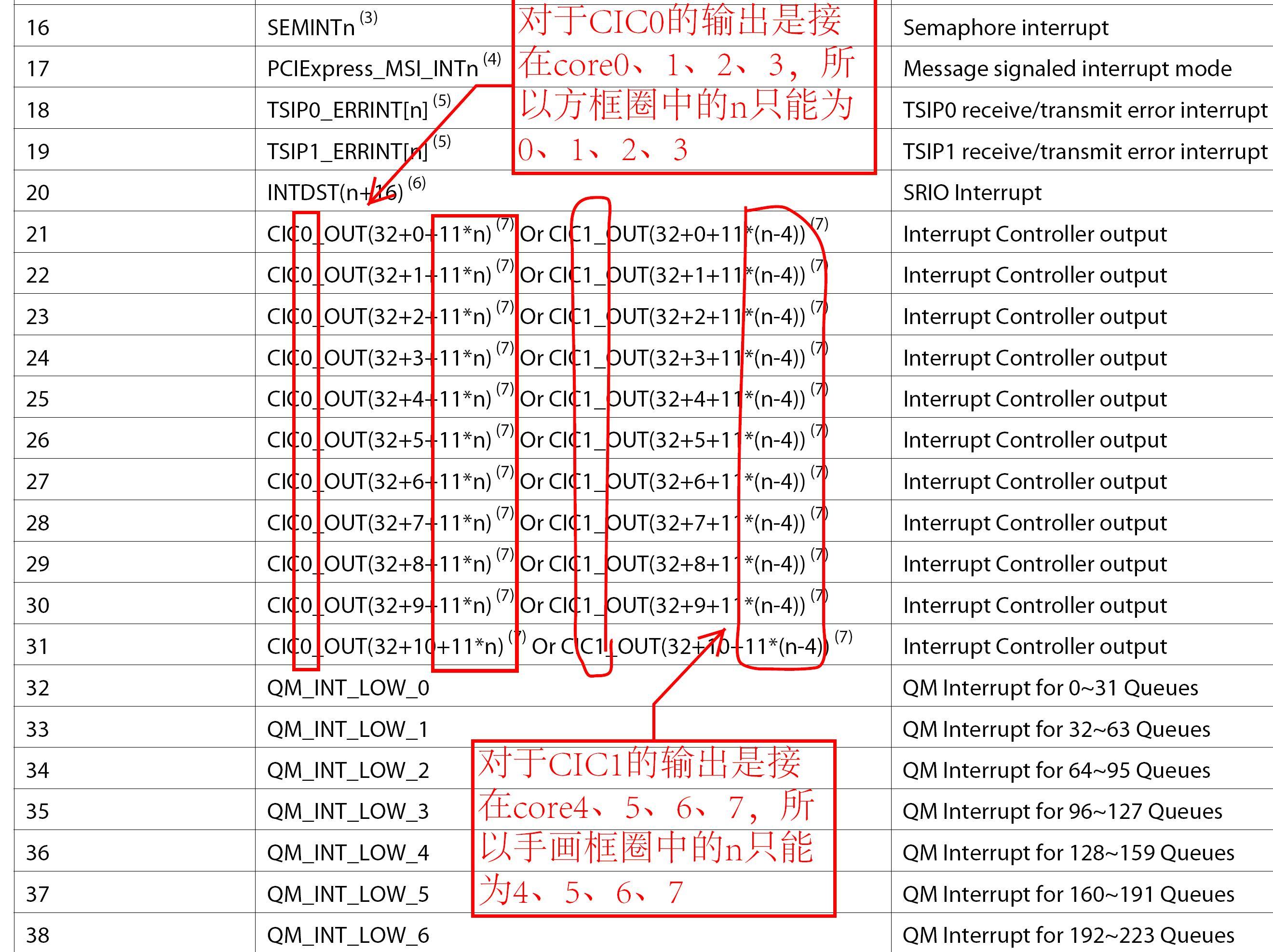

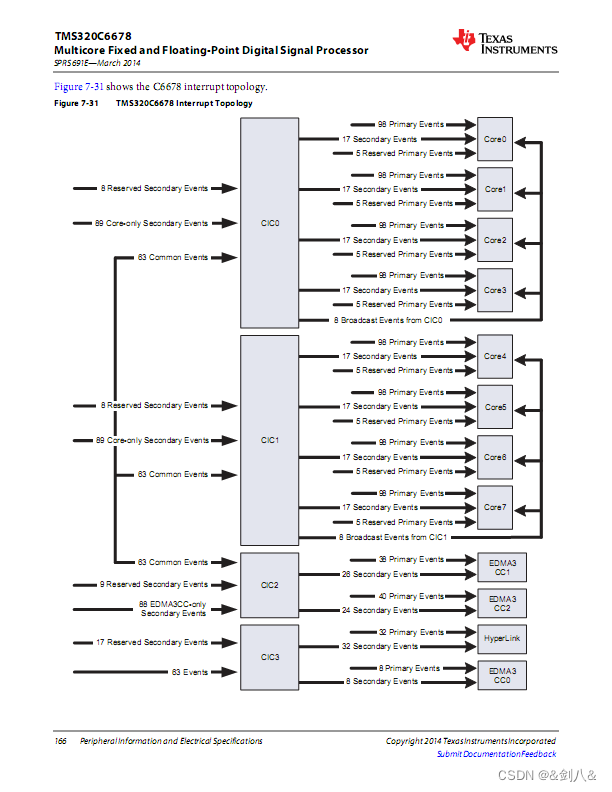

对于C6678的CIC可以管控的中断一共最多可以有1024个,管控方式是可以将每个中断通过配置,映射至256个channel中的某一个,一个channel上可以同时映射多个中断,映射至同一个channel的中断,相互之间就是逻辑“或”的关系了,即如果其中任何一个中断产生,该channel均会上报中断;system events至channel映射完了之后,还不能完成中断的上报,还需要把这256个channel映射至host interrupt,host interrupt的数量最大也是256个。这个host interrupt的编号和CICx_OUTn是一一对应的,但是整个对应关系并不是从CIC0开始按序号一边编到最后的CICx,而是CIC分多个,每个CIC的OUT都是从OUT0开始编号。实际上CICx_OUTn到corepac的intc的输入,是定死的,如下图:

比如21行中的CIC0_OUT,对于core0来说,core0的intc的system event21接的就是CIC0_OUT(32 + 0 + 11 * 0),即CIC0_OUT32,这个CIC0_OUT32是不可能让其他core来接管的;同样,对于core1来说,core1 intc的system event21接的就是CIC0_OUT(32 + 0 + 11 * 1),即CIC0_OUT43,这个CIC0_OUT43同样也只能由core1接管,不可能让其他core来接管CIC0_OUT43。其他类推。

对于从CIC的输入,到最后core,有3个环节决定CIC的输入最终由哪个core来处理,这3个环节分别是:

1、 system interrupt到channel的map

2、 channel到host interrupt的map

3、 host interrupt到corepac intc的连接

3862

3862

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?