一、使用存储控制器访问外设的原理

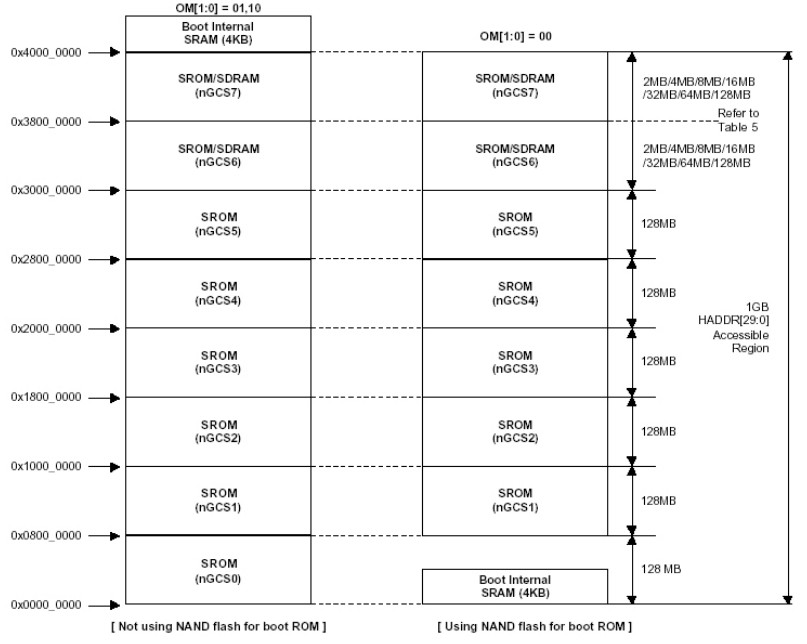

1、S3C2440的地址空间

S3C2440对外引出27根地址线ADDR0-ADDR26,访问范围只有128MB,CPU对外还引出8根片选信号nGCS0-nGCS7,对应BANK0-BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平来选中外接设备。

这样每个128MB空间,共8个片选,对应1GB的地址空间。空间分布图如下:

左边是nGCS0片选的nor flash启动模式下的存储分配图,右边是nand flash启动模式下的存储分配图

S3C2440是32位CPU,可以使用的地址范围理论达到4GB,除去上面连接外设的1GB空间外,还有一部分是CPU内部寄存器的地址,剩下的地址空间没有使用。

2、存储控制器与外设的关系

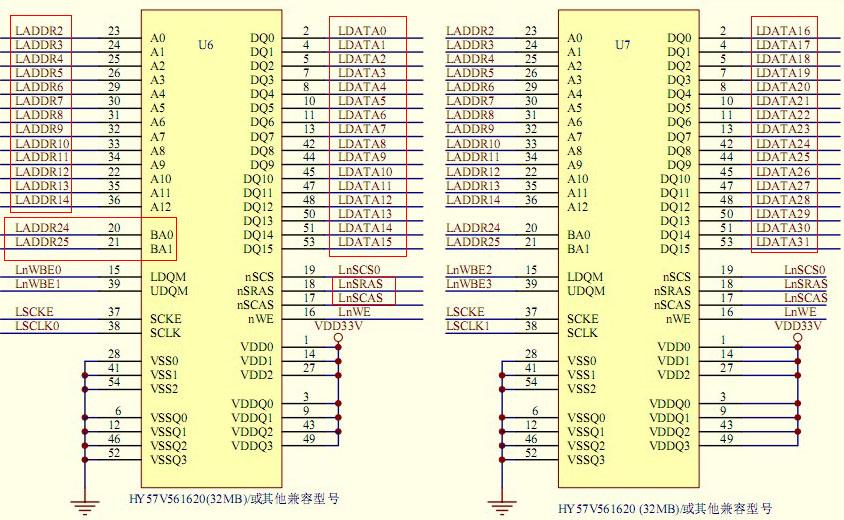

BANK0-BANK5的连接方式类似,BANK6连接SDRAM时复杂一些,SDRAM内部是一个存储阵列,指定一个行,再指定一个列,就可以准确找到所需要的单元格,而SDRAM有4个逻辑表格(L-BANK),下面图为一张L-BANK

那么SDRAM的访问步骤为:

1)CPU发出片选信号nSCS0(与nGCS6是同一引脚)有效,选中SDRAM芯片

2)SDRAM有4个L-BANK,需要两个地址信号来选中其中一个,即ADDR24、ADDR25,如下图

3)对被选中的芯片进行同一的行/列(存储单元)寻址

根据SDRAM芯片的列地址线数目设置CPU相关寄存器后,CPU会从32位地址中自动分出L-BANK选择信号、行地址信号、列地址信号,然后先后发出行地址信号、列地址信号。L-BANK选择信号在发出行地址信号的同时发出,并维持到列地址信号结束

如上图:行地址、列地址公用地址线ADDR2-ADDR14,使用nSRAS(R=Row)、nSCAS(C=Column)两个信号来区分它们,当nSRAS信号有效时,ADDR2-ADDR14发出的是行地址,对应地址空间bit[23:11],当nSCAS信号有效时,ADDR2-ADDR14发出的是列地址,对应地址空间bit[10:2]。

4)找到存储单元后,被选中的芯片就要进行统一的数据传输。

开发板使用两片16bit的SDRAM芯片并联形成32位的位宽,与CPU的32根数据线DATA0-DATA31相连,BANK6的起始地址位0x30000000

3、存储控制器的寄存器使用方法

存储控制器共有13个寄存器,BANK0-BANK5只需要设置BWSCON和BANKCONx两个寄存器,BANK6、BANK7外接SDRAM时,还要设置REFRESH,BANKSIZE,MRSRB6,MRSRB7,等4个寄存器,下面分别说明

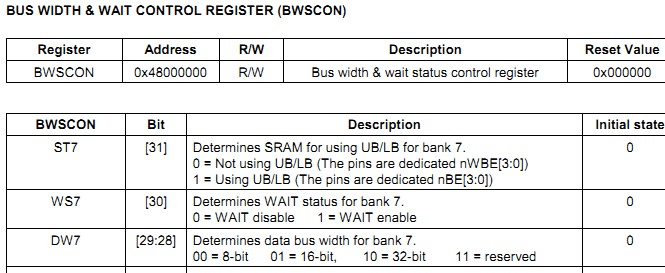

1)位宽和等待控制寄存器BWSCON

BWSCON中每四位控制一个BANK,最高4位对应BANK7、接下来4位对应BANK6,依次类推,如下图

STx:启动/禁止SDRAM的数据掩码引脚

WSx:是否使用存储器的WAIT信号

DWx:设置对应BANK的位宽,0b00对应8位,0b01对应16位,0b10对应32位,0b11表示保留

比较特殊的是BANK0,它没事ST0和WS0,DW0只读,由硬件跳线决定,0b01表示16位,0b10表示32位,BANK0只支持16、32两种位宽

所以可以确定BWSCON寄存器值为:0x22011110

2)BANK控制寄存器BANKCONx(x为0-5)

这些寄存器用来控制BANK0-BANK5外接设备的访问时序,使用默认0x0700即可

3)BANK控制寄存器BANKCONx(x为6-7)

MT[16:15]:设置BANK外接ROM/SRAM还是SDRAM,00=ROM/SRAM,01=保留,10=保留,11=SDRAM

MT=0b00时,与BANKCON0-BANKCON5类似

MT=0b11时,

Trcd[3:2]:RAS to CAS delay,设为推荐值0b01

SCAN[1:0]:SDRAM的列地址数,本开发板使用的SDRAM列地址数为9,0b00=8位,0b01=9位,0b10=10位

所以本开发板,BANKCON6/7均设为0x00018005

4)刷新控制寄存器REFRESH

REFEN[23]: 0=禁止SDRAM的刷新功能,1=开启SDRAM的刷新功能

TREFMD[22]: SDRAM的刷新模式,0=CBR/Auto Refresh,1=SelfRefresh

Trp[21:20]: SDRAM RAS预充电时间 00=2 clocks,01=3clocks,10=4clocks,11=不支持

Tsrc[19:18]: SDRAM半行周期时间 00=4clocks,01=5clocks,10=6clocks,11=7clocks,SDRAM行周期时间Trc=Tsrc+Trp

Refresh Counter[10:0]: SDRAM刷新计数,刷新时间=(2^11+1-refresh_count)/HCLK,在未使用PLL时,HCLK=晶振频率12MHz,刷新周期为7.8125us

refresh_count=2^11+1-12*7.8125=1955

REFRESH=0x008C0000+1955=0x008C07A3

5)BANKSIZE寄存器

BURST_EN[7]: 0=ARM核禁止突发传输,1=ARM核支持突发传输

SCKE_EN[5]: 0=不使用SCKE信号令SDRAM进入省电模式,1=使用SCKE信号令SDRAM进入省电模式

SCLK_EN[4]: 0=时刻发出SCLK信号,1=仅在方位SDRAM期间发出SCLK信号

BK76MAP[2:0]: 设置BANK6/7的大小,0b010=128MB/128MB,0b001=64MB/64MB,0b000=32M/32M,0b111=16M/16M,0b110=8M/8M,0b101=4M/4M,0b100=2M/2M

本开发板外接64MB的SDRAM

则本开发板BANKSIZE设为0xB1

6)SDRAM模式设置寄存器MRSRBx(x为6-7)

CL[6:4]: 0b000=1clocks,0b010=2clocks,0b011=3clocks

本开发板取0b011,所以MRSRB6/7取值为0x30

二、存储控制器操作实例:使用SDRAM

从NAND Flash启动CPU时,CPU会通过内部的硬件将NAND Flash开始的4KB数据复制到成为"Steppingstone"的4KB的内部RAM(起始地址为0)中,然后跳到地址0开始执行。

本程序先设置好存储控制器,使外接的SDRAM可用,然后把程序本身从steppingstone复制到SDRAM中,最后跳到SDRAM中执行

head.S:

1. @*************************************************************************

2.

3. @ File:head.S

4.

5. @ 功能:设置SDRAM,将程序复制到SDRAM,然后跳到SDRAM继续执行

6.

7. @*************************************************************************

8.

9.

10. .equ MEM_CTL_BASE, 0x48000000 @存储控制器寄存器基址

11. .equ SDRAM_BASE, 0x30000000 @SDRAM起始地址

12.

13. .text

14. .global _start

15.

16. _start:

17.

18. bl disable_watch_dog @ 关闭WATCHDOG,否则CPU会不断重启

19.

20. bl memsetup @ 设置存储控制器

21.

22. bl copy_steppingstone_to_sdram @ 复制代码到SDRAM中

23.

24. ldr pc, =on_sdram @ 跳到SDRAM中继续执行

25.

26. on_sdram:

27.

28. ldr sp, =0x34000000 @ 设置堆栈

29.

30. bl main

31.

32. halt_loop:

33.

34. b halt_loop

35.

36. disable_watch_dog:

37.

38. @ 往WATCHDOG寄存器写0即可

39.

40. mov r1, #0x53000000

41.

42. mov r2, #0x0

43.

44. str r2, [r1]

45.

46. mov pc, lr @ 返回

47.

48.

49. copy_steppingstone_to_sdram:

50.

51. @ 将Steppingstone的4K数据全部复制到SDRAM中去

52.

53. @ Steppingstone起始地址为0x00000000,SDRAM中起始地址为0x30000000

54.

55.

56. mov r1, #0

57.

58. ldr r2, =SDRAM_BASE

59.

60. mov r3, #4*1024

61.

62. 1:

63.

64. ldr r4, [r1],#4 @ 从Steppingstone读取4字节的数据,并让源地址加4

65.

66. str r4, [r2],#4 @ 将此4字节的数据复制到SDRAM中,并让目地地址加4

67.

68. cmp r1, r3 @ 判断是否完成:源地址等于Steppingstone的未地址?

69.

70. bne 1b @ 若没有复制完,继续

71.

72. mov pc, lr @ 返回

73.

74.

75. memsetup:

76.

77. @ 设置存储控制器以便使用SDRAM等外设

78.

79.

80. mov r1, #MEM_CTL_BASE @ 存储控制器的13个寄存器的开始地址

81.

82. adrl r2, mem_cfg_val @ 这13个值的起始存储地址

83.

84. add r3, r1, #52 @ 13*4 = 54

85.

86. 1:

87.

88. ldr r4, [r2], #4 @ 读取设置值,并让r2加4

89.

90. str r4, [r1], #4 @ 将此值写入存储控制寄存器,并让r1加4

91.

92. cmp r1, r3 @ 判断是否设置完所有13个寄存器

93.

94. bne 1b @ 若没有写成,继续

95.

96. mov pc, lr @ 返回

97.

98.

99.

100. .align 4

101.

102. mem_cfg_val:

103.

104. @ 存储控制器13个寄存器的设置值

105.

106. .long 0x22011110 @ BWSCON

107.

108. .long 0x00000700 @ BANKCON0

109.

110. .long 0x00000700 @ BANKCON1

111.

112. .long 0x00000700 @ BANKCON2

113.

114. .long 0x00000700 @ BANKCON3

115.

116. .long 0x00000700 @ BANKCON4

117.

118. .long 0x00000700 @ BANKCON5

119.

120. .long 0x00018005 @ BANKCON6

121.

122. .long 0x00018005 @ BANKCON7

123.

124. .long 0x008C07A3 @ REFRESH

125.

126. .long 0x000000B1 @ BANKSIZE

127.

128. .long 0x00000030 @ MRSRB6

129.

130. .long 0x00000030 @ MRSRB7 leds.c

1. #define GPBCON (*(volatile unsigned long *)0x56000010)

2. #define GPBDAT (*(volatile unsigned long *)0x56000014)

3.

4.

5. #define GPB5_out (1<<(5*2))

6. #define GPB6_out (1<<(6*2))

7. #define GPB7_out (1<<(7*2))

8. #define GPB8_out (1<<(8*2))

9.

10. void wait(unsigned long dly)

11. {

12.

13. for(; dly > 0; dly--);

14.

15. }

16.

17. int main(void)

18. {

19.

20. unsigned long i = 0;

21.

22. GPBCON = GPB5_out|GPB6_out|GPB7_out|GPB8_out; // 将LED1-4对应的GPB5/6/7/8四个引脚设为输出

23.

24. while(1){

25.

26. wait(30000);

27.

28. GPBDAT = (~(i<<5)); // 根据i的值,点亮LED1-4,实现流水灯

29.

30. if(++i == 16)

31.

32. i = 0;

33.

34. }

35. return 0;

36.

37. } 最后是Makefile

sdram.bin : head.S leds.c

arm-linux-gcc -c -o head.o head.S

arm-linux-gcc -c -o leds.o leds.c

arm-linux-ld -Ttext 0x30000000 head.o leds.o -o sdram_elf

arm-linux-objcopy -O binary -S sdram_elf sdram.bin

arm-linux-objdump -D -m arm sdram_elf > sdram.dis

clean:

rm -f sdram.dis sdram.bin sdram_elf *.o

分别汇编head.S和leds.c

连接leds.o和head.o,指定代码段起始地址0x30000000(SDRAM首地址)

最后转换ELF为二进制,导出汇编代码

2245

2245

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?