目的

刚好有需要用到H743的这方面内容,截取核心内容,翻译看看。

参考文档

【ST官方】H743 参考手册-英文版V7.0【中文版的尚未更新ECC内存相关内容,建议直接看英文的】

【ST官方】H743 ECC内存管理应用手册[编号AN5342]

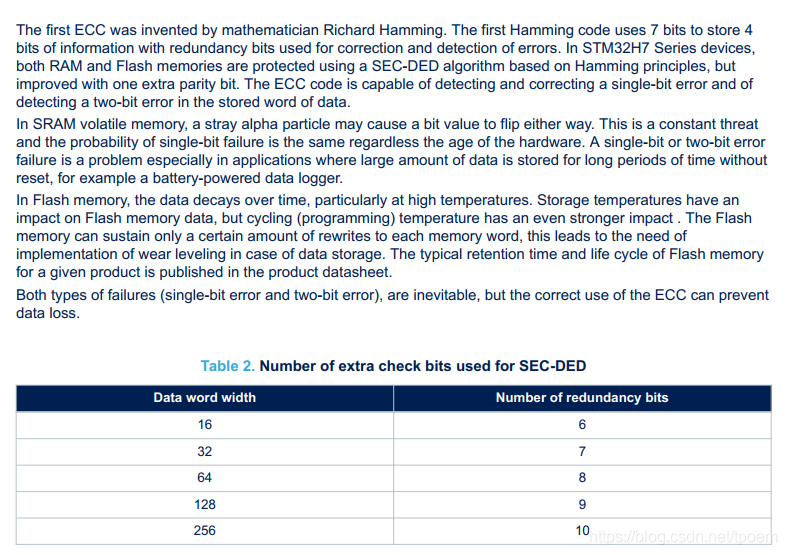

H7系列的芯片都是支持ECC【内存纠错】的,算法是SEC-DED

啥是ECC内存请自行百度~

支持情况汇总

数据来自ST的AN5342

原文如下:

| CPU系列 | 支持情况 |

|---|---|

| H7X5 H7X7 | SRAM,I/D Cache都支持ECC保护,数据宽度为64Bits(AXI-SRAM和ITCM RAM),其他所有易失性内存都是按32位宽度进行访问的。最小Flash编程单位是256位,被10位的ECC纠错码保护.该系列没有OTP内存区,所以就没有对应内存区的ECC防护 |

| H7X3 | 仅有紧密耦合内存和I/D Cache支持ECC保护,其他不支持,最小Flash编程单位是128位,被9位的ECC纠错码保护。1K字节的OTP内存区中,每16字节被6位的ECC纠错码防护 |

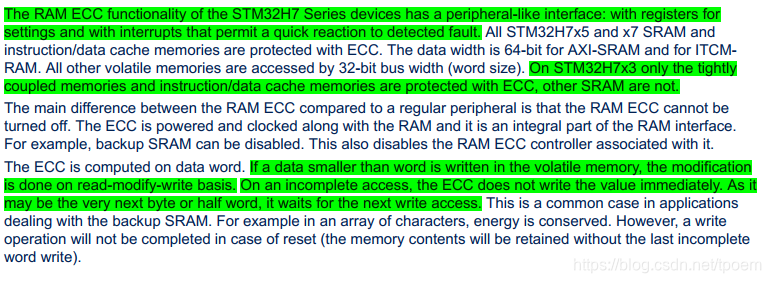

SRAM的ECC防护

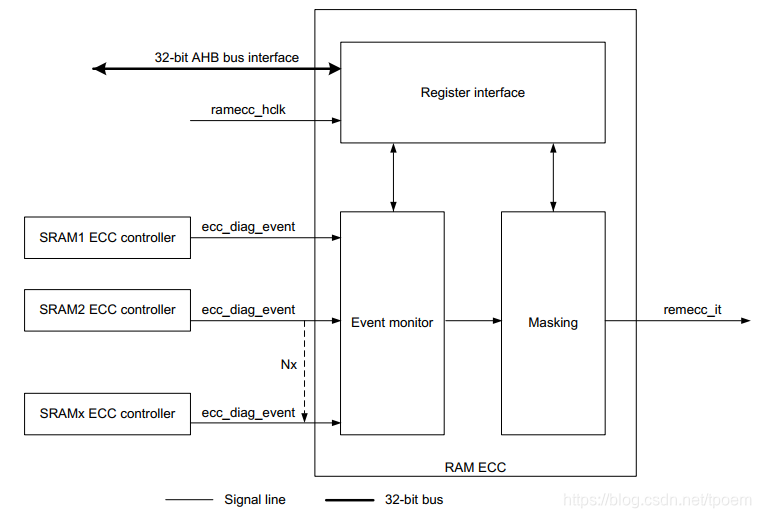

ST给RAM的ECC防护提供了一个接口【就是一些寄存器和一个ECC_IRQHandler中断】。RAM的ECC功能是不能被关闭的,它作为内存接口的一部分随电源上电,时钟起作用而启动

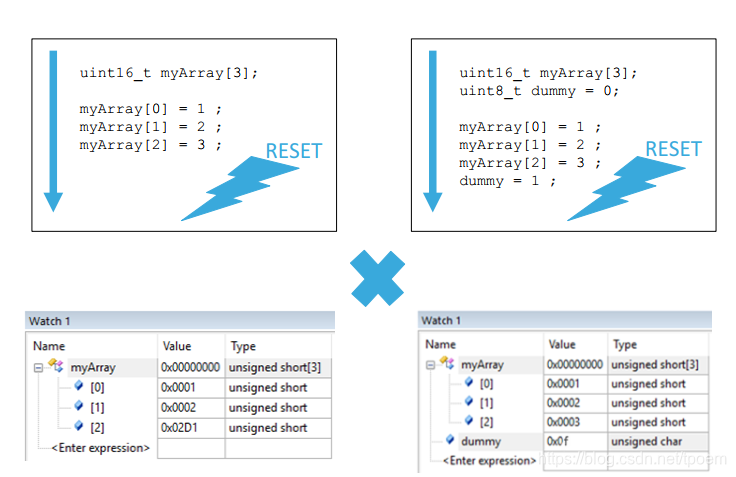

ECC是按字计算的.如果在易失性存储器中写入了小于字的数据,则修改是在读-修改-写的基础上进行的.对于没有完成的访问,ECC不会立即把值写进去.因为这有可能是下一个字节或半字,它会等待到下一个写周期.这个问题在用备份SRAM是很常见的.譬如突然复位,导致写操作没有完成.这种情况下,需要在正常的数据之后写一个dummy值,也就是占位值.这个占位值的写地址必须紧跟着数据,在同一段内存区域里。【以上为我对原文的翻译,仅供参考】

结合图片,大意感觉就是如果数据不对齐,在某些特殊情况【复位】下,写操作会异常,之后读出来的值会不对,需要人为的补上一些写操作,达到数据对齐的目的。

针对每一个内存块,ECC控制器是提供单独的事件控制,但是输出给用户是一个全局的中断。

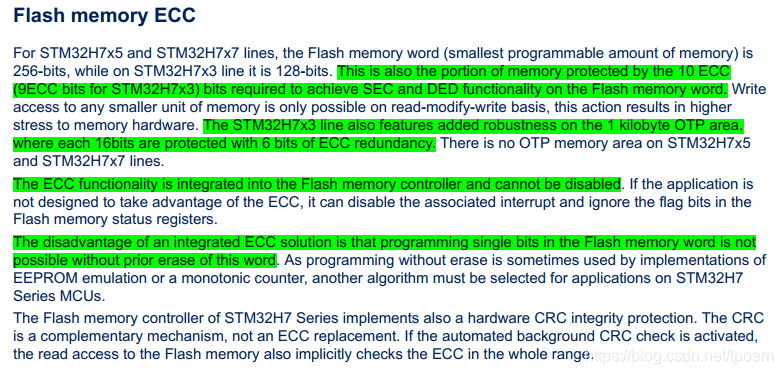

Flash的ECC防护

同样针对Flash的ECC也是不能关闭的。如果不希望使用,只能不理这个ECC中断和相关标志。ECC的缺点就是当希望把Flash当作EEPROM来用的时候,必须要先擦除后写入。否则需要额外的烧写算法。

另外H7本身有硬件CRC固件保护,这个与ECC互为补充,如果使能了CRC固件校验,那么对Flash 进行读操作的时候,其实隐含的也对整个Flash进行了ECC校验。

Cache的ECC防护

直接说结论了,M7内核在检测到任何指令Cache错误后自动恢复,1位错误能自动纠错并恢复。对两位错误,流水线无效,指令被重新从程序存储区取出。对于数据Cache,两位错误可能会导致在读取旧数据的时候,当前修改的结果丢失。由于没有通知的Cache ECC错误的机制,唯一的解决方法是定时去清理Cache或者干脆不用Cache。

ECC纠错的应用实现

SRAM

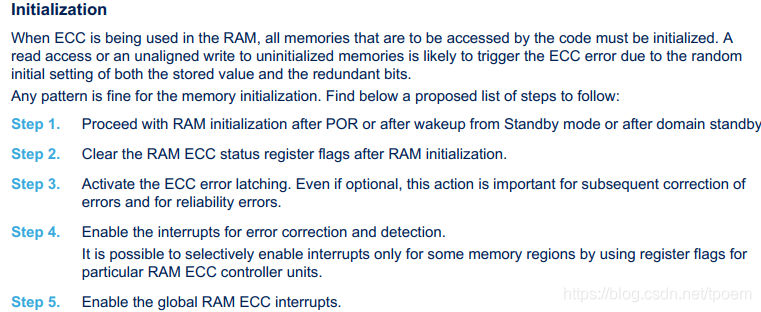

ST提供了ECC初始化5步骤【简单说】

- 正常初始化内存并上电

- 之后清除RAM ECC的状态标志位

- 激活ECC错误锁存

- 开启需要的内存区的ECC中断使能

- 开启全局ECC中断

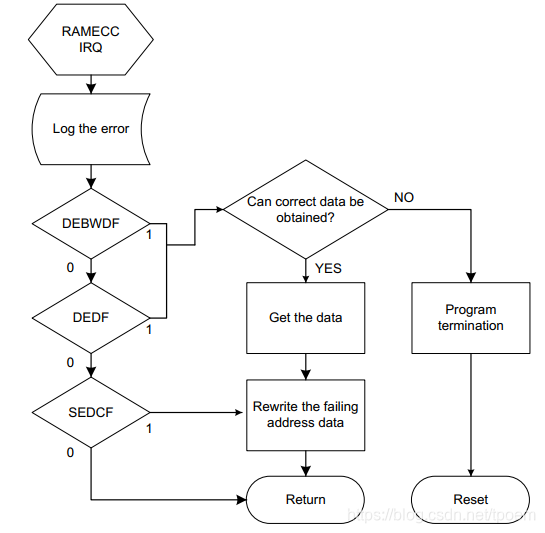

ECC错误中断提供了一个立即响应ECC错误的机会。1位错误自动被ECC控制器纠正,但仅限于数据读取。2位错误的处理要看具体情况

如果发生在装入内存的指令代码区,那么对应的代码要找出来,代码重新装入SRAM中。

如果发生在堆栈区,建议系统重启,以免造成更严重的系统损害。

RAM ECC中断的中断控制流程

如何防范

周期性的读检查,周期可以长些,具体看需求,可以放在空闲任务或者低优先级的DMA传输,但是由于内存区的不连续性,这样的方法也不是特别的好。可以试试MDMA,因为它可以访问I/DTCM,通过M7内核的I/DTCM去读SRAM,可以变相的实现ECC校验的目的,这样对CPU的负担小,对总线的压力大。

Flash

对Flash而言,其ECC错误是通过Flash中断上报的,具体寄存器看手册

这一章其他的内容,我这就不翻译了,暂时没有涉及。

ECC功能涉及到的内容对应于H743手册中的位置

6342

6342

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?