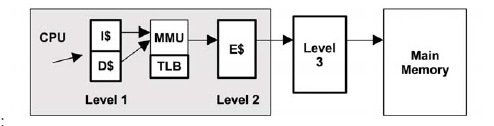

一,cpu缓存架构

1.level-1 data cache: 一级数据缓存

2.level-1 inst cache: 一级指令缓存

3.MMU: 内存管理单元

4.TLB(translation lookaside buffer): 转换后援缓存

5.level-2 cache:二级缓存

6.level-3 cache:三级缓存

二.处理器读取数据过程

- CPU根据虚拟地址尝试从一级缓存(存放的是虚拟地址的索引)中读取数据;

- 如果一级缓存中查找不到,则需向MMU请求数据;

- MMU从TLB中查找虚拟地址的缓存(换言之,

TLB是负责改进虚拟地址到物理地址转换速度、存放虚拟地址的缓存); - 如果TLB中存在该虚拟地址的缓存,则MMU将该虚拟地址转化为物理地址,如果地址转换失败,则发生缺页(图中的

fault分支),由内核进行处理,见上文所述;如果地址转换成功,则从二级缓存(存放的是物理地址的索引)中读取;如果二级缓存中也没有,则需要从三级缓存甚至物理内存中请求; - 如果TLB中不存在该虚拟地址的缓存,则MMU从物理内存中的转换表(

translation tables,也称为页表page tables)中获取,同时存入TLB;(注意,这个操作是硬件实现的,可以由MMU通过硬件直接从物理内存中读取); - 跳到第4步。

371

371

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?