我们现在有了一个新的寄存器,叫做指令寄存器。它包含一个字节,不同的内容表示控制部分的不同操作模式。也被称为指令代码。指令寄存器是一个字节,因此可能有多达256条不同的指令。所有指令都涉及在总线上移动字节。指令将导致字节进出RAM,进出寄存器,有时通过ALU。下面我们来认识一下计算机中简单的几种指令集吧。

算术逻辑指令

第一类指令时使用ALU的类型,像前面提到的ADD,NOT,SHL等8种类型,有的类型有两个字节的输入,有的类型有一个字节输出。所以ALU这类指令将选择一个ALU操作和两个寄存器。

指令代码有8个bit,当第一个bit是1时候,表示这是一条ALU指令,然后接下来三bit告诉选择ALU的哪个操作,接着两bit是选择的一个寄存器,在接着两bit是选择的另外一个寄存器。

因此如图,ALU指令(1)将(000)寄存器2(10)和寄存器3(11)相加,并将答案放入寄存器3,将是:1000 1011。布线如下:

上面是算术逻辑指令的代码,为了更好的记着这些CPU指令的含义,有这样一个速记发明,它被称为计算机语言,ALU指令产生的新语言的前八个单词是如下,当一个人想要编写一个计算机程序时,他可以直接在指令代码中编写,或者使用计算机语言。当然,如果你用计算机语言编写一个程序,它必须被翻译成实际的指令代码,然后才能放入RAM并执行。

加载与存储指令

加载和存储指令非常简单。它们在RAM和寄存器之间移动一个字节。

前面ALU指令是IR第一位打开,还有八种类型不是ALU指令,第一位关闭时候进入这八种类型指令,并使用IR的接下来三位来准确地告诉我们我们有哪种类型的命令。

本节介绍使用解码器前两个输出的指令,即IR以0000或0001开头时出现的指令。第一条指令将一个字节从RAM移动到寄存器,这称为“加载”指令。另一个则相反,它将一个字节从寄存器移动到RAM,称为“存储”指令。

Load指令的指令代码为0000,Store指令的指令码为0001。在这两种情况下,剩余的四位都指定了两个寄存器,就像ALU指令一样,但在这种情况下,一个寄存器将用于选择RAM中的一个位置,另一个寄存器则将从该RAM位置加载或存储到该RAM位置。

对于这两个指令,步骤4是相同的。其中一个寄存器由IR位4和5选择,并在总线上启用。然后将总线设置为MAR,从而在RAM中选择一个地址。

在步骤5中,IR位6和7选择另一个CPU寄存器。对于Load指令,RAM被启用到总线上,总线被设置到所选寄存器中。对于存储指令,所选寄存器被启用到总线上,总线被设置到RAM中。这些指令中的每一个只需要两个步骤就可以完成,第6步什么不做。

数据指令

数据指令所做的只是将一个字节从RAM加载到寄存器中,就像上面的load指令一样。但它的不同之处在于,它需要指令在RAM中的哪个位置获得该字节。

在Data指令中,数据来自下一条指令的位置。所以你可以考虑这个指令实际上有两个字节!第一个字节是指令,下一个字节是一些将被放入寄存器的数据。这个数据很容易找到,因为当我们在IR中有指令时,IAR已经更新了,所以它指向这个字节。

这是Data指令的指令代码。第0位至第3位为0010位。第4位和第5位未使用。第6位和第7位选择将加载第二字节数据的寄存器。

这条指令需要做的就是,在步骤4中,将IAR发送到MAR,在步骤5中,将RAM发送到所需的CPU寄存器。然而,还有一件事需要发生。由于指令的第二个字节只是可以是任何数据的数据,所以我们不希望将第二个字符作为指令执行。我们需要第二次向IAR添加1,以便它跳过这个字节并指向下一条指令。我们将以同样的方式在步骤1和3中执行。在步骤4中,当我们将IAR发送到MAR时,我们将利用ALU正在计算IAR加上一些东西的事实,同时我们将打开“总线1”,并将答案设置为ACC。步骤5仍然将数据移动到寄存器,在步骤6中,我们可以将ACC移动到IAR。

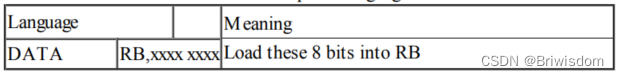

这是数据指令形成的计算机语言:

1190

1190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?