背景:没有数字电路专业背景的人,从0到1简单看懂时序图

时序图基本组成元素

时序图由方波组成,如下图,向上凸起的表示高电平,下凸起的部分表示低电平。两者状态之间通过斜线控制,表示在状态切换。

![]()

写优先模式时序图

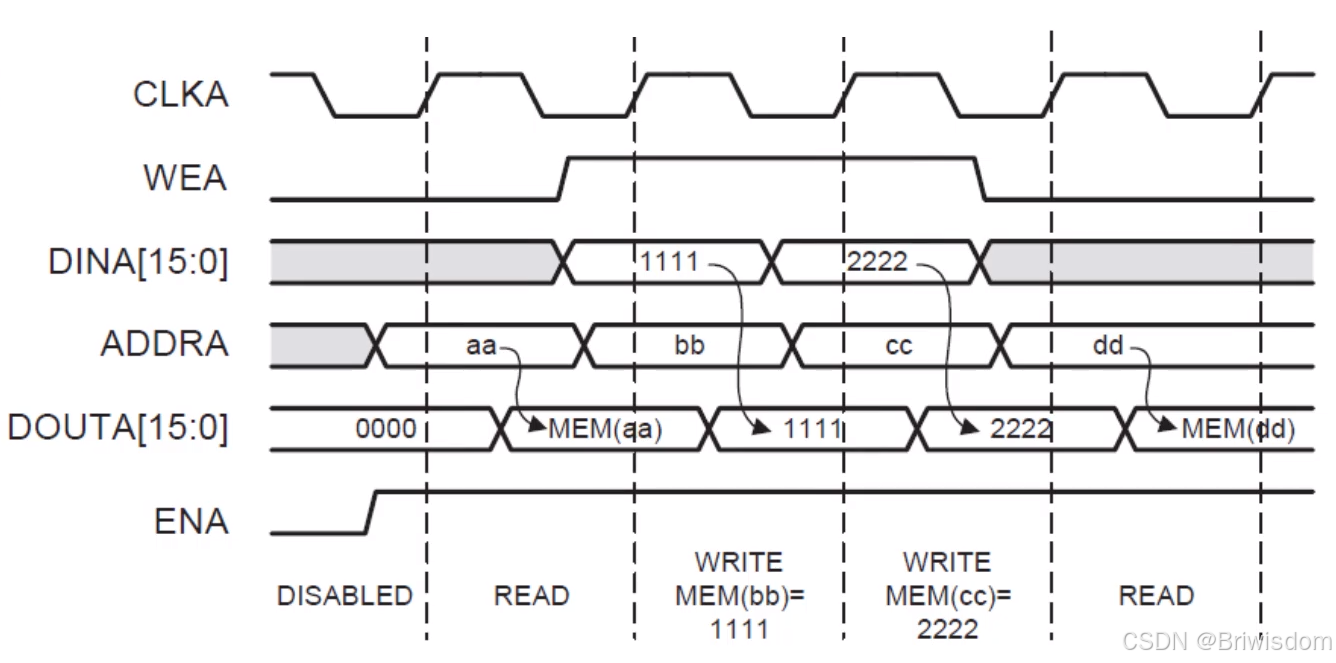

如下图示意,对一个写优先的时序图进行解读。

- CLKA表示时钟信号

- ENA:是全局控制总开关,使能信号

- WEA:是写控制开关,使能信号

- DINA: data in addr, 数据写入地址

- ADDRA: RAM内存地址

- DOUTA:data out addr,数据写出地址

图中虚线位置表示在全局开关使能条件下,一个时钟沿上升时候的系统状态。

当全局使能信号ENA =0 (即DISABLED)时候,数据写出总线没有操作。

当全局使能信号ENA=1时候,

- 第一条虚线,WEA=0,此时表示系统是读状态,从RAM地址aa读取数据到DOUTA总线;

- 第二条虚线,WEA=1,此时表示系统是写优先状态,先从DINA地址1111写数据到RAM的bb地址,并马上把写入数据传到DOUTA输出总线;

- 第三条虚线,WEA=1,同第二条虚线,先从DINA地址2222写数据到RAM的cc地址,并马上把写入数据传到DOUTA输出总线;

- 第四条虚线,WEA=0,同第一条虚线,RAM地址dd读取数据到DOUTA总线;

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?