1. I2C总线协议解析

1.1. 概述

IIC开发于1982年,当时是为了给电视机内的CPU和外围芯片提供更简易的互连方式。电视机是最早的嵌入式系统之一,而最初的嵌入系统是使用内存映射(memory-mapped I/O)的方式来互连微控制器和外围设备的。要实现内存映射,设备必须并行连入微控制器的数据线和地址线,这种方式在连接多个外设时需大量线路和额外地址解码芯片,很不方便并且成本高。

为了节省微控制器的引脚和和额外的逻辑芯片,使印刷电路板更简单,成本更低,位于荷兰的Philips实验室开发了IIC(Inter-Integrated Circuit),它是由数据线 SDA和时钟线SCL两根线构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送

IIC数据传输速率有标准模式(100 kbps)、快速模式(400 kbps)和高速模式(3.4 Mbps),另外一些变种实现了低速模式(10 kbps)和快速+模式(1 Mbps)

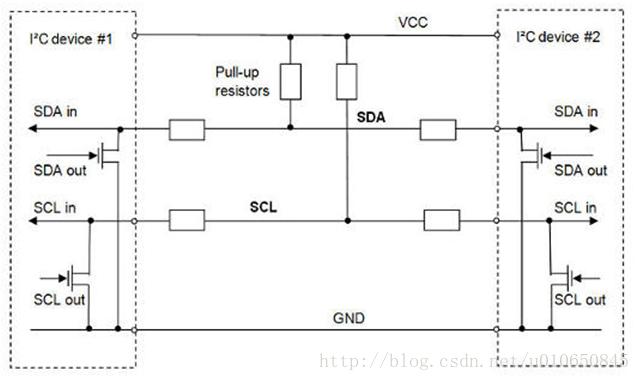

1.2. 硬件结构

每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器。这种电路具有两个特点:

- 由于 SDA、SCL 为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

- 引脚在输出信号的同时还能对引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟同步”和“总线仲裁”提供硬件基础。

1.3. 数据类型

IIC数据传输的过程中,数据帧的大小固定为8位的字节,高位先发送。

主控器向被控器发送的信息种类有:

启动信号、停止信号、7位地址码、读/写控制位、10位地址码(地址扩展)、数据字节、重启动信号、应答信号、时钟脉冲。被控器向主控器发送的信息种类有:

应答信号、数据字节、时钟低电平(时钟拉伸)。

1.3.1. 总线空闲状态

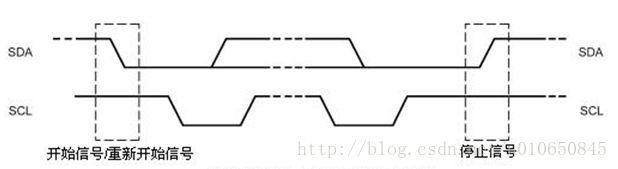

IIC总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

1.3.2. 启动信号

SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据

1.3.3. 结束信号

SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

1.3.4. 重新开始信号

在IIC总线上,由主机发送一个开始信号启动一次通信后,在首次发送停止信号之前,主机通过发送重新开始信号,可以转换与当前从机的通信模式,或是切换到与另一个从机通信。当SCL为高电平时,SDA由高电平向低电平跳变,产生重新开始信号,它的本质就是一个开始信号

1.3.5. 应答信号

II

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3771

3771

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?