一、Verilog HDL

Verilog HDL(Hardware Description Language)是一种设计硬件电路的语言,由IEEE完成了对其标准化的工作。 Verilog HDL总体来讲带有C语言的风格,是工业界常用的硬件描述语言。——《计算机原理与设计》,李亚民(全文引用的概念都出自此书,不多赘述)

个人感觉,Verilog HDL跟每一种编程语言一样,有自己独特的地方。Verilog HDL作为一种HDL,它语法风格很像C类语言,但是它更如同名字一样,偏重于去描述,而不是像C注重算法实现的过程或者是面向对象的抽象。这或许是因为它除了逻辑设计以外,还有时序设计,所以往往要比一般设计更加复杂,对设计者要求更加谨慎和细心。

二、CMOS

CMOS的全称是Complementary Metal Oxide Semiconductor,意味互补型金属氧化物半导体,由PMOS和NMOS两种晶体管“互补”构成

CMOS晶体管结合了PMOS和NMOS两种晶体管的优点,使得电路更易导通1和0两种状态,物理特性和规格标准这里不作讨论。

在CMOS级别上,我们可以搭建起常见的门级逻辑,如非门、与或门、异或门等。而在我们设计时,我们会经常忽略CMOS这一层级的考虑,因为越低的层级更加繁琐,而且当工程量大了以后,我们也很难顾虑了。用的晶体管的个数,可以在大致程度上衡量这个器件的功耗、面积,从而决定这个器件最后的好坏。

在Verilog HDL里,给出了这一级别设计的一些类型:

supply1 vdd; //高电平

supply0 gnd; //低电平

pmos p1(drain, source, gate);

nmos n1(drain, source, gate);

而在这个层级上定义了一些CMOS门,代码已经传上CSDNCode里,需要或有兴趣实现的可以参考这里

三、四种风格的Verilog HDL描述

1.晶体管开关级:也就是上述的CMOS级别描述;

2.逻辑门级:在CMOS上搭建的逻辑门,从而实现更高的设计;

3.数据流级:从这一级别开始,设计变得简易。数据流级强调和关注数据的流向、改变,使得信号数据有了连接关系,牵一发而动全身的姿态。

4.功能描述级:更接近自然语言的级别。

四、常用的组合电路

1.多路选择器

2.译码器

这里就不多赘述两者的概念和实现。这两个组合电路可以很简单地实现逻辑门(非、与、或等),从而组成组合电路。

五、时序电路

1.D锁存器

2.D触发器

3.状态机

同样,三者也不多赘述。

状态机是一个很重要的时序逻辑,可以很方便地解决我们一些实际问题,而我们的生活中处处都是一个个状态机,包括我们的投币机、电子防盗门系统等。如果有机会,将进一步学习。

六、实例:3输入CMOS与非门

在这里,以一个3输入CMOS的与非门作为实例。

实现代码:

<verilog HDL>

module cmosnand3 (ina,inb,inc,out);

input ina,inb,inc;

output out;

supply1 vdd;

supply0 gnd;

wire wn1,wn2;

pmos p1(out,vdd,ina);

pmos p2(out,vdd,inb);

pmos p3(out,vdd,inc);

nmos n1(out,wn1,ina);

nmos n2(wn1,wn2,inb);

nmos n3(wn2,gnd,inc);

endmodule

</verilog HDL>测试代码:

<verilog HDL>

`include "cmosnand3.v"

module cmosnand3_test;

reg ina,inb,inc;

wire out;

cmosnand3 c1(ina,inb,inc,out);

integer i;

initial begin

#0 ina = 0; inb = 0; inc = 0;

$display("\tina\tinb\tinc\tout");

for(i = 0; i < 9; i = i + 1)begin

#1 {ina,inb,inc} = i;

end

#1 $finish;

end

initial begin

$monitor("\t%b\t%b\t%b\t%b",ina,inb,inc,out);

$dumpfile("cmosnand3.vcd");

$dumpvars;

end

endmodule

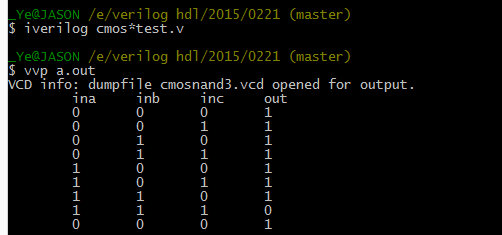

</verilog HDL>测试结果截图:

2125

2125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?