今天继续看看 IR 模块。

名词缩写

参考前面章节 TriCore:Interrupt 1

ICU

IR(Interrupt Router)中针对每一个SP(Service Provider,CPU or DMA)都有一个专门的ICU(Interrupt Control Unit)与之相连接。某个 SRN 模块可以通过设置其 SRC.TOS = x, 从而将自己映射到 ICUx模块,进而映射到 SPx。比如,SRC.TOS = 0, 则该中断就映射到 Core0,SRC.TOS = 1, 则该中断就映射到 DMA,SRC.TOS = 3, 则该中断就映射到 Core3 等。

ICU 的 主要工作包括:

- 将映射到该 ICU 的 SRN 发出的SR(Service Request) 进行中断仲裁,并将仲裁结果提供给 SP;

- 接收 SP 的中断通知;

- 进行 ECC 校验,并将ECC错误发送到SMU;

- 清除中断通知;

ICU 控制寄存器

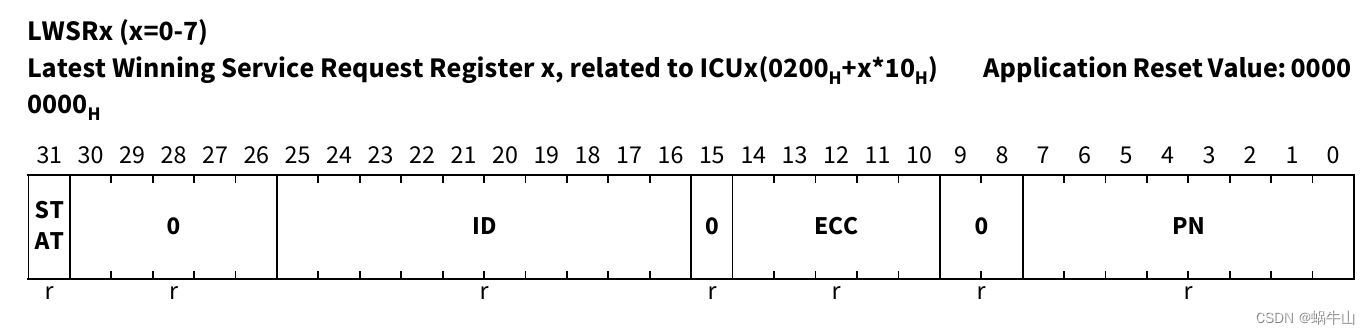

LWSR

| Field | Bits | Type | Description |

| PN | 7:0 | r | 仲裁完成后ICU送到 SP 的中断优先级。仅当 STAT == 1 时有效。 |

| ECC | 14:10 | r | 仲裁完成后ICU送到 SP 的中断 SRN.ECC。仅当 STAT == 1 时有效。 |

| ID | 25:16 | r | 仲裁完成后ICU送到 SP 的中断编号。仅当 STAT == 1 时有效。 |

| STAT | 31 | r | 0: LWSR 无效 1: LWSR 有效 |

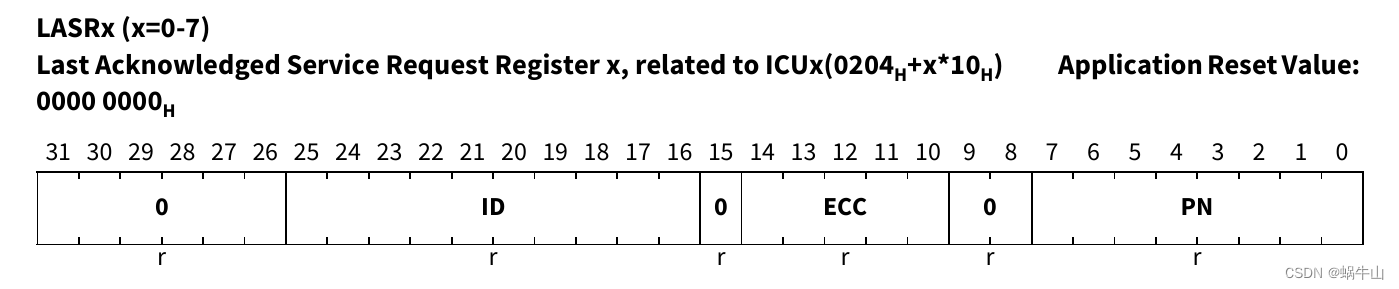

LASR

| Field | Bits | Type | Description |

| PN | 7:0 | r | SP 通知 ICU 的中断优先级。 |

| ECC | 14:10 | r | SP 通知 ICU 的中断ECC。 |

| ID | 25:16 | r | SP 通知 ICU 的中断编号。 |

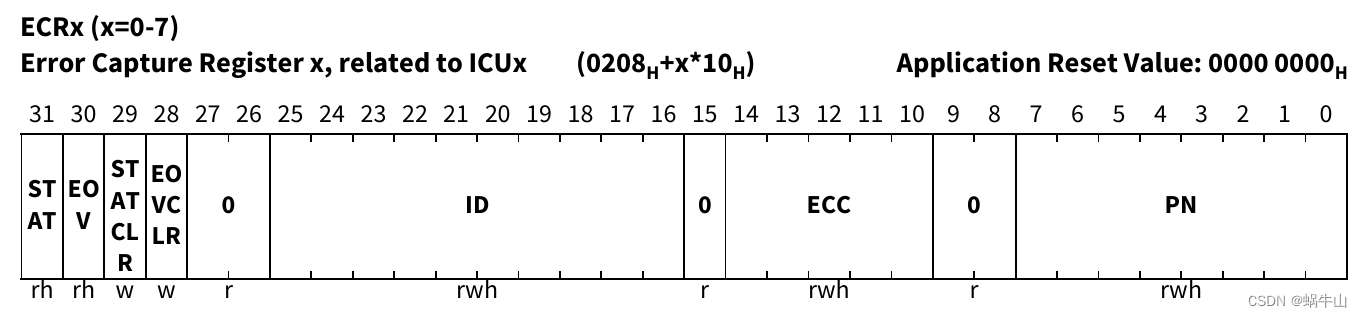

ECR

| Field | Bits | Type | Description |

| PN | 7:0 | r | 检测到错误的最新中断优先级。 |

| ECC | 14:10 | r | 检测到错误的最新中断ECC。 |

| ID | 25:16 | r | 检测到错误的最新中断编号。 |

| EOVCLR | 28 | w | 清除 EOV bit 0:No action 1:Clear EOV bit; bit value is not stored; read always returns 0; no action if EOV bit is set in parallel. |

| STATCLR | 29 | w | 清除 STATbit 0:No action 1:Clear STAT bit; bit value is not stored; read always returns 0; no action if STAT bit is set in parallel. |

| EOV | 30 | rh | Error Overflow Bit The bit is set if an ECC error was detected by the ICU while ECR.STAT=´1´ (Error Overflow situation). 0:No Error Overflow situation detected 1:Error Overflow situation detected |

| STAT | 31 | rh | Error Status Bit The Error Status Bit is set whenever an ECC was detected by the ICU. 0:No ECC error detected 1:B ECC error detected |

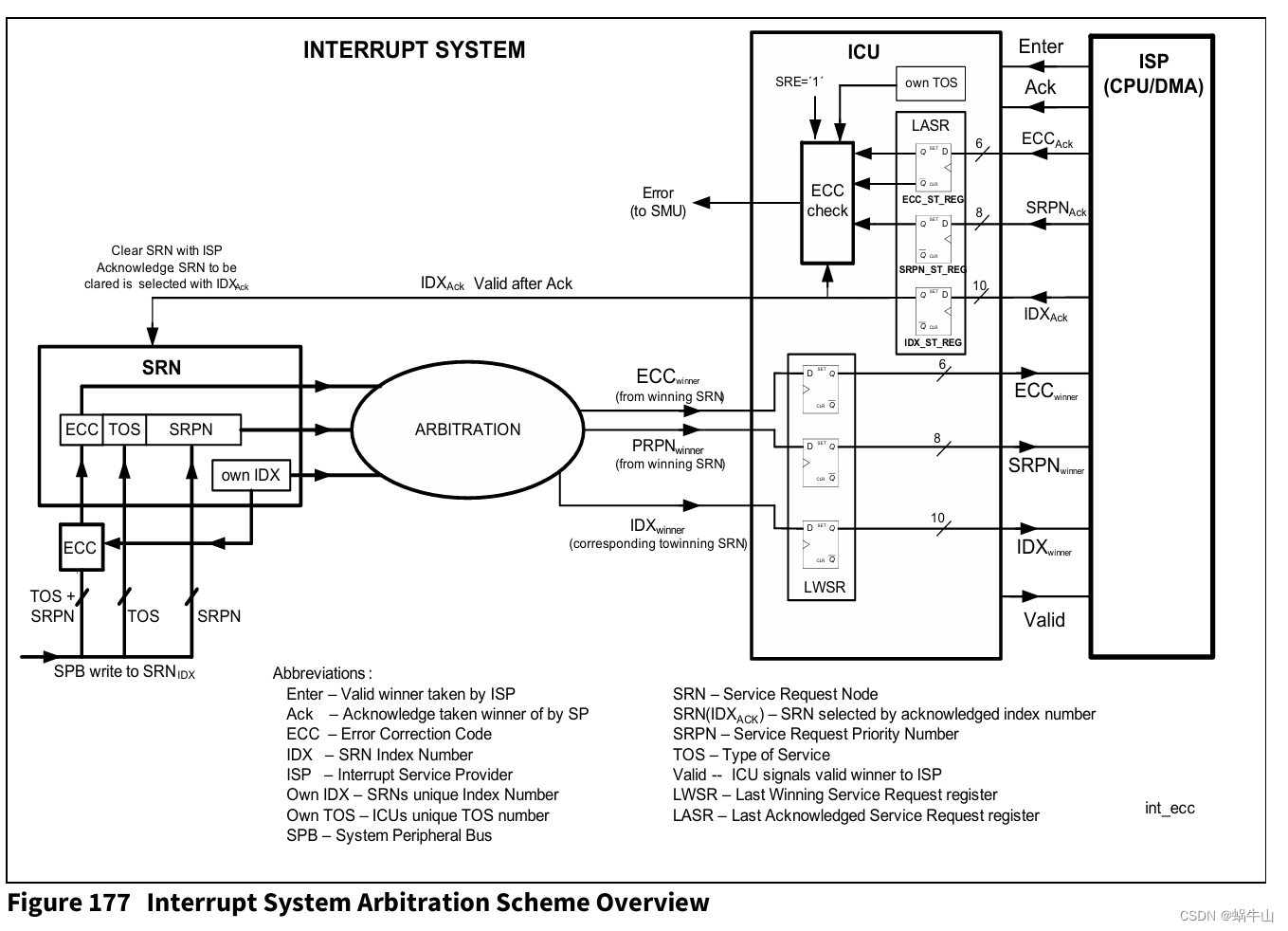

仲裁(Arbitration)

仲裁过程

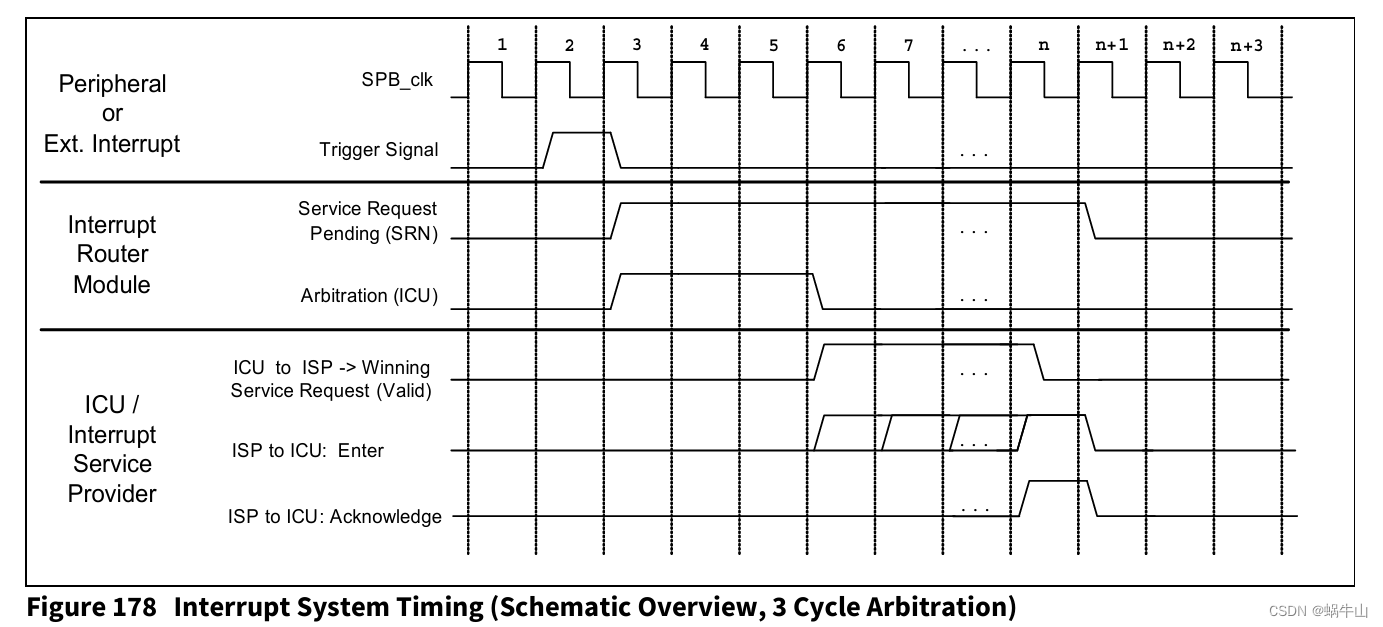

如上图所示,当第一个中断请求处于 Pending 状态时,中断总线就回开始仲裁处理。仲裁过程大概耗时 3-4 系统外设总线时钟周期。仲裁完成后 ICU会将仲裁获胜即最高优先级的 SR 信息 (SRPN, ECC, SRN Index)装载到 LWSR 中发送给 SP。等 SP 通过 LASR 发回 acknowledge 信息后,ICU 会对 SP 通知的 ECC, SRPN, SRN Index Number 进行 ECC检查,如果此时检测到 ECC错误,则会将 ECC 错误信息装载到 ECR 中,并向 SMU(Safety Management Unit) 发送错误信号。

仲裁时序

假设IR 的实现中仲裁耗时3 个SP时钟周期,则如上图所示:

- Cycle 1: 没有 SR(service request) 处于 pending 状态;

- Cycle 2: 某个模块触发中断,并向其 SRN 发送 SR;

- Cycle 3-5: 对所有处于 Pending 状态的 SR 进行仲裁;

- Cycle 6: ICU 将在仲裁中获胜的 SR 信息 (包括SRPN, ECC, SRN Index)提供给 SP;

- Cycle 7 - n-1: 如果在此期间又有一个新的 SRN 处于 Pending 状态,则 ICU 回重新进行仲裁,从而提供最高优先级的 SR 给到 SP;

- Cycle 6- n-1: SP 接收最新获胜SRN信息 (Enter);

- Cycle n: SP 通知(acknowledges) SR (包括 SRPN, ECC, SRN Index). 在同一个时钟周期内,ICU 状态转变为 ´无有效 SR´ ,即SR处理结束.

- Cycle n+1: ICU 对通知信息进行 ECC 检查,若有ECC错误回更新在ECR寄存器中并通知SMU。硬件会清除通知的SRN。

- Cycle n+2: 如果此时有 新的 SR 处于 Pending 状态,则回开始下一轮仲裁。

以后博客内容会同步更新在订阅号 AutomotiveOS,喜欢的可以关注:)

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?