前言

这一篇主要还是提供给了解C的工程师,方便快速的上手Verilog的思维和编写方法

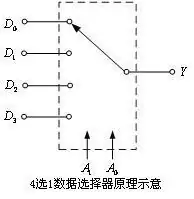

从多路选择器了解Verilog语法

多路选择器,名称有点厉害但其实就是一个多路输入然后通过一路输入切换输出的小玩意,比如这个就是一个四进一出,二切换输入的多路选择器。

这个选择器不需要时钟,所以我觉得更能理解Verilog的本质,Verilog的本质就是使用代码来定义一个芯片的功能。只要想,以及芯片资源足够,就可以让CPLD或FPGA变成任意的其他芯片。

先来看一下整个代码

module mux(in1,in2,sel,out);

parameter N=4;

output[N:1] out;

input[N:1] in1,in2;

input sel;

assign out=sel?in1:in2;

endmodule 一句一句分析,首先verilog这边定义是“使用编程代码来定义硬件模块”,所以,会有一个语句结构,括号内定义的是输入和输出端口

module name(inputs1,inp.....output2)

endmodule先行定义和之后定义都可以,你可以这样

module name(input a,output b);

endmodule也能这样

module name( a, b);

input a;

output b;

endmodule然后在这个框体里面,会填入一些定义,比如说定一个参数

parameter N=4;这个参数用途我觉得其实更像是C里面的#define因为你可以用这个来定义位的宽度,比如这里就是描述一个out端口,它有1,2,3,4,也就是4位

output[N:1] out;输入端口的描述也是一样,使用了N参数

input[N:1] in1,in2;当然可以不定义多个位的端口,可以直接定一个只有一位的端口

input sel;然后,我们把端口和寄存器连接一下,这样寄存器有变化,那端口就有变化

assign out=sel?in1:in2;

2027

2027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?