Xv6 Page Table

Learning xv6-riscv-book Chapter 3 Page tables

文章目录

Isolate different process’s address spaces and to multiplex them onto a single physical memory.

Paging hardware

Sv39 RISC-V:

-

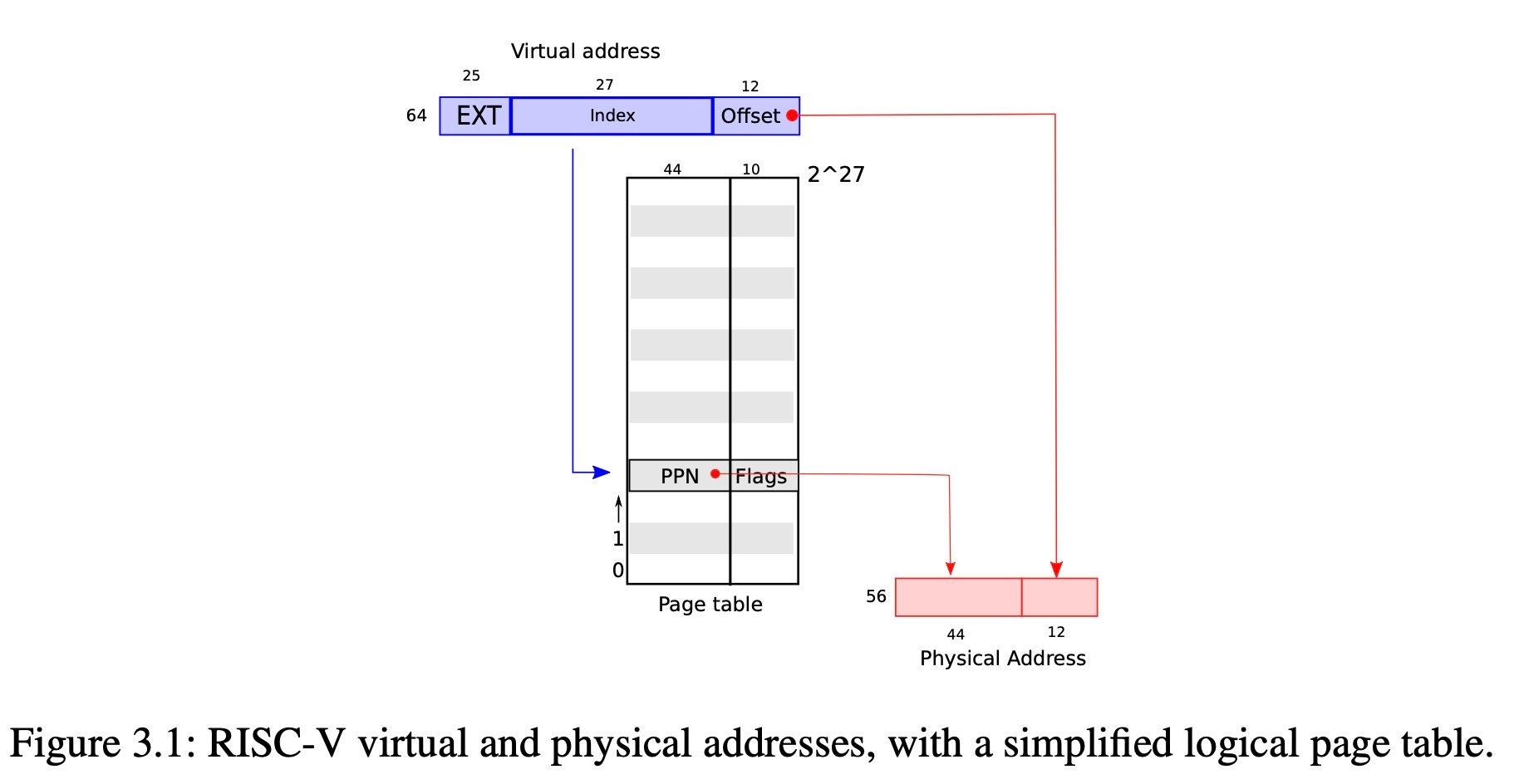

Xv6 runs on Sv39 RISC-V: only the bottom 39 bits of a 64-bit virtual address are used; the top 25 bits are not used.

-

a RISC-V page table: an array of 2 27 2^{27} 227 page table entries (PTEs)

-

a PTE: a 44-bit physical page number (PPN) and flags.

[Logically] The paging hardware: virtual address => physical address:

- handle a 39-bit virtual address

- top 27 bits of the 39 bits: index into the page table to find a PTE

- bottom 12 bits: do not change

- making a 56-bit physical address:

- top 44 bits come from the PPN in the PTE

- bottom 12 bits are copied from the original virtual address.

Virtual-to-physical address translations: aligned chunks of

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6402

6402

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?