源码

GitHub:https://github.com/Kilento/4412NoOS

时钟的作用

就如人离不开心脏的跳动一般,嵌入式系统的工作也离不开时钟的“跳动”。嵌入式SoC本身就是一个庞大的数字电路。这些电路的工作需要时钟进行同步,比如SoC中的CPU、串口、DRAM 控制器等等。

时钟的产生

时钟的来源一般可以有三种:

- 外部晶振 + 内部时钟发生器

- 外部时钟直接输入

- 外部晶振 + 内部时钟发生器 + 锁相环 + 分频器

像 Exynos4412 这种较为复杂的 arm 芯片一般都使用第3种,可以产生更多的时钟频率。外部晶振一般无法产生频率过高的时钟信号,比如iTop-4412的外部晶振时钟频率是 24MHz。而 CPU 工作的频率则往往达到几百MHz甚至几GHz。所以需要通过锁相环进行倍频然后通过分频器进行分频输出各种不同频率的时中信号。

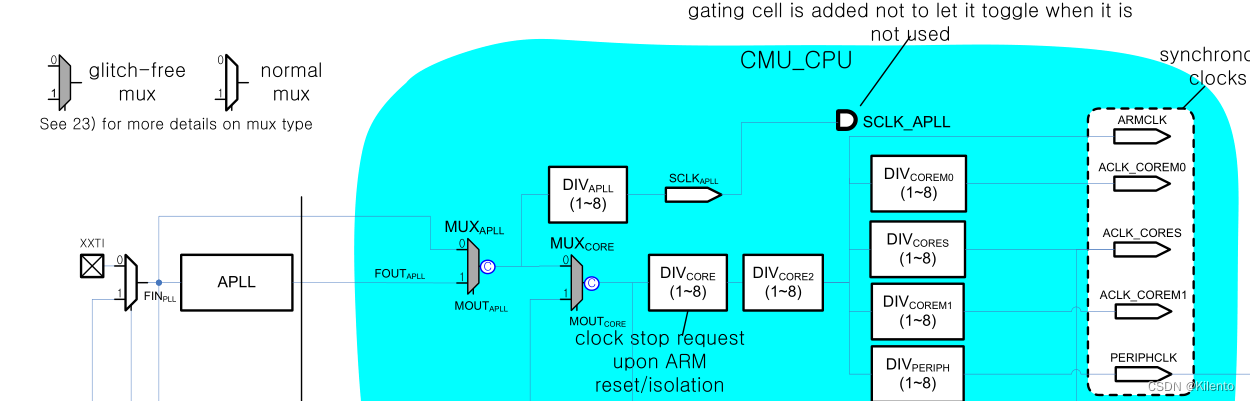

Exynos4412的时钟产生比较复杂,有兴趣的可以查看数据手册下图:

Exynos4412 的时钟域

Exynos4412 的 CPU 可以工作在 200MHz ~ 1.4 GHh 的时钟频率下,也就是我们熟知的主频。除了主频以外,Exynos4412 还划分了如下图不同的时钟域。

时钟关键寄存器

- xPLL_LOCK(x可以为A、V、E、M)

PLL_LOCK 寄存器用于控制 PLL 锁定周期的,倍频需要一定的时间。 - xPLL_CONn

PLL_CON 寄存器主要用来打开/关闭PLL电路,设置PLL的倍频参数,查看PLL锁定状态等 - CLK_SRC_XXX

CLK_SRC_XXX 寄存器是用来设置时钟来源的,对应时钟框图中的MUX开关。 - CLK_SRC_MASK_XXX

CLK_SRC_MASK 决定 MUX 开关 n 选 1 后是否能继续通过。默认打开,关闭可以减少耗能。 - CLK_DIV_XXX

各模块的分频器参数配置 - CLK_GATE_XXX

类似于 CLK_SRC_MASK,对时钟进行开关控制 - CLK_DIV_STAT_XXX

- CLK_MUX_STAT_XXX

用来查看 DIV 和 MUX 的状态是否已经完成还是在进行中

时钟设置的一般步骤

- 设置 PLL 的锁定周期( xPLL_LOCK)

- 设置 PLL 的倍频参数(xPLL_CONn)

- 选择时钟源(CLK_SRC)

- 选择分频参数(CLK_DIV)

典型代码

lowlevel_init:

// 初始化 APLL_LOCK 寄存器,设置锁定周期

ldr r0, =(APLL_LOCK)

ldr r1, =0x00000FFF

str r1, [r0]

// 初始化 MPLL_LOCK 寄存器,设置锁定周期

ldr r0, =(MPLL_LOCK)

ldr r1, =0x00000FFF

str r1, [r0]

// 初始化 EPLL_LOCK 寄存器,设置锁定周期

ldr r0, =(EPLL_LOCK)

ldr r1, =0x00000FFF

str r1, [r0]

// 初始化 VPLL_LOCK 寄存器,设置锁定周期

ldr r0, =(VPLL_LOCK)

ldr r1, =0x00000FFF

str r1, [r0]

// 使能 APLL PDIV = 3, MDIV = 125, SDIV = 0, Fvco_out = Fref

// Fref = FIN / PDIV = 24MHz / 3 = 8MHz

// FAPLLOUT = MDIV * FIN / (PDIV + 2^SDIV) = 125 * 24Mhz / (3 * 2 ^ 0) = 1000MHz

ldr r0, =(APLL_CON0)

ldr r1, =0x807D0300

str r1, [r0]

// 使能 MPLL PDIV = 3, MDIV = 100, SDIV = 0, Fvco_out = Fref

// Fref = FIN / PDIV = 24MHz / 3 = 8MHz

// FMPLLOUT = MDIV * FIN / (PDIV + 2^SDIV) = 100 * 24Mhz / (3 * 2 ^ 0) = 800MHz

ldr r0, =(MPLL_CON0)

ldr r1, =0x80640300

str r1, [r0]

// 使能 EPLL PDIV = 3, MDIV = 100, SDIV = 1, Fvco_out = Fref

// Fref = FIN / PDIV = 24MHz / 3 = 8MHz

// FEPLLOUT = (MDIV + K/65536 ) * FIN / (PDIV + 2^SDIV) = (100 + 0 / 65536) * 24Mhz / (3 * 2 ^ 1) = 400MHz

ldr r0, =(EPLL_CON0)

ldr r1, =0x80640301

str r1, [r0]

// 使能 VPLL PDIV = 3, MDIV = 100, SDIV = 3, Fvco_out = Fref

// Fref = FIN / PDIV = 24MHz / 3 = 8MHz

// FVPLLOUT = (MDIV + K/65536 ) * FIN / (PDIV + 2^SDIV) = (100 + 0 / 65536) * 24Mhz / (3 * 2 ^ 3) = 100MHz

ldr r0, =(VPLL_CON0)

ldr r1, =0x80640303

str r1, [r0]

// MUX_MPLL_USER_SEL_C = FOUTMPLL MUX_HPM_SEL = MOUTAPLL MUX_CORE_SEL = MOUTAPLL MUX_APLL_SEL = MOUTAPLLFOUT

ldr r0, =(CLK_SRC_CPU)

ldr r1, =0x01000001

str r1, [r0]

// MUX_PWI_SEL = XusbXTI MUX_MPLL_SEL = MOUTMPLLFOUT

ldr r0, =(CLK_SRC_DMC)

ldr r1, =0x00011000

str r1, [r0]

// MUX_ONENAND_SEL = ACLK_133 MUX_ACLK_133_SEL = SCLKMPLL MUX_ACLK_160_SEL = SCLKMPLL MUX_ACLK_100_SEL = SCLKMPLL

// MUX_ACLK_200_SEL = SCLKMPLL MUX_EPLL_SEL = FOUTEPLL MUX_EPLL_SEL = FOUTEPLL MUX_ONENAND_1_SEL = MOUTONENAND

ldr r0, =(CLK_SRC_TOP0)

ldr r1, =0x00000110

str r1, [r0]

// MUX_MPLL_USER_SEL_T = SCLKMPLLL MUX_ACLK_266_GPS_SUB_SEL = DIVOUT_ACLK_266_GPS

ldr r0, =(CLK_SRC_TOP1)

ldr r1, =0x00011000

str r1, [r0]

// MUX_MPLL_USER_SEL_L = FOUTMPLL MUX_GDL_SEL = SCLKMPLL

ldr r0, =(CLK_SRC_LEFTBUS)

ldr r1, =0x00000010

str r1, [r0]

// MUX_MPLL_USER_SEL_R = FOUTMPLL MUX_GDR_SEL = SCLKMPLL

ldr r0, =(CLK_SRC_RIGHTBUS)

ldr r1, =0x00000010

str r1, [r0]

// CORE2_RATIO = 0 APLL_RATIO = 1 PCLK_DBG_RATIO = 1 ATB_RATIO = 4 PERIPH_RATIO = 3

// COREM1_RATIO = 7 COREM0_RATIO = 3 CORE_RATIO = 0

ldr r0, =(CLK_DIV_CPU0)

ldr r1, =0x01143730

str r1, [r0]

// CORES_RATIO = 0 HPM_RATIO = 0 COPY_RATIO = 4

ldr r0, =(CLK_DIV_CPU1)

ldr r1, =0x00000004

str r1, [r0]

// DMCP_RATIO = 1 DMCD_RATIO = 1 DMC_RATIO = 1 DPHY_RATIO = 1 ACP_PCLK_RATIO = 1 ACP_RATIO = 3

ldr r0, =(CLK_DIV_DMC0)

ldr r1, =0x00111113

str r1, [r0]

// DPM_RATIO =1 DVSEM_RATIO = 1 C2C_ACLK_RATIO = 1 PWI_RATIO = 1 C2C_RATIO = 1 G2D_ACP_RATIO = 3

ldr r0, =(CLK_DIV_DMC1)

ldr r1, =0x01011113

str r1, [r0]

// ACLK_400_MCUISP_RATIO = 1 ACLK_266_GPS_RATIO = 2 ONENAND_RATIO = 0 ACLK_133_RATIO = 5

// ACLK_160_RATIO = 4 ACLK_100_RATIO = 7 ACLK_200_RATIO = 3

ldr r0, =(CLK_DIV_TOP)

ldr r1, =0x01205473

str r1, [r0]

// GPL_RATIO = 1 GDL_RATIO = 3

ldr r0, =(CLK_DIV_LEFTBUS)

ldr r1, =0x00000013

str r1, [r0]

// GPR_RATIO = 1 GDR_RATIO = 3

// ACLK_GPR = MOUTGPR/(GPR_RATIO + 1)

// ACLK_GDR = MOUTGDR/(GDR_RATIO + 1)

ldr r0, =(CLK_DIV_RIGHTBUS)

ldr r1, =0x00000013

str r1, [r0]

mov pc, lr

主频

以主频 ARMCLK 为例:

要得到主频 ARMCLK,由下图可知,需要知道 APLL 倍频系数、MUX_APLL_SEL、MUX_CORE_SEL、DIV_CORE、DIV_CORE2 等值。

这些值分别由寄存器 APLL_CON0、CLK_SRC_CPU、CLK_DIV_CPU0 寄存器控制。

这些值分别由寄存器 APLL_CON0、CLK_SRC_CPU、CLK_DIV_CPU0 寄存器控制。

输入频率 FINPLL = 24MHz

由代码可知:

PDIV = 3, MDIV = 125, SDIV = 0

FAPLLOUT = MDIV * FIN / (PDIV + 2SDIV) = 125 * 24Mhz / (3 * 2 0) = 1000MHz

MUX_APLL_SEL = MOUTAPLLFOUT,即 MUXAPLL 选择 1 开关

MUX_CORE_SEL = MOUTAPLL,即 MUXCORE 选择 0 开关

DIV_CORE = CORE_RATIO + 1 = 1

DVI_CORE2 = CORE2_RATIO + 1 = 1

由此可得 ARMCLK = FAPLLOUT / 1 / 1 = 1000MHz

其余时钟频率也可由此方法推导得出

2021年10月7日

Kilento

5021

5021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?