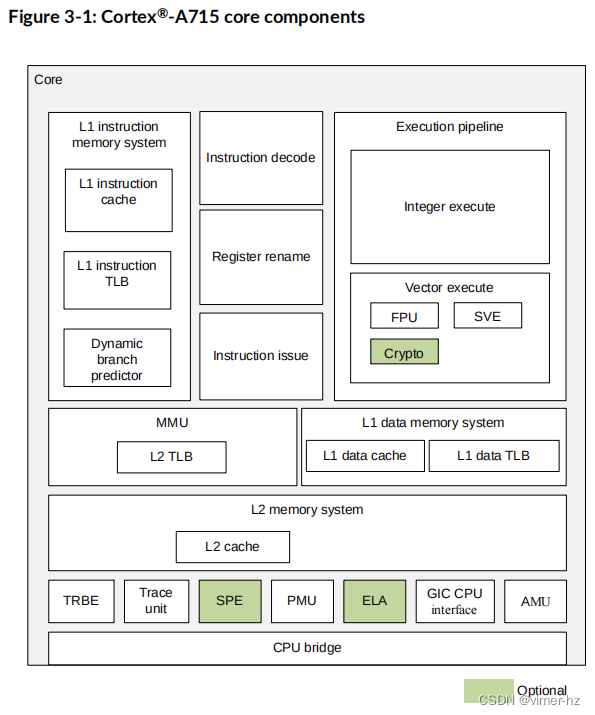

Cortex®‑A715核心中的组件旨在使其成为一个平衡性能的核心。主要组件包括:

• L1指令和L1数据存储系统

• L2存储系统

• 寄存器重命名

• 指令解码

• 指令发射

• 执行流水线

• 存储管理单元(MMU)

• 追踪单元和追踪缓冲区

• 性能监控单元(PMU)

• 活动监控单元(AMU)

• 通用中断控制器(GIC)CPU接口

• 分支预测

Cortex®‑A715核心通过CPU桥与DynamIQ™ Shared Unit-110(DSU-110)进行接口连接。

Cortex®‑A715核心实现了Arm®v9.0-A架构。Arm®v9.0-A架构扩展了Arm®v8‑A架构中定义的架构,一直延伸到Arm®v8.5-A。

程序员模型和实现的体系结构特性(例如通用计时器)符合第25页上所述的2.4支持的标准和规范。

3.1 Core components

Cortex®‑A715核心包括一系列组件,旨在使其成为一个平衡性能、低功耗且面积受限的产品。Cortex®‑A715核心包括一个CPU桥,将核心连接到DynamIQ™ Shared Unit-110(DSU-110)。DSU-110将核心连接到外部存储系统和片上系统(SoC)的其他部分。

下图显示了Cortex®‑A715核心的组件。

L1 instruction memory system

L1指令存储系统从指令缓存中获取指令,并将指令流传递给指令解码单元。

L1指令存储系统包括:

• 32KB或64KB的4路组相联式L1指令缓存,每个缓存行大小为64字节

• 完全关联的L1指令转换后置缓冲器(TLB),原生支持4KB、16KB、64KB和2MB页面大小

• 动态分支预测器

Instruction decode

指令解码单元将AArch64指令解码为一个内部格式,并将其传递到执行流水线中。解码单元负责解析指令的操作码、操作数和操作顺序,并将其转换为可被执行的内部表示形式,以供后续阶段执行。这样,处理器可以正确地理解和执行指令的操作。解码完成后,解码单元将解码后的指令传递给执行流水线的下一个阶段,从而启动指令的实际执行过程。

Register rename

寄存器重命名单元执行寄存器重命名,以便实现乱序执行,并将解码的指令发送到各种发布队列。

寄存器重命名是一种技术,通过为指令中的目标寄存器分配重命名寄存器,来解决由于指令间数据依赖关系而导致的数据冲突。这样,不同的指令可以并发地使用相同的物理寄存器,从而允许指令乱序执行,提高了处理器的性能。

寄存器重命名单元负责分配重命名寄存器,并将解码的指令发送到相应的发布队列。发布队列是用于保存将要执行的指令,并确保它们按照正确的顺序进入执行阶段。通过寄存器重命名和发布队列的组合使用,处理器能够更高效地利用指令级并行性,提升整体执行效率。

Instruction issue

指令分发单元控制解码后的指令何时被分派到执行流水线。它包括用于存储待分派到执行流水线的指令的发布队列。

Integer execute

执行流水线包括整数执行单元,用于执行算术和逻辑数据处理操作。

Vector execute

矢量执行单元是执行流水线的一部分,用于执行高级SIMD和浮点运算。矢量执行单元执行可扩展矢量扩展(SVE)和可扩展矢量扩展2(SVE2)指令,并可选择执行加密指令。

-高级SIMD和FP支持

高级SIMD是一种媒体和信号处理架构,主要添加了用于音频、视频、3D图形、图像和语音处理的指令。浮点数架构提供对单精度和双精度浮点操作的支持。

-加密扩展

加密扩展在Cortex®‑A715核心中是可选的。加密扩展向高级SIMD和可扩展矢量扩展(SVE)指令集添加了新指令,加速以下功能:

- 高级加密标准(AES)加密和解密。

- 安全哈希算法(SHA)函数SHA-1、SHA-3、SHA-224、SHA-256、SHA-384和SHA-512。

- Armv8.2-SM SM3哈希函数和SM4加密和解密指令。

- 有限域算术,用于诸如Galois/Counter Mode和椭圆曲线密码术等算法。

可选的加密扩展不包含在基本产品中。Arm仅在额外的Cortex®‑A715核心许可证下提供加密扩展。

-可扩展矢量扩展

可扩展矢量扩展(SVE)和可扩展矢量扩展2(SVE2)是Armv8-A架构的扩展。

它们是对AArch64高级SIMD和浮点功能的补充,而不是替代品。

L1 data memory system

L1数据内存系统执行加载和存储指令,并处理内存一致性请求。

L1数据内存系统包括:

- 32KB或64KB的4路组关联缓存,其中缓存行大小为64字节。

- 全关联的L1数据TLB,原生支持4KB、16KB、64KB和2MB的页面大小。

Memory Management Unit

内存管理单元(MMU)通过一组虚拟地址到物理地址映射和内存属性,在转换表中提供细粒度的内存系统控制。当地址被转换时,这些映射关系会保存在TLB中。TLB条目包括全局标识符(ASID)和地址空间标识符(ASID),以防止上下文切换导致的TLB无效。它们还包括虚拟机标识符(VMID),以防止虚拟机切换时由虚拟机监视程序导致的TLB无效。

L2 memory system

L2内存系统包括L2缓存。L2缓存是私有的,每个核心具有8路组关联性。您可以将其RAM大小配置为128KB、256KB或512KB。L2内存系统通过CPU桥连接到DSU-110。

Embedded Trace Extension and Trace Buffer Extension

Cortex®‑A715核心支持一系列的调试、测试和跟踪选项,包括跟踪单元和跟踪缓冲区。

Cortex®‑A715核心还包括一个ROM表,其中包含系统中的组件列表。调试器可以使用ROM表确定实现了哪些CoreSight™组件。

Cortex®‑A715核心的所有调试和跟踪组件都在本手册中进行了描述。有关嵌入式逻辑分析仪(ELA)的更多信息,请参阅Arm® CoreSight™ ELA-600嵌入式逻辑分析仪技术参考手册。

Statistical Profiling Extension

在Cortex®‑A715核心中,统计分析扩展(SPE)是可选的。Cortex®‑A715核心实现了Arm®v8.2-A架构中的SPE。SPE提供了执行指令的性能特性的统计视图,软件开发者可以利用这些统计数据来优化代码,以实现更好的性能。

Performance Monitoring Unit

性能监控单元(PMU)提供了6个或20个性能监视器,可以配置为收集每个核心和内存系统的操作统计数据。这些信息可用于调试和代码性能分析。

Activity Monitoring Unit

Cortex®‑A715核心实现了Arm®v8.4-A架构中的活动监视器扩展。活动监视器在活动监视单元(AMU)中提供有用的信息,用于系统功耗管理和持续监控。

GIC CPU interface

通用中断控制器(GIC)CPU接口,与外部分发器组件集成时,是支持和管理集群系统中断的资源。

CPU bridge

在一个集群中,每个Cortex®‑A715核心和DSU-110之间有一个CPU桥。CPU桥控制核心和DSU-110之间的缓冲和同步。CPU桥是异步的,允许每个核心具有不同的频率、功耗和面积实现点。您可以配置CPU桥以同步运行,而不影响其他始终同步的接口,如调试和跟踪。

相关信息:

6. 内存管理(第51页)

7. L1指令内存系统(第60页)

8. L1数据内存系统(第63页)

9. L2内存系统(第68页)

13. GIC CPU接口(第84页)

18. 性能监控扩展支持(第98页)

19. 嵌入式跟踪扩展支持(第113页)

20. 跟踪缓冲区扩展支持(第122页)

21. 活动监视器扩展支持(第123页)

22. 统计分析扩展支持(第127页)

3.2 Interfaces

DynamIQ™ Shared Unit-110 (DSU-110)是用于管理所有Cortex®‑A715核心与片上系统(SoC)之间的外部接口的模块。

您可以参考Arm® DynamIQ™ Shared Unit-110技术参考手册中的技术概述,以获取有关这些接口的详细信息。

3.3 Programmers model

Cortex®‑A715核心实现了Arm®v9.0-A架构。Arm®v9.0-A架构扩展了Arm®v8‑A架构,一直延伸到Arm®v8.5-A。Cortex®‑A715核心在所有异常级别(EL0到EL3)都支持AArch64执行状态。

您可以参考Arm® Architecture Reference Manual for A-profile architecture,以获取有关程序员模型的更多信息。

相关信息:

2.4 支持的标准和规范(第25页)

1021

1021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?