写偏斜(Write Skew)

写偏斜可以理解为事务commit之前写前提被破坏,导致写入了违反业务一致性的数据,网上有个很好的简称为写前提困境,也就是读出某些数据,作为另一些写入的前提条件,但是在提交前,读入的数据就已被别的事务修改并提交,这个事务并不知道,然后commit了自己的另一些写入,写前提在commit前就被修改,导致写入结果违反业务一致性。

写偏斜发生在写前提与写入目标不相同的情境下。

这是业务开发中最容易出错地方,如果开发者不太理解隔离级别,也不知道目前使用的是哪个隔离级别,很可能写出有写偏斜的代码,造成业务不一致。

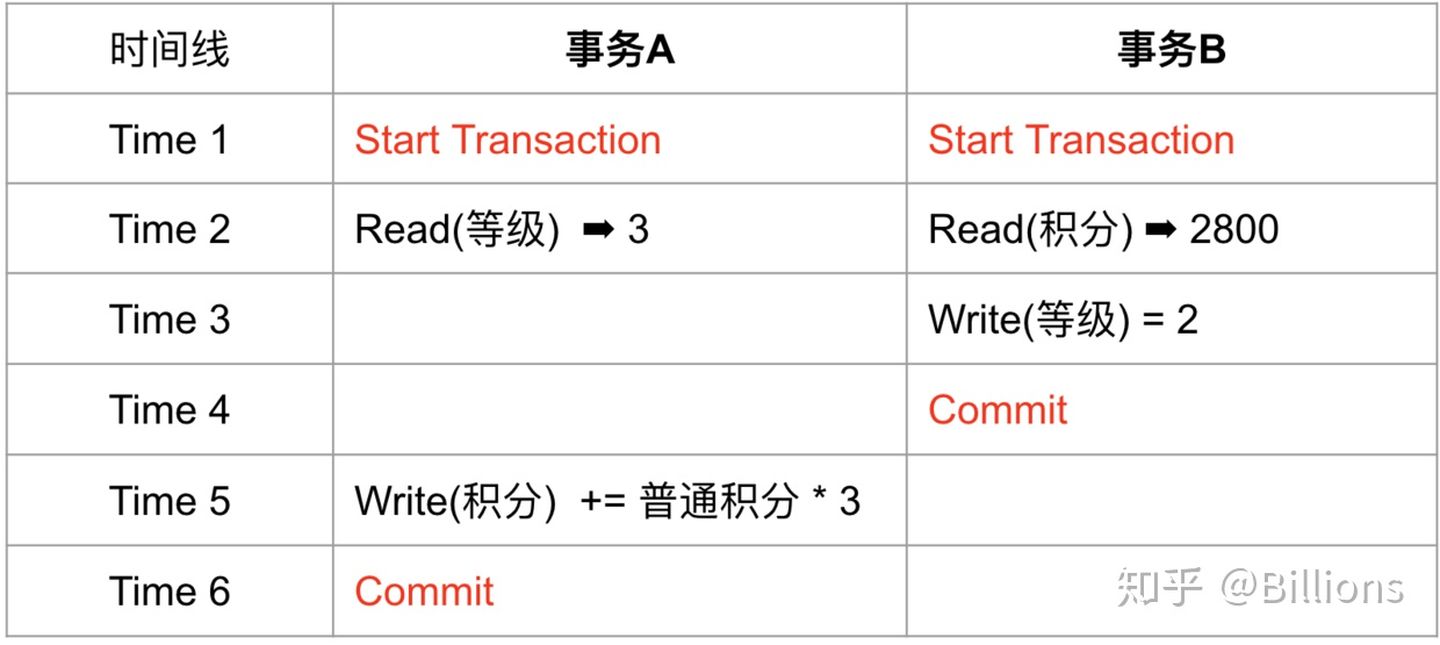

举个例子:

信用卡系统对不同等级的会员有积分加成,3级会员则每次都3倍积分,同时,会有定时任务检查当积分不满足要求时,就会降级。

首先,会员进行了刷卡消费,此时要计算积分,开启了事务A,读到会员等级为3,与此同时定时任务也开始了,读到会员积分为2800,已经不满足3000分应该降级为2级,然后将会员等级降级为2并且commit,由于事务A读到的等级为3,它还是按照3倍积分为会员增加了积分,会员赚了,多亏那个程序员不理解他使用的事务隔离级别,出现了业务不一致。

丢失更新(Lost Updates)

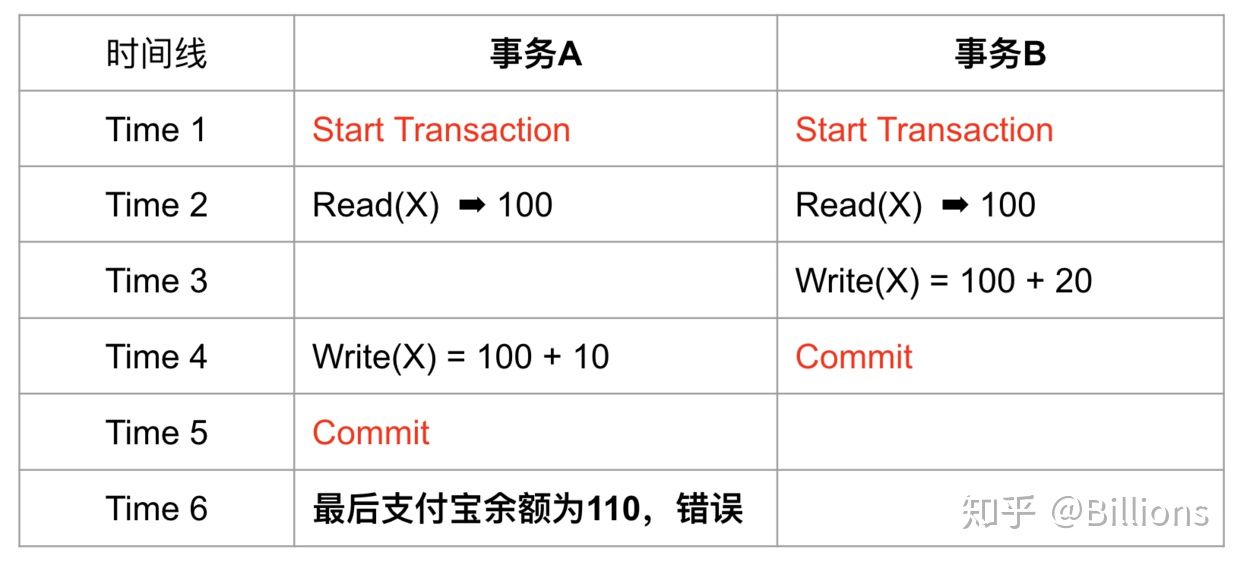

由于未提交事务之间看不到对方的修改,因此都以一个旧前提去更新同一个数据,导致最后的提交结果是错误值。

假设有支付宝账户X,余额100元,事务A、B同时向X分别充值10元、20元,最后结果应该为130元,但是由于丢失更新,最后是110元。

丢失更新与写偏斜很相似,都是由于写前提被改变,

他们区别是,丢失更新是在同一个数据的最终不一致,而写偏斜的冲突不在同一个数据,在不同数据中的最终不一致。

362

362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?