第2章 IA-32处理器体系结构

2.1 基本概念

本章以程序员的视角描述Intel IA-32处理器家族机器计算机系统,包括所有的Intel兼容处理器,如AMD的速龙(Athlon)和皓龙(Opteron)处理器。汇编语言是学习计算机如何运行的绝好工具,同时这也就要求读者具备计算机硬件的相关知识。本章的目的就是科普相关知识。

2.1.1 微机的基本结构

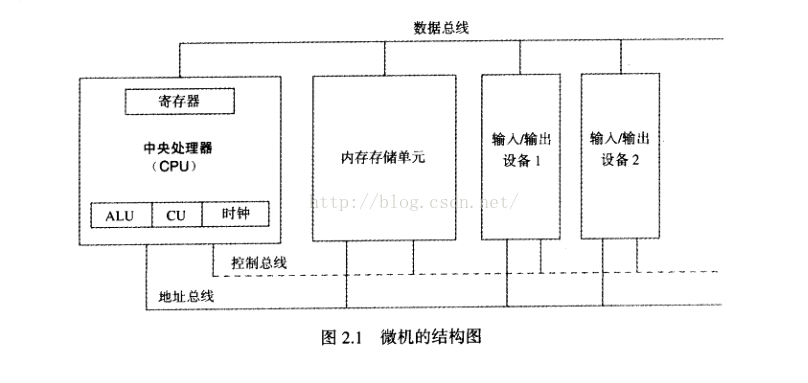

中央处理器(CPU,Central Processor Unit)是进行所有计算和逻辑操作的地方,它包含了数量有限的称为寄存器(register)的存储单元,一个高频时钟(clock)、一个控制单元(CU ,Control Unit)和一个算术逻辑单元(ALU,Arithmetic Logic Unit)。

(1)时钟用于CPU的内部操作和其他系统部件的同步。

(2)控制单元(CU)系统调执行机器指令各个步骤的次序。

(3)算术逻辑单元(ALU)执行加法和减法等算术运算,以及AND,OR和NOT等逻辑运算。

CPU通过插入主板插槽的引脚同计算机的其余部分相连接,大部分引脚与数据总线,控制总线和地址总线相连接。

内存存储单元是计算机程序运行时存放指令和数据的地方。内存存储单元接受CPU的数据请求,从随机访问存储器(RAM)中取出数据送至CPU,火把数据从CPU送回寄存器中。

总线(BUS)是一组用于在计算机各部分之间传送数据的并行线。计算机的总线一般分为三组独立的总线构成:数据总心啊、控制总线和地址总线。数据总线(data bus)在CPU和内存之间传送指令和数据;控制总线(control bus)使用二进制信号同步连接到系统总线上的所有设备的动作;如果当前被执行的指令要在CPU和内存之间传输数据,那么地址总线上保持着指令和数据的地址。

本文详细介绍了IA-32处理器的基本概念,包括CPU的组成、微机结构、指令执行周期和内存读取过程。内容涵盖了时钟、控制单元、ALU的作用,以及流水线技术、内存访问和缓存的工作原理。同时,解释了程序如何在处理器上运行的流程,涉及到加载、执行和多任务处理的概念。

本文详细介绍了IA-32处理器的基本概念,包括CPU的组成、微机结构、指令执行周期和内存读取过程。内容涵盖了时钟、控制单元、ALU的作用,以及流水线技术、内存访问和缓存的工作原理。同时,解释了程序如何在处理器上运行的流程,涉及到加载、执行和多任务处理的概念。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2348

2348

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?