前言:

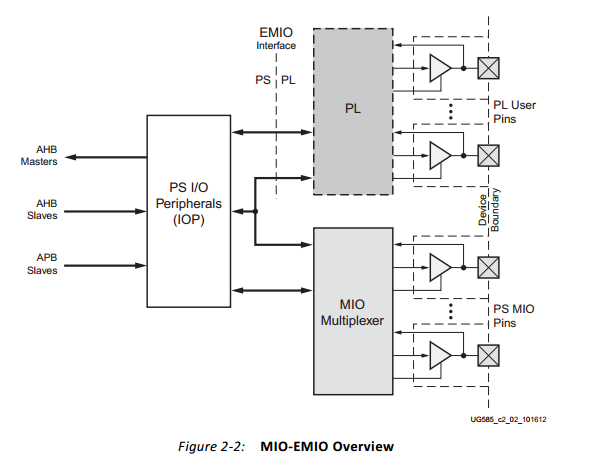

ZYNQ 7000有三种GPIO:MIO,EMIO,AXI_GPIO

MIO是固定管脚的,属于PS,使用时不消耗PL资源;EMIO通过PL扩展,使用时需要分配管脚,使用时消耗PL管脚资源;AXI_GPIO是封装好的IP核,PS通过M_AXI_GPIO接口控制PL部分实现IO,使用时消耗管脚资源和逻辑资源。

使用的板子是zc702。

1.MIO方式

Zynq7000 系列芯片有 54 个 MIO(multiuse I/O), 它们分配在 GPIO 的 Bank0 和Bank1 隶属于 PS 部分, 这些 IO 与 PS 直接相连。 不需要添加引脚约束, MIO 信号对 PL部分是透明的, 不可见。 所以对 MIO 的操作可以看作是纯 PS 的操作。

新建Vivado工程,添加ZYNQ CPU核,双击,配置好时钟和内存类型,确认勾选MIO:

如系列(三)文章所述,生成bit stream,然后Launch SDK。

在SDK中新建工程,源文件如下:

#include "xgpiops.h"

#include "sleep.h"

int main()

{

static XGpioPs psGpioInstancePtr;

XGpioPs_Config* GpioConfigPtr;

int iPinNumber= 8; //DS12连接的是MIO8

u32 uPinDirection = 0x1; //1表示输出, 0表示输入

int xStatus;

//--MIO的初始化

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

if(GpioConfigPtr == NULL)

return XST_FAILURE;

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr,

GpioConfigPtr->BaseAddr);

if(XST_SUCCESS != xStatus)

print("

本文详细介绍了Xilinx ZYNQ 7000系列芯片的三种GPIO使用方式:MIO、EMIO和AXI_GPIO。MIO不消耗PL资源,EMIO消耗PL管脚资源,而AXI_GPIO通过M_AXI_GPIO接口控制PL,同时消耗管脚和逻辑资源。通过具体示例展示了如何在Vivado和SDK中配置与使用这三种GPIO,包括管脚约束和功能验证。

本文详细介绍了Xilinx ZYNQ 7000系列芯片的三种GPIO使用方式:MIO、EMIO和AXI_GPIO。MIO不消耗PL资源,EMIO消耗PL管脚资源,而AXI_GPIO通过M_AXI_GPIO接口控制PL,同时消耗管脚和逻辑资源。通过具体示例展示了如何在Vivado和SDK中配置与使用这三种GPIO,包括管脚约束和功能验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?