SPI 接口作为slave的代码,Verilog编写注释详细,功能正确;

ID:6880643922417161

南朝划水的莲雾

SPI(Serial Peripheral Interface)是一种常见的串行通信协议,广泛应用于嵌入式系统中。在嵌入式系统中,SPI接口通常被用作从设备和主设备之间进行通信的桥梁。本文将详细介绍如何使用Verilog编写SPI接口作为从设备的代码,并对其功能进行正确性验证。

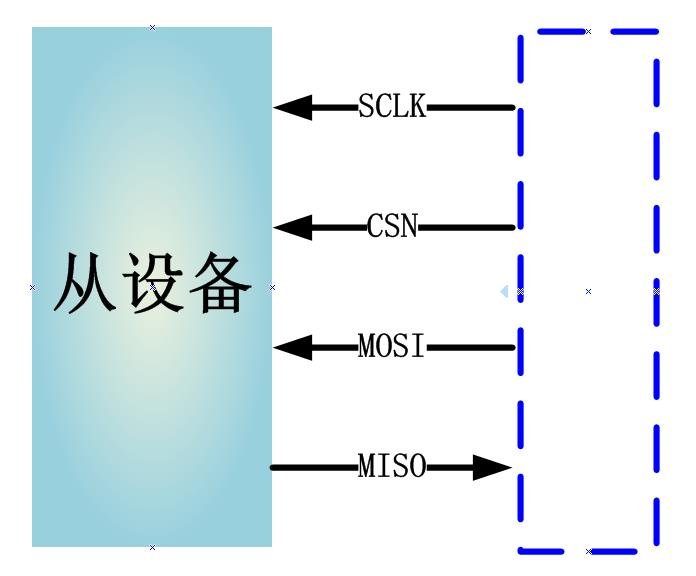

首先,我们需要了解SPI接口的基本原理。SPI接口由一个主设备和一个或多个从设备组成。主设备负责控制通信的时序,从设备则负责根据主设备的控制信号进行数据传输。在SPI接口的通信过程中,主设备通过时钟信号(SCLK)来驱动数据的传输,同时通过输出使能信号(SS)来选择要与从设备进行通信的目标。数据在主设备和从设备之间通过主设备的输出引脚(MOSI)和从设备的输入引脚(MISO)进行传输。

在Verilog中,我们可以通过定义输入和输出信号的方式来实现SPI接口的从设备功能。首先,我们需要定义输入信号,包括时钟信号(SCLK)和主设备输出使能信号(SS)。同时,我们还需要定义输出信号,包括主设备输出引脚(MOSI)和从设备输入引脚(MISO)。通过对这些信号进行适当的赋值和时序控制,我们可以实现从设备对主设备的响应。

在编写SPI接口作为从设备的Verilog代码时,我们需要对时钟信号进行同步,并根据主设备输出使能信号的状态进行数据传输的选择。首先,我们可以使用一个时钟域同步器来保证时钟信号的稳定性。接着,我们可以在时钟的上升沿或下降沿触发数据传输的操作。在数据传输过程中,我们需要根据主设备输出使能信号的状态来选择是否接收数据。如果主设备输出使能信号处于使能状态,即表示主设备要向从设备传输数据,我们可以将主设备输出引脚(MOSI)上的数据进行接收。反之,如果主设备输出使能信号处于禁用状态,即表示主设备不需要向从设备传输数据,我们可以将从设备输入引脚(MISO)设置为一个默认值。

在编写SPI接口作为从设备的Verilog代码时,我们还需要注意对输入和输出信号的赋值范围。为了保证数据传输的正确性,我们可以使用合适的位宽来定义输入和输出信号。同时,我们可以通过使用适当的寄存器来保存接收到的数据,以备将来使用。

通过以上的编码实现,我们可以在Verilog中实现SPI接口作为从设备的功能,并通过详细的注释对代码进行解释。这样的代码不仅能够保证功能的正确性,还能提高代码的可读性和可维护性。在代码编写完成后,我们可以使用Verilog仿真工具对代码进行功能验证,以确保代码的正确性。

综上所述,本文以Verilog编写SPI接口作为从设备的代码为主题展开了论述。通过对SPI接口原理的介绍和Verilog代码的编写,我们可以实现从设备对主设备的正确响应。通过详细的注释和功能验证,我们能够确保代码的准确性和可靠性。这样的技术分析文章能够为嵌入式系统中使用SPI接口进行通信的开发者提供参考和指导,进一步提升他们的工作效率和代码质量。

相关的代码,程序地址如下:http://imgcs.cn/643922417161.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?