分页机制

分页(paging)内存管理方案允许进程的物理地址空间可以是非连续的。分页避免了将不同大小的内存块匹配到交换空间上这样的麻烦,许多内存管理方案都有这个问题。各种形式的分页由于其优越性,因此常为绝大多数操作系统所采用。

传统上,分页支持一直是由硬件来处理的。然而,最近的设计是通过将硬件和操作系统相配合来实现分页。

基本原理

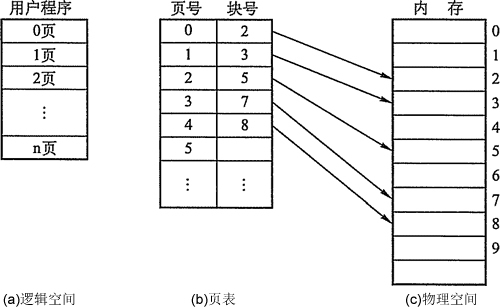

分页方法将物理内存分为固定大小的帧(frame);将逻辑内存分为对应大小的页(page)。当需要执行进程时,其页从备份储存中调入到可用的内存帧中。

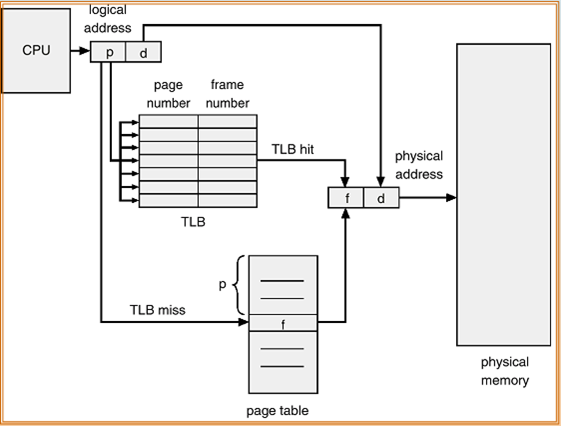

由CPU生成的每个地址分为两个部分:页号和页偏移。页号作为页表的索引。页表包含每页所在物理内存的基地址,这些基地址与页偏移的组合就形成了物理地址。

分页的一个重要特点是用户视角的内存和实际物理内存的分离。用户程序将内存作为一整块来处理,而且他只包括只一个进程。事实上,一个用户程序与其他程序一起,分布在物理内存上。用户视角的内存和实际的物理内存的差异是通过地址转换硬件协调的。逻辑地址转变成物理地址。这种映射是用户所不知道的,但是受操作系统所控制

硬件中的分页

分页单元(paging unit)把线性地址转换成物理地址。其中的一个关键任务是把所请求的访问类型与线性地址的访问权限相比较,如果这次内存访问是无效的,就产生一个缺页异常。

分页单元把所有的RAM分成固定长度的页框(page frame)。每一个页框包含一个页,也就是说一个页框的长度与一个页的长度一致。页框是主存的一部分,因此也是一个储存区域。页框是一个数据块,而页是数据块及其所存储的内容。

把线性地址映射到物理地址的数据结构称为页表(page table)。页表存放在主存中,并在启用分页单元之前必须由内核对页表进行适当的初始化。从80386开始,所有的80x86处理器都支持分页,它通过设置cr0寄存器的PG标志启用。当PG=0时,线性地址就被解释成物理地址。

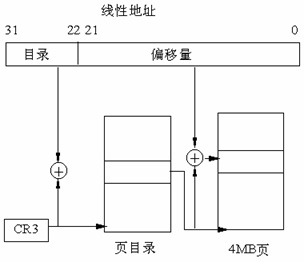

常规分页

从80386起,Intel处理器的分页单元处理4KB的页。

CR0寄存器中的PG标志(位31)——开启分页

32位的线性地址被分成3个域:

Director(目录)

最高10位

Table(页表)

中间10位

Offset(偏移量)

最低12位

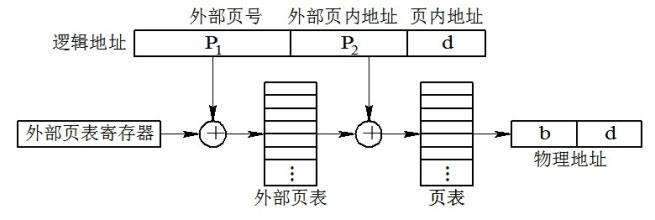

线性地址的转换分两步完成,每一步都基于一种转换表,第一种转换表称为页目录表(page directory),第二种转换表称为页表(page table)。使用这样的二级页表相比与简单的一级页表要减少很多内存空间。

拓展分页

从Pentium模型开始,80x86微处理器引入了拓展分页(extended paging),它允许页框大小为4MB而不是4KB。拓展分页用于把大段连续的线性地址转换成相应的物理地址,在这些情况下,内核可以不用中间页表进行地址转换,从而节省内存并保留TLB项。

物理地址拓展(PAE)分页机制

处理器所支持的RAM容量受连接到地址总线上的地址管脚数量限制。早期的Intel使用32位物理地址。这样应该可以安装4GB的RAM;而实际上,由于用户进程线性地址空间的需要,内核不能直接对1GB以上的RAM进行寻址。

Intel通过在它的处理器上把管脚数从32增加到36来满足这些需求。不过只有引入一种新的分页机制把32位线性地址转换为36位物理地址才能使用所增加的物理地址。从Pentium Pro处理器开始,Intel引入一种叫做物理地址拓展(Physical Address Extension,PAE)的机制。

CR4寄存器中的PAE标志(位5)置位,开启PAE分页机制。

分页机制也要做相应更改:

64GB的RAM被分成 224 个页框,页表的物理地址字段从20位拓展到了24位,总和数到达了36位,则页表大小从32位变为64位,结果一张4KB的页表所包含的项从1024减少到512项。

引入一个被称作页目录指针(Page Directory Pointer Table,PDPT)的页表新级,它由4个64位表项组成。

cr3寄存器包含一个27位的页目录指针表基地址段。

当把线性地址映射到4KB页时,32位线性地址按如下方式解释:

cr3

指向一个PDPT

位31-30

指向PDPT中4个项中的一个

位29-21

指向页目录中512个项中的一个

位20-12

指向页表中512项中的一个

位11-0

4KB页中的偏移量

当把线性地址映射到2MB的页时,32位线性地址按如下方式解释:

cr3

指向一个PDPT

位31-30

指向PDPT中4个项中的一个

位29-21

指向页目录中512个项中的一个

位20-0

2MB页中的偏移量

一旦cr3被设置,就可能寻址高达4GB RAM。使用PAE的主要问题是线性地址仍然是32位字长,这就迫使编程人员用同一线性地址映射不同的RAM区。

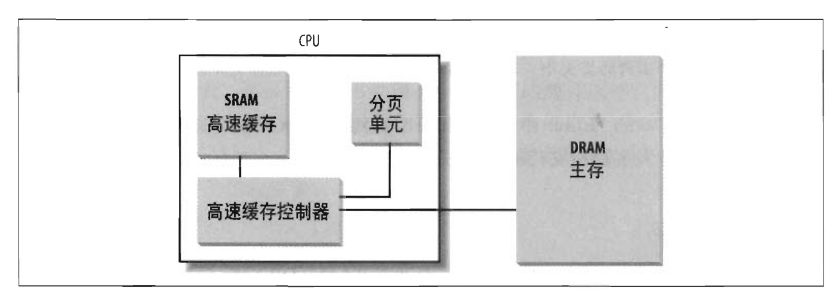

硬件高速缓存

为了缩小CPU与RAM之间的速度不匹配,引入了硬件高速缓存内存(hardware cache memory)。硬件高速缓存基于著名的局部性原理(locality principle),该原理即使用于程序结构也适用于数据结构。

局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。

三种不同类型的局部性:

时间局部性(Temporal Locality):如果一个信息项正在被访问,那么在近期它很可能还会被再次访问。

空间局部性(Spatial Locality):在最近的将来将用到的信息很可能与现在正在使用的信息在空间地址上是临近的。

顺序局部性(Order Locality):在典型程序中,除转移类指令外,大部分指令是顺序进行的。顺序执行和非顺序执行的比例大致是5:1。此外,对大型数组访问也是顺序的。

80x86体系结构引入了一个叫行(line)的新单位。行由几十个连续的字节组成,他们以脉冲突发模式(burst mode)在慢速DRAM和快速的用来实现高速缓存的片上静态RAM(SRAM)之间传送,用来实现高速缓存。

高速缓存单元插在分页单元和主内存之间。他包含一个硬件高速缓存内存(hardware cache memory)和一个高速缓存控制器(cache controller)。高速缓存内存存放内存中真正的行。

当访问一个RAM储存单元时,CPU从物理地址中提出子集的索引号并把子集中所有行的标签与物理地址的高几位相比较。如果发现某一行的标签与这个物理地址的高位相同,则CPU命中一个高速缓存(cache hit),否则,高速缓存没有命中(cache miss)。

转换后援缓冲器(TLB)

除了高速缓存之外,80x86处理器还包含了另外一个称为转换后援缓冲器(Translation Lookaside Buffer)的高速缓存用于加快线性地址的转换。当一个线性地址第一次使用时,通过慢速访问RAM中的页表计算出相应的物理地址。同时物理地址被存放在一个TLB表项中,以便以后对同一个线性地址的引用可以快速得到转换。

在多处理器系统中,每个CPU都有自己的TLB。与硬件高速缓存相反,TLB中的对应不必同步,这时因为运行在现有CPU上的进程可以使同一线程地址与不同的物理地址发生关系。

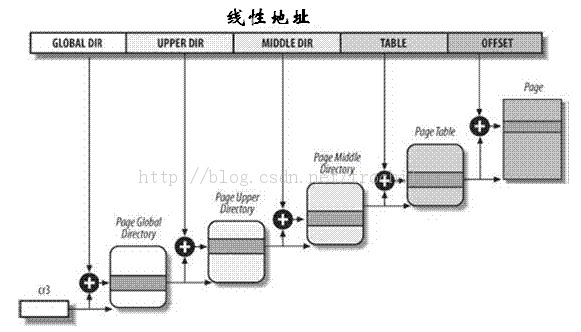

Linux中的分页

Linux采用了 一种同时适用于32位和64位系统的普通分页模型。从2.6.11版本开始,采用了四级分页模型。

页全局目录包含若干页上级目录的地址,页上级目录又依次包含若干页中间目录的地址,而页中间目录又包含若干页表的地址。每一个页表指向一个页框。线性地址因此被分成五个部分。

启用了物理地址拓展的32位系统使用了三级页表。Linux的页全局目录对应的80x86的页目录指针表(PDPT),取消了页上级目录,页中间目录对应80x86的页目录,Linux的页表对应80x86的页表。

670

670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?