FPGA 1553B IP

典型的 Core1553BRM 系统需要连接到外部 CPU,用于设置内核寄存器和初始化

内存中的数据表。

为了便于系统集成,Core153BRM 与 SuMMITTM 寄存器兼容

Aeroflex Inc. 的 1553B 设备系列

外部存储块用于存储接收和发送的数据。

这个内存可以是内部的或外部的

FPGA,取决于目标系列。

核心通过外部 1553 与 1553 总线接口

收发器和变压器。

提供三个版本的内核:

允许使用 Actel Libero 集成设计环境 (IDE) 或

模型模拟

提供混淆 RTL 和预编译测试平台的混淆版本

可完全访问源代码的 RTL 版本

可直接移植使用

ID:68200679854873069

小小小fpga

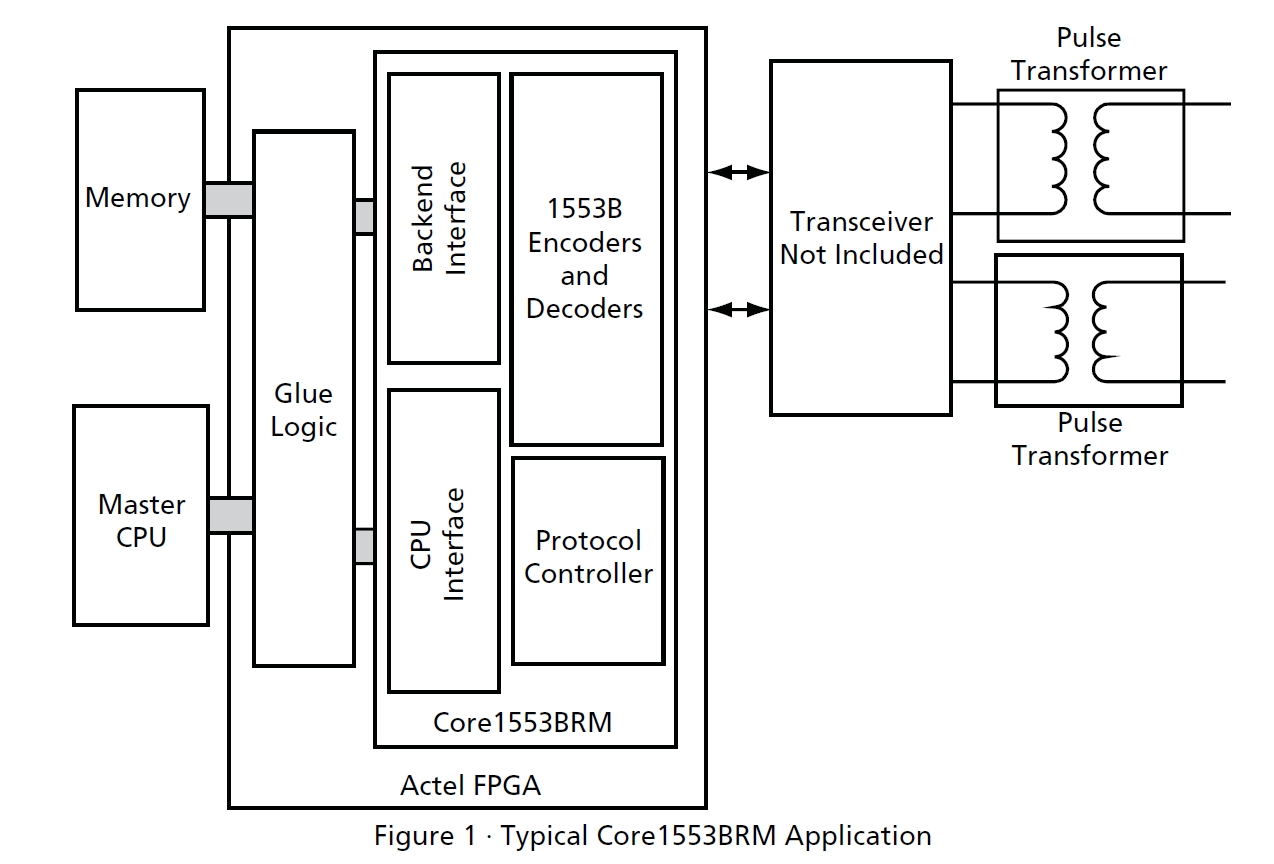

FPGA 1553B IP(下文简称IP)是一种常用的核心架构,在Core1553BRM系统中起到了关键的作用。这个系统需要与外部的CPU进行连接,以便用于设置内核寄存器和初始化内存中的数据表。为了方便系统集成,Core1553BRM与Aeroflex Inc.的1553B设备系列的SuMMITTM寄存器兼容。

在IP中,外部存储块被用于存储接收和发送的数据。这个存储块可以是内部的或者外部的FPGA,具体取决于目标系列。此外,核心通过外部的1553与1553总线接口相连,并且通过收发器和变压器进行通信。

这个IP提供了三个版本的内核,以满足不同的需求:

-

第一个版本允许使用Actel Libero集成设计环境(IDE)或模型模拟进行设计。这种版本适合那些希望通过模拟和仿真来验证系统功能的开发者。通过Libero集成设计环境,开发者可以方便地配置和调试IP,以满足系统的需求。

-

第二个版本是混淆版本,提供了混淆RTL和预编译测试平台。这种版本适合那些希望在保护知识产权的同时,快速进行系统验证和测试的开发者。混淆RTL版本通过对RTL代码进行混淆处理,使得代码难以被逆向工程分析,从而保护了核心的技术细节。

-

第三个版本是RTL版本,提供了完全访问源代码的权限。这种版本适合那些希望对IP进行二次开发和扩展的开发者。通过访问源代码,开发者可以深入了解IP的实现细节,并根据自己的需求进行修改和优化。

无论选择哪个版本,这个IP都具备直接移植使用的能力。这意味着开发者可以将IP直接应用到目标系统中,无需进行大量的修改和优化。这让开发者能够更加高效地进行系统集成和部署。

总的来说,FPGA 1553B IP是一个功能强大的核心架构,可以满足Core1553BRM系统的需求。通过与外部CPU的连接,它能够灵活地设置内核寄存器和初始化内存中的数据表。同时,它的三个版本也为开发者提供了不同的选择,以适应不同的开发需求。无论是使用Actel Libero集成设计环境还是混淆RTL版本,还是直接访问源代码的RTL版本,开发者都能够利用这个IP来加快系统开发的进度。综上所述,FPGA 1553B IP是一项具有广泛应用前景的技术,值得开发者深入研究和应用。

相关的代码,程序地址如下:http://matup.cn/679854873069.html

698

698

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?