本文摘抄改编自http://blog.csdn.net/findaway123/article/details/20727017

权当学习与交流使用,谨向findaway兄致以敬意。

TMS320F28335总共有2个McBSP(多通道缓冲串口)接口。每个接口有六根引脚, 分别是:

MCLKX(发送时钟引脚)

MCLKR(接收时钟引脚)

MFSX(发送帧同步引脚)

MFSR(接收帧同步引脚)

MDX(数据发送)

MDR (数据接收)

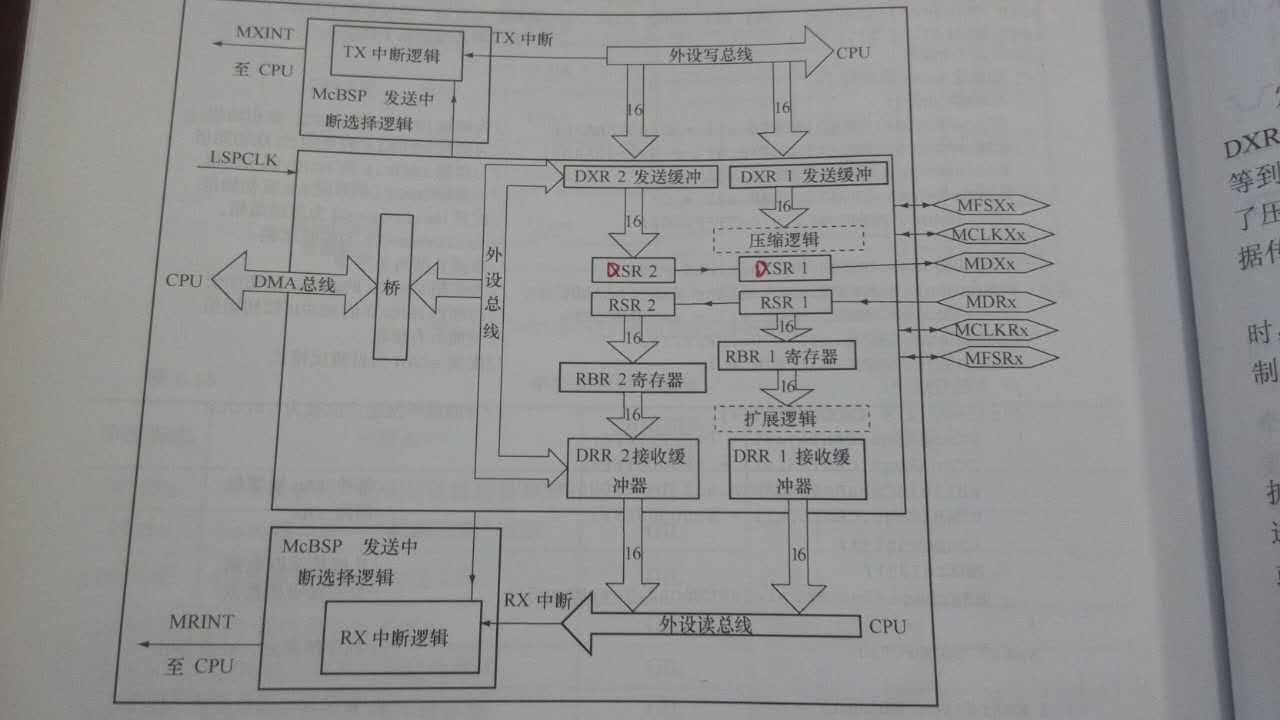

一.结构原理

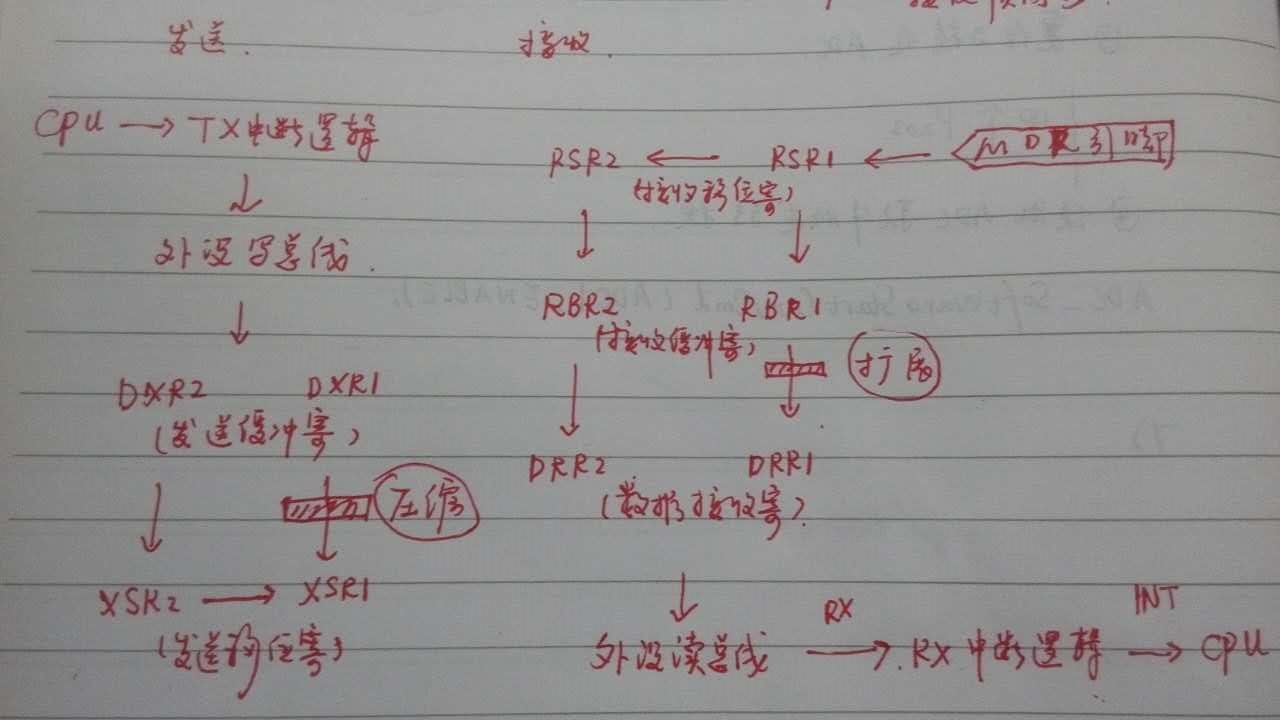

二.McBSP的数据传输过程

CPU和DMA控制器通过外设总线与MCBSP进行通信。

当发送数据时,CPU和DMA将数据写入数据发送寄存器(DXR1,DXR2),接着复制到发送移位寄存器(XSR1,XSR2),通过发送移位寄存器输出至DX引脚。

同样,当接收数据时,DR引脚上接收到的数据先移位到接收移位寄存器(RSR1,RSR2),接着复制到接收缓冲寄存器(RBR1,RBR2)中,RBR再将数据复制到数据接收寄存器(DRR1,DRR2)中,由CPU或DMA读取数据。这样就可以同时进行内部和外部的数据采集。

由结构原理图可知,发送缓冲寄存器DXR和接收缓冲寄存器DRR通过外设总线直接和DMA总线连接。(外设之中,有ADC、McBSP、ePWM通过DMA总线连接至RAM)

简化之:

注:

1)MCBSP的接收操作是三缓冲(triple buffered)的,而发送操作是双缓冲(double buffered)的。寄存器值的使用取决于串行字长是否符合16bits。

如果字长为16bits或小于16bits(8bits、12bits),则只须使用一套寄存器(RSR1,RBR1,DRR1,DXR1,XSR1)。

如果字长大于16bits,则需要使用两套寄存器(RSR1/2,RBR1/2,DRR1/2,DXR1/2,XSR1/2)。

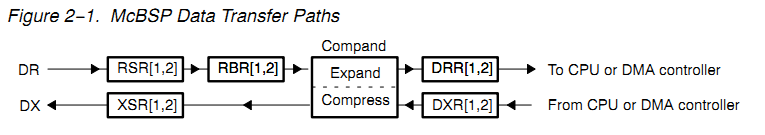

2)数据的压缩和扩展

MCBSP的压缩和扩展硬件可以将数据按照μ-律和A-律格式进行压缩和扩展。其示意图如上:

接收时,8位压缩过的数据被扩展成16位左对齐的形式放在DRR1中,RJUST位被忽略。

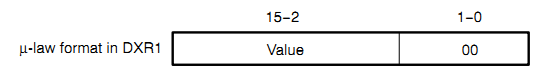

发送时,a.对于使用μ-律压缩和扩展的数据,要保证其在DXR1中进行14位左对齐,如下图:

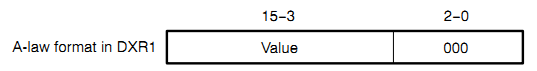

b.对于使用A-律压缩和扩展的数据,要保证其在DXR1中进行13位左对齐,如下图:

三.时钟

两个时钟信号可来自内部或外部。

一般上升沿发送,下降沿接收。高位在前,低位在后。

四.McBSP串口初始化

//以下设置适用于数据回送模式,也即自发自收

void mcbsp_init()

{

/*----------------------------------------

1.使帧同步逻辑、采样率发生器、接收器和发送器处于复位状态,即FRST=GRST=XRST=RRST=0

----------------------------------------*/

McbspaRegs.SPCR2.bit.FRST=0;

McbspaRegs.SPCR2.bit.GRST=0;

McbspaRegs.SPCR2.bit.XRST=0;

McbspaRegs.SPCR1.bit.RRST=0;

/*----------------------------------------

2. 控制寄存器配置

a.串行端口控制寄存器SPCR1&SPCR2

b.接收控制寄存器RCR1&RCR2

c.发送控制寄存器XCR1&XCR2

d.采样率发生寄存器SRGR1&SRGR2:采样率发生寄存器用于产生时钟信号CLKG和帧同步信号FSG

1).SRGR2.bit.CLKSM+PCR.bit.SCLKME共同确定输入时钟源,本次为01内部输入时钟LSPCLK

2). f clkg=f 输入时钟/(SRGR1.bit.CLKGDV+1)

FSG周期:每(SRGR2.bit.FPER+1 )个CLKG周期 输出一个FSG脉冲

----------------------------------------*/

McbspaRegs.SPCR2.all=0x0000;

McbspaRegs.SPCR1.all=0x8000; //DLB=1,表示数字回环测试

McbspaRegs.RCR2.all=0x0001;

McbspaRegs.RCR1.all=0x0;

McbspaRegs.XCR2.all=0x0001;

McbspaRegs.XCR1.all=0x0; //收发都是单向帧,每帧1个字,8位字长,不压扩,1位数据延迟

McbspaRegs.SRGR2.all=0x3140;

McbspaRegs.SRGR1.all=0x010f;

McbspaRegs.MCR2.all=0x0;

McbspaRegs.MCR1.all=0x0;

McbspaRegs.PCR.all=0x0A00;//由采样率发生器提供发送时钟和发送帧同步,照样上面。另外后4位对极性进行了配置

/*-----------------------------------------

添注:采用中断时,SPCR1.bit.RINTM或者SPCR2.bit.XINTM+MFFINT.bit.RINT(XINT)要设置好,进入中断后读DRR或写DXR

-----------------------------------------*/

McbspaRegs.MFFINT.bit.XINT = 1;

McbspaRegs.MFFINT.bit.RINT = 1;

/*----------------------------------------

3. 等待2个时钟周期及以上,保证内部的同步

a.设置GRST=1,采样率发生器工作

等待2个时钟周期及以上,保证内部的同步

b.设置RRST=XRST=1,允许发送和接收数据

c.若使用内部帧同步逻辑,则需将FRST=1

----------------------------------------*/

//省略delay_loop();

// Wait at least 2 SRG clock cycles

McbspaRegs.SPCR2.bit.GRST=1;

//省略delay_loop();

// Wait at least 2 SRG clock cycles

McbspaRegs.SPCR2.bit.XRST=1;

McbspaRegs.SPCR1.bit.RRST=1;

McbspaRegs.SPCR2.bit.FRST=1;

}

4560

4560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?