1、配置从设备(MCBSP)的数据格式寄存器:

1、配置从设备(MCBSP)的数据格式寄存器:

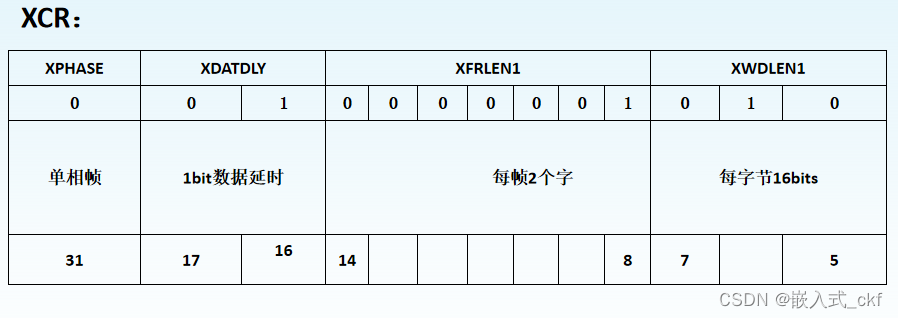

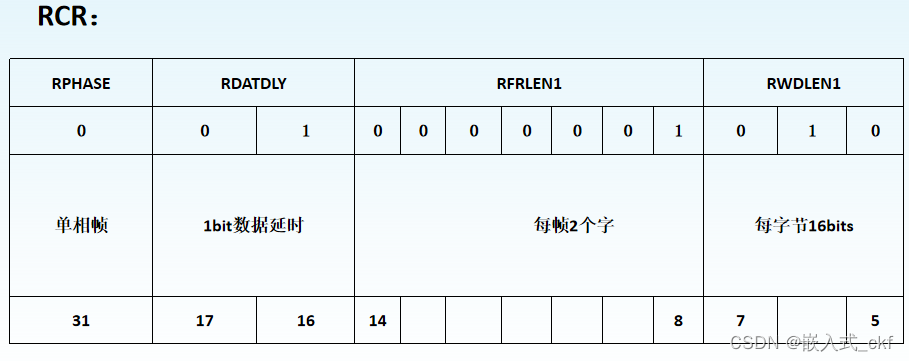

(1)与AIC33相同 单相帧,每帧2个数据单元(Element),每个数据单元16bit,1位延迟。具体配置如下表:

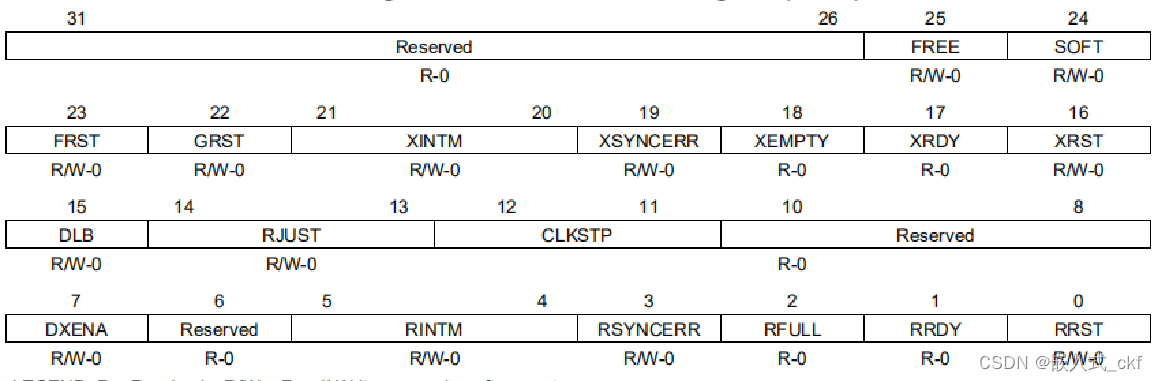

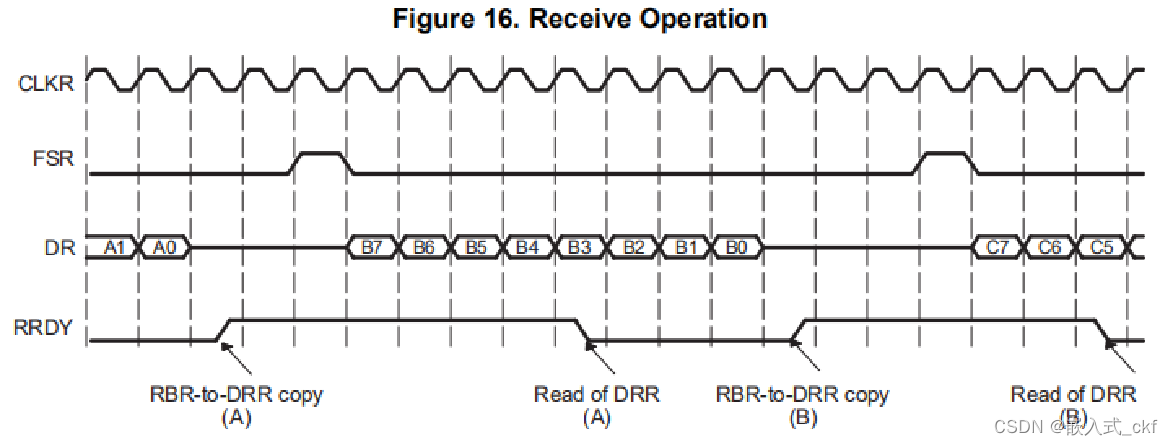

(2)采用右对齐、高位补零 一次完成读双声道数据:由RSR到RBR时,32bit逐位进入。 双声道数据从RBR到DRR分两次完成:每次16位。 时序图可看出DRR按照数据单元读取。

串口控制寄存器(SPCR)

RJUST:SPCR[14:13],接收符号扩展和对齐模式位.

RJUST = 0:在DRR中右对齐,MSB零填充

RJUST = 1:在DRR中右对齐,MSB符号扩展

RJUST = 2:在DRR中左对齐,LSB零填充

RJUST = 3:保留

数据的发送和接收过程

接收操作采取三级缓冲方式,发送操作采取两级缓冲方式

2、数据的接收过程

(1)DR-RSR

FSR有效后,接收数据到达DR后移位至RSR。

(2)RSR-RBR

完整数据单元(8、12、16、20、24或32位)接收完毕后,若接收缓冲寄存器(RBR)空,则将RSR复制到RBR中。

(3)RBR-DRR

DRR空(RRDY = 0),实现RBR-DRR,并(自动)设置RRDY = 1,表示数据准备好;

DRR数据准备好(RRDY = 1):CPU或EDMA可以读取; 当CPU或 EDMA 读取DRR数据后,(自动)设置RRDY=0(DRR空),具体如下:

RRDY = 1/0,表示DRR 有效/无效--(满/空)

RRDY = 1:DRR是满,DRR to CPU,结束后,设置RRDY = 0

RRDY = 0:DRR是空,RBR to DRR,结束后,设置RRDY = 1

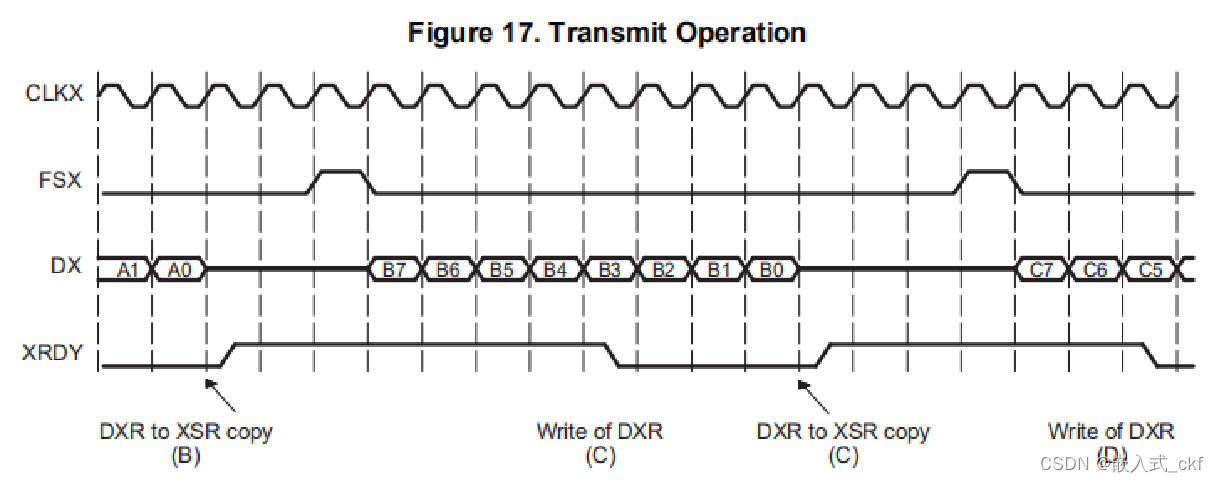

3、数据的发送过程

XRDY = 1/0,表示DXR 有效/无效--(空/满)

XRDY = 1:DXR是空,CPU to DXR,结束后,设置XRDY = 0

XRDY = 0:DXR是满,DXR to XSR,结束后,设置XRDY = 1

(1)CPU-DXR

DXR空(XRDY = 1):CPU或 EDMA 控制器可以写数据到DXR中 ;

当CPU或EDMA控制器写入DXR时,XRDY = 0(CPU停止访问)。

(2)DXR-XSR

在随后的CLKX下降沿,最后一个DXR-to-XSR拷贝操作后,XRDY = 1,表示DXR可以写入下一个待传输的数据。

当发生传输帧同步(检测到FSX),经过适当的数据延迟(XDATDLY设置)后,XSR将数据移出到DX管脚输出。

控制通道

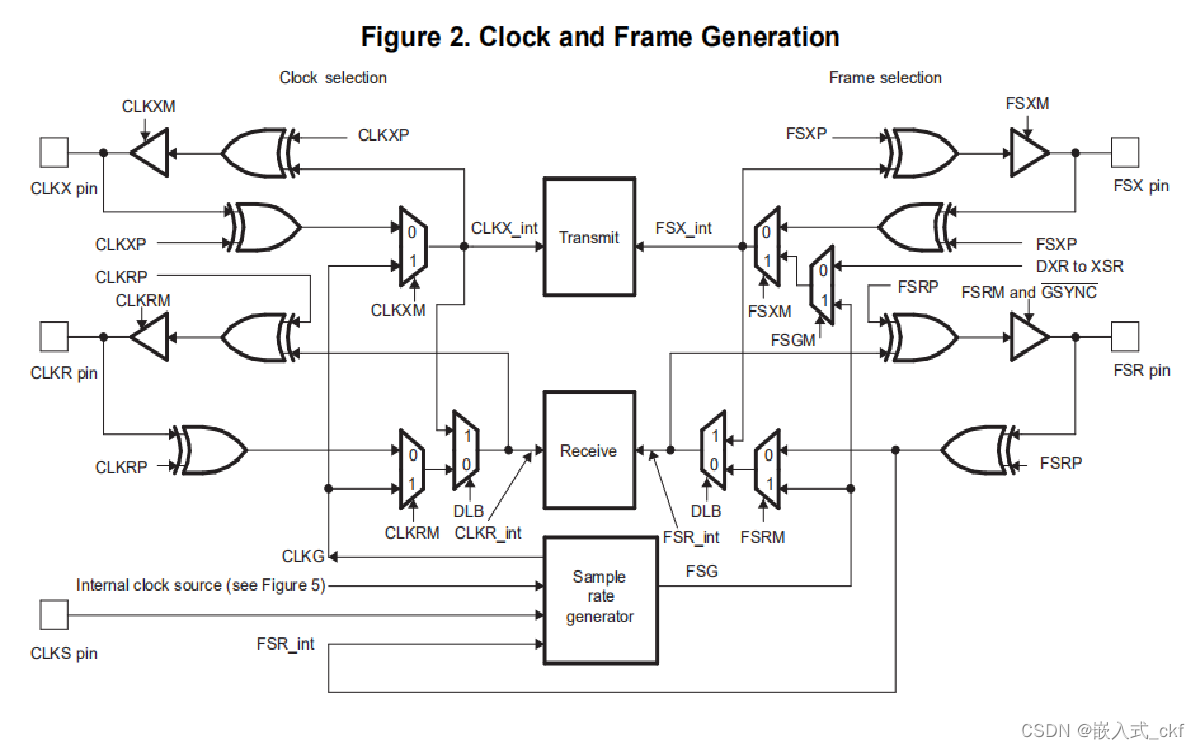

生成时钟和帧:

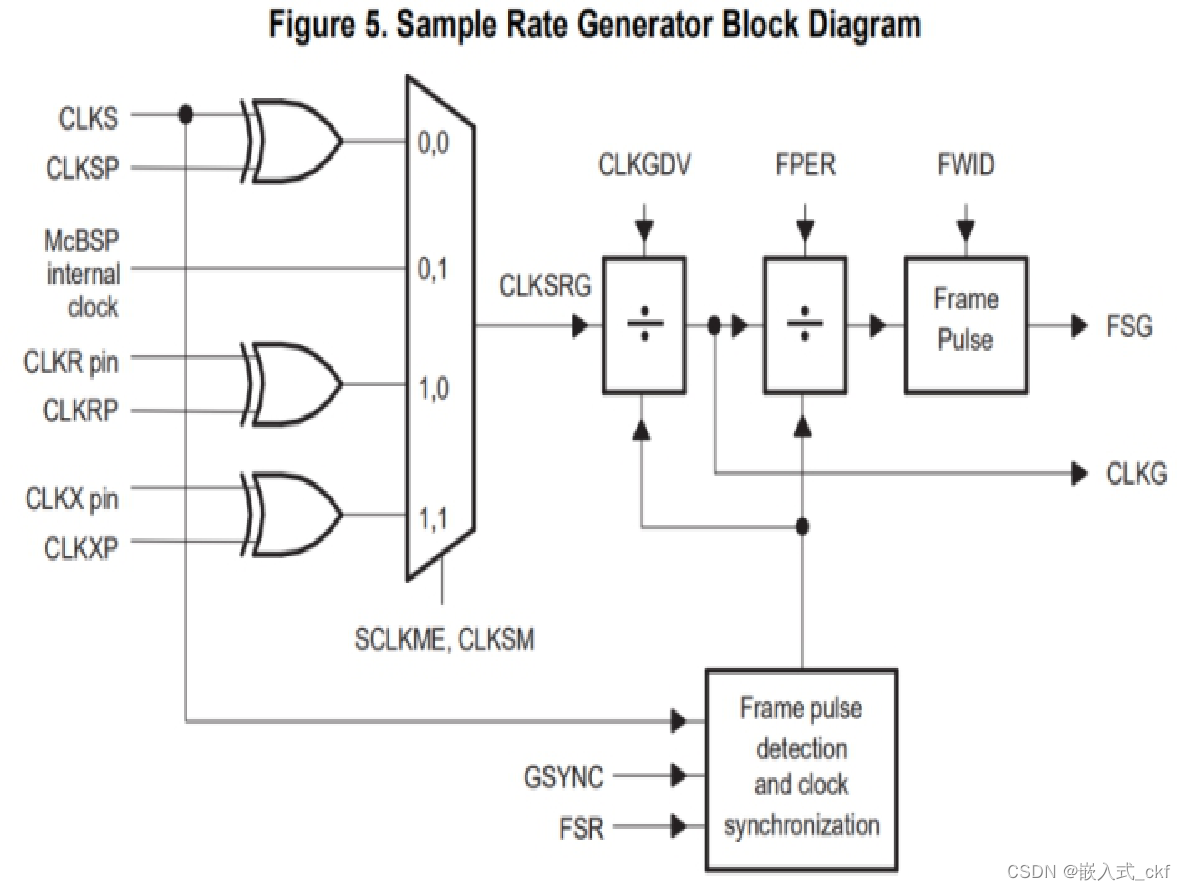

(1)采样率发生器

输入时钟:内部时钟源、CLKS、FSR_int

提供的数据时钟信号: 位时钟:CLKG)、帧时钟:FSG

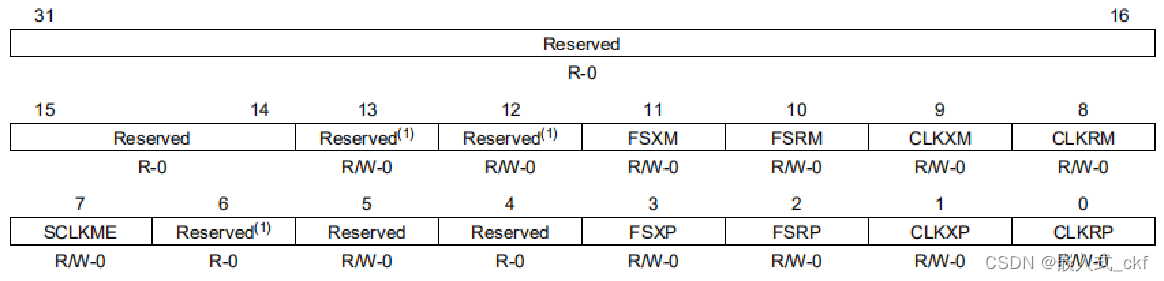

(2)发射、接收器使用的内部时钟:

内部时钟选择控制位: FS(R/X)M:选择FS(R/X)_int来自于FSG还是FS(R/X)_pin

FS(R/X)M = 0,FS(R/X)_int来自FS(R/X)_pin

FSRM = 1,FS(R/X)_int来自FSG FSXM = 1时,

FGSM = 0,FSX_int 由内部DXR-XSR提供(SPI主设备)

FGSM = 1,FSX_int 由内部FSG提供

CLK(R/X)M:选择CLK(R/X)_int来自于CLKG还是CLK(R/X)_pin

CLK(R/X)M = 0,CLK(R/X)_int来自CLK(R/X)_pin

CLK(R/X)M = 1,CLK(R/X)_int来自CLKG

(3)时钟极性控制位:

CLK(R/X)P:FS(R/X)P控制外部时钟信号的极性

(4)DLB 数据环路控制: 设置数字环路模式,主要用于串口功能测试,输入输出直接连接

DLB = 0,正常工作下,环路关闭

DLB = 1,使用数字回环模式,环路打开

工作模式配置:

时钟由外部提供 FSXM = FSRM = CLKRM = CLRXM =0

时钟由内部FSG提供 FSXM = FSRM = CLKRM = CLRXM =1 FSGM = 1

1、采样率发生器时钟源位:SCLKME:PCR[7]、CLKSM:SRGR[29]

选择内部时钟源: CLKSM = 1、SCLKME = 0

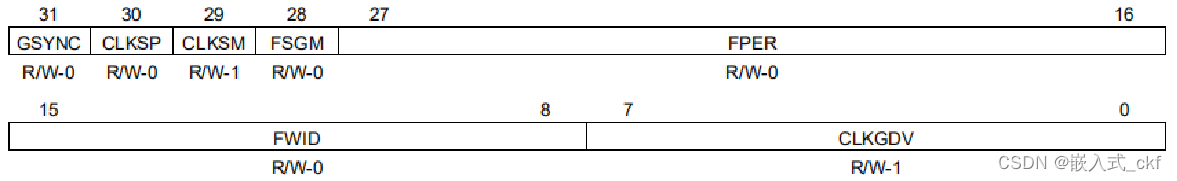

采样率发生器-结构:

二级分频器

第一级:生成时位钟CLKG,频率为:

CLKG frequency = Input clock frequency/(CLKGDV + 1)

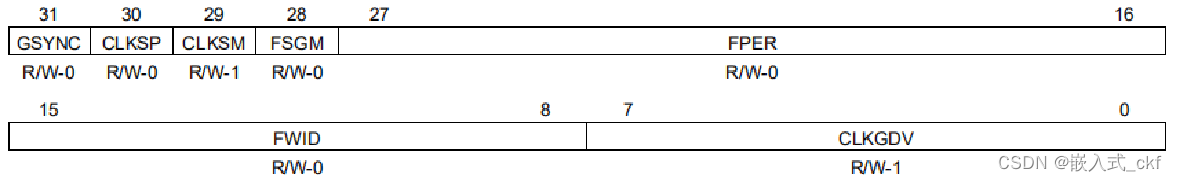

CLKGDV:SRGR[7:0],时钟分频系数(0~255)

Input clock frequency 即可为CLKSRG/SYSCLK3

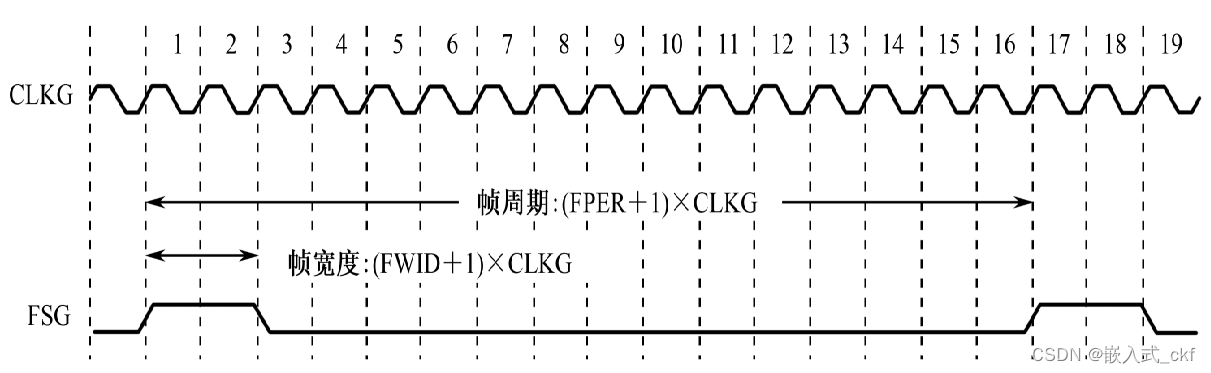

第二级:生成帧时钟FSG,频率为: FSG frequency =CLKG/(FPER + 1)

FPER:SRGR[27:16],时钟分频系数(0~4095)

FWID:SRGR[15:8],设置帧宽(0~255)

第二级分频器的帧周期和帧宽度

采样率发生寄存器(SRGR)的相关配置

CLKGDV:SRGR[7:0],二级分频数,生成CLKG 取值范围:0~255

FPER:SRGR[27:16],帧周期值(3级分频数)生成FSG, 取值范围:0~4095

FWID:SRGR[15:8],帧宽度值,FSG的脉冲宽度 取值范围:0~255

CLKS时钟极性边沿选择位:CLKSP

当CLKSM=0、SCLKME=0时,选择外部时钟(CLKS)来驱动采样率发生器的时钟分频器,此时CLKSP,决定了CLKS时钟极性

CLKSP:SRGR[30],CLKS时钟极性边沿选择位

CLKSP = 0:CLKS的上升沿将生成CLKG和FSG

CLKSP = 1:CLKS的下降沿生成CLKG和FSG。

时钟同步位:GSYNC

当选择外部时钟(CLKS)来驱动采样率发生器时,GSYNC位可用于配置CLKG相对于CLKS的时间。

GSYNC = 0:CLKG自由运行。

GSYNC = 1:CLKG运行,但CLKG需要重新同步,并且只有在检测到FSR后才产生帧同步信号(FSG)。 由于周期是由外部帧同步脉冲决定的,和帧周期(FPER)也没关系。

当GSYNC = 1:满足以下条件,发送器可以与接收器同步

FSX由FSG驱动

FSGM = 1

FSXM = 1

采样率发生器时钟应驱动发送和接收比特时钟

CLKRM = 1

CLKXM = 1

即CLK(R/X)管脚不由任何其他源驱动。

FGSM:SRGR[28],采样率生成器发送帧同步模式位:

仅在PCR中的FSXM = 1帧时使用,

FGSM = 0:在每个DXR-XSR时,生成发送帧同步信号(FSX)

当FSGM = 0时,将忽略FWID位和FPER位。

FGSM = 1:FSX由FSG驱动。

6125

6125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?