S3C2440有两种启动方式:NORFLASH启动与NANDFLASH启动;但一般都只从NANDFLASH启动,既然是从这个地方启动,那必须具备两个条件:

1 这个里面必须得有程序

2 必须得有内存去跑这段程序

第一个条件,我们必须通过JTAG下载程序到NANDFLASH,假设下载了一个LED测试程序在里面了;

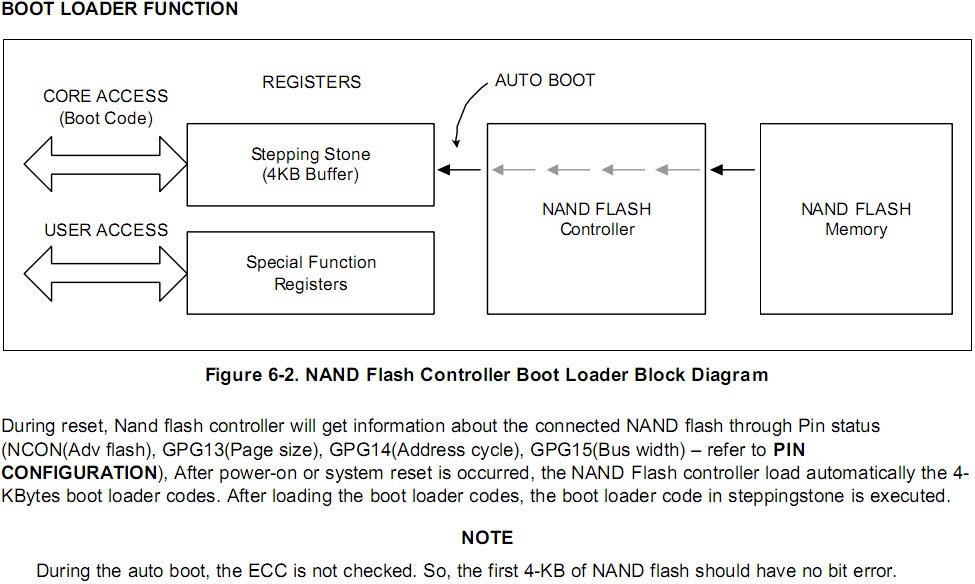

第二个条件,要跑这段程序必须有内存,可这个时候SDRAM还没有初始化,不能跑,怎么办?S3C2440里面有一个4k空间的SRAM,当芯片复位的时候会通过外部引脚首先判断使用哪种启动方式,如果是NANDFLASH启动方式,S3C2440的Nand Flash控制器有一个特殊的功能,在S3C2440上电后,Nand Flash控制器会自动的把Nand Flash上的前4K数据搬移到4K内部SRAM中,(此内部RAM被称为Steppingstone)并把0X00000000设置内部RAM的起始地址,CPU从内部RAM的0X00000000位置开始启动。这个过程不需要程序干涉。芯片怎么做到没有NANDFLASH驱动就能够读取前4K代码呢?在最后会讲。

上面的两个条件都满足了,程序可以在4K SRAM里面自动跑起来了。但只能是4K的代码,大于4K怎么办?那就只能在SDRAM去跑了,这就需要满足下面条件:

1 SDRAM必须要初始化

2 有一段代码把NANDFLASH里面的程序搬到SDRAM里面去运行

上面的两个条件都需要运行程序,就只能在SRAM里面运行,所以程序的前面4k的代码必须完成这两项工作,在完成了这两项工作后从SRAM跳转到SDRAM里面执行余下的工作;这样就实现了程序从NANDFLASH启动了。但程序是如何从SRAM跳转到SDRAM接着去执行的呢?

启动代码最开始是这样的:

@*************************************************************************

@ File:head.S

@ 功能:设置SDRAM,将程序复制到SDRAM,然后跳到SDRAM继续执行

@*************************************************************************

.equ MEM_CTL_BASE, 0x48000000

.equ SDRAM_BASE, 0x30000000

.text

.global _start

_start:

bl disable_watch_dog @ 关闭WATCHDOG,否则CPU会不断重启

bl memsetup @ 设置存储控制器

bl copy_steppingstone_to_sdram @ 复制代码到SDRAM中

ldr pc, =on_sdram @ 跳到SDRAM中继续执行

on_sdram:

ldr sp, =0x34000000 @ 设置堆栈

bl main

halt_loop:

b halt_loop

首先其他的都先不管,这里只关注bl指令与ldr指令,这两个指令的区别:

bl :位置无关码 -- 跳转位置与启动代码的链接地址无关

ldr:位置相关码 --跳转位置与链接地址相关

S3C2440 的SDRAM起始地址为0x3000,0000,最开始运行启动代码,所以启动代码的连接地址为0x3000,0000,这个地址是在编译链接操作的时候指定的,在makefile里面;

当执行bl的时候,跳转地址跟SDRAM链接地址无关(当前指令在SRAM内地址),这个地址还是本来的地址范围,SRAM的范围,所以还是在SRAM里面跳转。

当执行ldr的时候,跳转地址跟SDRAM连接地址有关,这里跳转到0x3000,0000+当前指令在SRAM内地址,这个地址已经是SDRAM的地址范围了,所以完成跳转。

就这样理解吧,如果要详细的理解,需要分析启动代码的反汇编文件,理解起来更加清晰。

下面再把整个过程总结一下:

1 上电复位判断从NANDFLASH启动后,芯片自动复制NANFLASH前4K内容到SRAM,(这时候SDRAM还没初始化)。再SRAM里面从0地址开始执行PC=0X00000000

2 此时PC执行到memsetup,初始化SDRAM

3 SDRAM初始化完成后,再执行

bl copy_steppingstone_to_sdram完成将NANDFLASH里面的代码复制到SDRAM里面(这里是复制的SRAM里面的代码到SDRAM,因为程序小于4K,SRAM里面就是所有的代码了;大于4K必须从NANDFLASH里面复制)

4 复制完成以后执行

ldr pc, =on_sdram这时候的跳转地址就跟链接地址有关了,本来是0x0000,0010,而SDRAM的连接地址是 0x3000,0000 ,所以跳转到 0x3000,0000+0x0000,0010 =0x3000,0010 。这样就完成了SRAM到SDRAM的跳转。

——————————————————————————————————————————————

前面说到那4K代码在系统复位后芯片自动复制带SRAM,这时候NANDFLASH驱动都没有,怎么实现读操作的呢?S3C2440的芯片手册是这样说的:

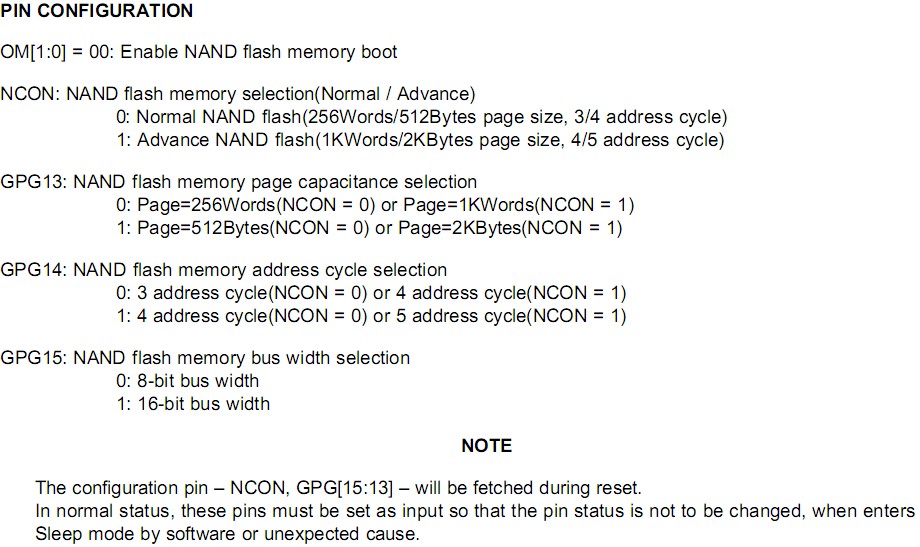

在系统复位期间,NANDFLASH控制器会去读取硬件PIN脚的电平来获取NANDFLASH信息从而对其进行对应的控制。

系统复位期间内部完成步骤:

1 读取OM【0:1】脚判断从哪里启动。

2 如果从NAND启动,读取 NCON, GPG[13-15] PIN脚信息

3 NAND控制器自动产生时序读取4K信息到SRAM

NANDFLASH启动的PIN脚设置说明如下:

本文介绍S3C2440处理器如何从NAND Flash启动,包括利用内部4K SRAM自动加载代码,SDRAM的初始化过程及代码如何从SRAM跳转至SDRAM执行。

本文介绍S3C2440处理器如何从NAND Flash启动,包括利用内部4K SRAM自动加载代码,SDRAM的初始化过程及代码如何从SRAM跳转至SDRAM执行。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?