版权说明:未经许可,不得转载

一.目的

1.了解FPGA的开发流程

2.学会使用XiLinxFPGA开发工具ISE

3.了解Digilent Anvyl实验平台的主要功能

4.掌握拨码开关和LED的使用

5.学习基本组合逻辑电路在FPGA上的开发、实现和验证方法

二.工具

1. Digilent Anvyl 开发板

2. 安装 ISE Design Suite软件的 PC 机一台

3. USB 数据线一根

三.简单上手实验

1.请采用门级和数据流级别描述方式建模,实现一个2输入与门。

2. 请采用行为级描述方式,实现一个4选1数据选择器,要求使用case语句和if_else语句分别实现。

3.设计并实现一个4输入电路,当大多数输入信号(3或4输入)为1时,输出为1,否则输出为0。

4. 设计并实现一个组合逻辑电路,要求:以SW0~SW3作为4个开关输出,控制LD0~LD1两个灯,完成集成照明控制逻辑,SW0是总开关; SW1开则LD0亮; SW2和SW3为双控开关,控制LD1。

四.实验步骤与结果分析

实验一:请采用门级和数据流级别描述方式建模,实现一个2输入与门。

设计过程:

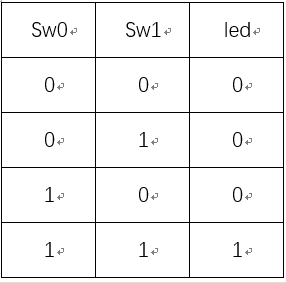

真值表

真值表

根据真值表可知:led = sw0 & sw1

门级描述方法源程序:

.v文件:

module led{

input[1:0] sw,

outputled

};

andU(led,sw[0],sw[1]);

endmodule

.ucf文件:

NET sw<0> LOC=V5;

NET sw<1> LOC=U4;

NET led LOC=W3;

数据流级描述方法源程序:

.v文件:

module led{

input[1:0] sw,

outputled

};

assignled = sw[0]&sw[1]

endmodule

.ucf文件:

NET sw<0> LOC=V5;

NET sw<1> LOC=U4;

NET led LOC=W3;

实验结果:

上图为1&1=1的结果

实验二:请采用行为级描述方式,实现一个4选1数据选择器,要求使用case语句和if_else语句分别实现。

设计过程:

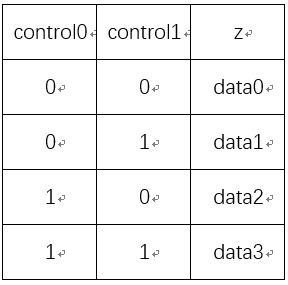

真值表

行为级描述方法源程序:

.v文件(case语句):

module test2{

input[1:0] control,

input[3:0] data

outputz

};

always@(controlor data)

begin

case(control):

0:z=data[0]

1:z=data[1]

2:z=data[2]

3:z=data[3]

end

endmodule

.v文件(if else语句):

module test2{

input[1:0] control,

input[3:0] data,

outputz

};

always@(controlor data)

begin

if(control==0)

z= data[0];

elseif(control==1)

z= data[1];

elseif(control==2)

z= data[2];

elseif(control==3)

z= data[3];

end

endmodule

.ucf文件(两种方式都相同):

NET control<0> LOC=V5;

NET control<1> LOC=U4;

NET data<0> LOC=V3;

NET data<1> LOC=P4;

NET data<2> LOC=R4;

NET data<3> LOC=P6;

NET z LOC=W3;

上图为四选一选择最右边的LED0

实验三:设计并实现一个4输入电路,当大多数输入信号(3或4输入)为1时,输出为1,否则输出为0。

设计过程:

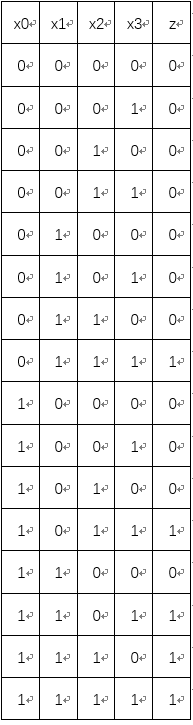

真值表

真值表

由真值表可画出如下卡诺图:

卡诺图

卡诺图

根据卡诺图可知:z =x0x1x3+x0x1x3+x0x2x3+x1x2x3

则数据流级描述方法程序如下:

.v文件:

module test3{

input[3:0] x,

outputz

};

assignz =(x[0]&x[1]&x[3])|(x[0]&x[1]&x[2])|(x[0]&x[2]&x[3])|(x[1]&x[2]&x[3])

endmodule

.ucf文件:

NET x<0> LOC=V5;

NET x<1> LOC=U4;

NET x<2> LOC=V3;

NET x<3> LOC=P4;

NET z LOC=W3;

实验结果(略)

实验四:设计并实现一个组合逻辑电路,要求:以SW0~SW3作为4个开关输出,控制LD0~LD1两个灯,完成集成照明控制逻辑,SW0是总开关; SW1开则LD0亮; SW2和SW3为双控开关,控制LD1。

设计过程:

真值表

真值表

根据真值表可画出如下卡诺图:

卡诺图

卡诺图

由卡诺图可知:

Z0 = x0x1

Z1 = x0(x2⊙x3)

则数据流级描述方法源程序如下:

.v文件:

module test4{

input[3:0] x,

output[1:0] z

};

assignz[0] = x[0]&x[1];

assignz[1] = x[0]&(x[2]~^x[3]);

endmodule

.ucf文件:

NET x<0> LOC=V5;

NET x<1> LOC=U4;

NET x<2> LOC=V3;

NET x<3> LOC=P4;

NET z<0> LOC=AB3;

NET z<1> LOC=AA4;

实验结果:

上图为输入为1011时,输出01

上图为输入为1111时,输入为11

五.实验总结

1.Verilog语言与所学的其他语言存在一定差异性,写的时候一定注意语法,不然很容易报错。

2.应该对每个小实验都新建一个文件夹来存放。因为不同实验中有些相同的变量如果放在同一文件夹中会引起冲突

对于以上实验若有不理解的地方,请参考相关实验说明文件

---------------------------@weekdawn 版权所有------------------------------------

1702

1702

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?