一、填空题:(每空1分,共 30 分)

1.第1代计算机的逻辑器件,采用的是( 1 );第2代计算机的逻辑器件,采用的是( 2 );第3代计算机的逻辑器件,采用的是集成电路;

2.程序设计语言一般可以分成三类:( 3 )、( 4 )和高级语言。

3.计算机由( 5 )、( 6 )、( 7 )、输入设备和输出设备5部分组成。

4.解释下列英文缩写的中文含义:CPU( 8 )、ALU( 9 )、SRAM( 10 )、DRAM( 11 )。

5.指令由( 12 )码和( 13 )码组成。

6.时序逻辑电路内存储信息的记忆元件是( 14 ),它是构成时序逻辑电路的基础。三态门是一种( 15 )逻辑电路。计数器是一种( 16 )逻辑电路。

7.浮点数加减运算过程一般包括( 17 )、尾数运算、规格化、( 18 )和判溢出等步骤。

8.双符号位补码表示时,为判断溢出,正数符号用( 19 ),负数符号用( 20 )。

9.从计算机指令系统设计的角度,可以将计算机分成复杂指令系统计算机CISC和( 21 )。

10.在程序执行过程中,控制器控制计算机的运行总是处于( 22 )、分析指令和( 23 )的循环之中。

11.控制信号的产生有微程序控制和( 24 )两种方法。

12.一条机器指令的执行可以与一段微指令构成的( 25 )相对应。微指令可以由一系列( 26 )组成。

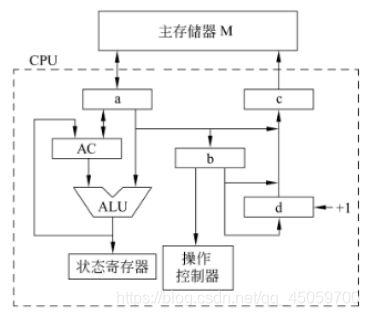

13.CPU结构如左图所示,其中有一个累加寄存器AC、一个状态条件寄存器和其他4个寄存器,各部件之间的连线表示数据通路,箭头表示信息传送方向。

寄存器的名称如下:

a是( 27 )

b是( 28 )

c是( 29 )

d是( 30 )

二、判断题:(每空1分,共10分)

1.所有逻辑电路的输出不仅与当时的输入状态有关,而且还与前一时刻的状态有关。

2.所有进位计数值,其整数部分最低位的权值都是1。

3.串行进位加法器比并行进位加法器的速度快。

4.任何的十进制小数都能用二进制精确表示。

5.不设置浮点运算指令的计算机就不能用于科学计算。

6.由于DRAM是破坏性读出,所以必须不断刷新。

7.程序只有被存入主存储器中,才可以被CPU解释、执行。

8.主存是用来存放机器指令和数据的,控存则是用来存放微程序的。

9.水平型微指令的执行速度比垂直型微指令快。

10.IR是用来存放指令和数据的寄存器。

三、选择题:(每题 2 分,共 24分)

1.一个16位无符号二进制数的表示范围是 ( )

(A)0~65536 (B)0~65535 (C)-32768~32767 (D)-32768~32768

2.设[X]补= 1.x1x2x3,仅当( ) 时,X>-1/2成立。

(A)x1必须为1,x2x3至少有一个为1

(B)x1必须为1,x2x3任意

(C)x1必须为0,x2x3至少有一个为1

(D)x1必须为0,x2x3任意

3.设浮点数的阶码和尾数均采用补码表示,且位数分别为5位和7位(均含2位符号位)。若有两个数X=27×29/32,Y=25×5/8,则用浮点数计算X+Y的最终结果是( )。

(A)00111 1100010 (B)01000 0010001

(C)00111 010010 (D)发生溢出

4. 若RAM每个存储单元为16位,则下面所述正确的是( )。

(A)地址线也是16位 (B)地址线与16无关

(C)地址线与16有关 (D) 地址线不得少于16位

得分

阅卷人

5. 存储器容量为32K×16,则( )。

(A)地址线为16根,数据线为32根 (B)地址线为32根,数据线为16根

(C)地址线为15根,数据线为16根 (D)地址线为16根,数据线为15根

6. 某计算机字长32位,存储容量是8MB,若按双字编址,它的寻址范围是( )。

(A)0~256K-1 (B)0~512K-1 (C)0~1M-1 (D)0~2M-1

7. 4个16K8位的存储芯片,可以设计为 ( )的存储器。

(A)32K16位 (B)16K16位 (C)32K8位 (D)8K*16位

8. 某指令系统有200条指令,若采用定长操作码,最少需要用( )位操作码。

(A)4 (B)8 (C)16 (D) 32

9. 2164RAM芯片(芯片内是4个128×128结构)采用分散刷新方式,如果刷新间隔不超过2ms,则刷新信号的周期是( )

(A)15.6us (B)12.8us (C)62.4us (D)51.2us

10. 某计算机的控制器采用微程序控制方式,微指令中的操作控制字段采用字段直接编码法,共有33个微命令,构成5个互斥类,分别包含7、3、12、5和6个微命令,则操作控制字段至少有( )

(A)5位 (B)6位 (C)15位 (D)33位

11.下列校验码中,奇校验正确的是( )

(A)110100111 (B)001000111 (C)010110011 (D)110100111

12. 待校验的数据为D8~D1=10101011,若采用海明校验,则校验码是( )

(A)0 1010 0 101 1 1 11 (B)0 1000 0 111 1 1 11

(C)0 1010 1 101 1 1 00 (D)0 1000 0 111 0 0 11

四、分析题(共 6 小题,共 36 分)

1、(本题 6 分)设十进制数X=(+128.75)×2-10。

(1) (2分)若(Y)2 = (X)10,用定点数表示Y的值。

(2) (2分)设用21个二进制位表示浮点数,阶码用5位,其中阶符1位;尾数用16位,其中符号用1位,阶码的基数为2,写出阶码和尾数均用原码表示的Y的机器数。

(3) (2分)写出阶码和尾数均用补码表示Y的机器数。

2、(本题 6 分)某8位微型机地址码为18位,若存储器使用4K×4位的RAM芯片扩展而成,试问:

(1)(2分)该机所允许的最大主存空间是多少?

(2)(2分)存储器中共有多少片RAM?

(3)(2分)说明地址线是如何译码的。

3、(本题 6 分)用原码一位乘计算X=0.1101,Y= - 0.1011的积 X•Y

4、(本题 6 分)某机器采用16位字长指令,

(1)(3分)若采用定长操作码,地址码5位,现已定义60条二地址指令,那么一地址指令最多多少条?

(2)(3分)修改(1)条件为不定长操作码,其余不变,答案如何?

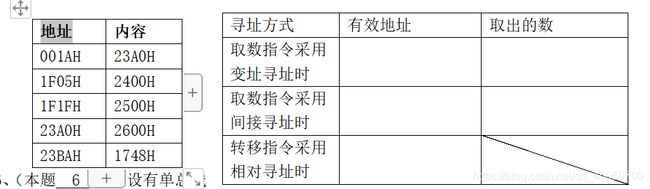

5、(本题 6 分)某计算机有变址寻址、间接寻址和相对寻址等寻址方式,设当前指令的地址码部分为001AH,正在执行的指令所在地址为1F05H,变址寄存器的内容为23A0H,请根据各种寻址方式,完成右表:

寻址方式 有效地址 取出的数

取数指令采用

变址寻址时

取数指令采用

间接寻址时

转移指令采用

相对寻址时

地址 内容

001AH 23A0H

1F05H 2400H

1F1FH 2500H

23A0H 2600H

23BAH 1748H

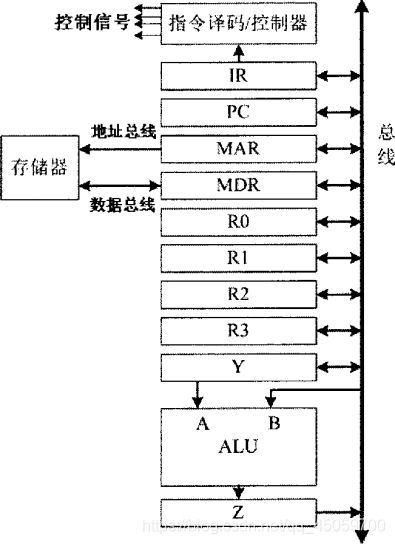

6、(本题 6 分)设有单总线结构计算机的CPU数据通路及其与存储器的连接结构如下图所示,其中,R0~R3为通用寄存器,Y和Z为临时寄存器。

试写出指令ADD R1,[(R2)+0100H]具体的执行过程。(分为多少步,每一步产生哪些微命令)(6分)。

2285

2285

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?