并行除法器 ,并行除法器结构原理是什么?

1.可控加法/减法(CAS)单元

和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成电路制造。与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。

阵列除法器有多种多样形式,如不恢复余数阵列除法器,补码阵列除法器等等。

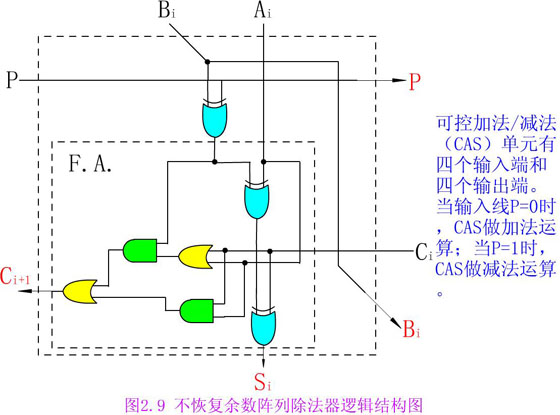

首先介绍可控加法/减法(CAS)单元,它将用于并行除法流水逻辑阵列中,它有四个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。逻辑结构图:

CAS单元的输入与输出的关系可用如下一组逻辑方程来表示:

Si=Ai⊕(Bi⊕P)⊕Ci

Ci+1=(Ai+Ci)·(Bi⊕P)+AiCi (2.32)

当P=0时,方程式(2.32)就等于式(2.23),即得我们熟悉的一位全加器(FA)的公式:

Si=Ai⊕Bi⊕Ci

Ci+1=AiBi+BiCi+AiCi

当P=1时,则得求差公式:

Si=Ai⊕Bi⊕Ci

Ci+1=AiBi

本文介绍了计算机阵列除法器的基本原理,特别是不恢复余数的阵列除法器的工作机制。阵列除法器利用可控加法/减法(CAS)单元进行并行运算,提高运算速度。不恢复余数除法器通过加减交替实现除法,当部分余数符号改变时产生商位“0”,不变时产生商位“1”。阵列由CAS单元组成,延迟时间为3T单元,对于2n位除以n位的除法,执行时间为3(n+1)²T。

本文介绍了计算机阵列除法器的基本原理,特别是不恢复余数的阵列除法器的工作机制。阵列除法器利用可控加法/减法(CAS)单元进行并行运算,提高运算速度。不恢复余数除法器通过加减交替实现除法,当部分余数符号改变时产生商位“0”,不变时产生商位“1”。阵列由CAS单元组成,延迟时间为3T单元,对于2n位除以n位的除法,执行时间为3(n+1)²T。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2081

2081

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?