作者:虞己某

链接:https://www.zhihu.com/question/29685396/answer/145507426

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

当然,实际上的设计一般clk还会AND 一个叫enable的输入,那么当enable是0的时候,clk那边就一直是0,你要写进去这个flipflop,就需要enable=1,clk=1,这时候D就被存进去了。

为什么需要clk呢,因为你的设计里面,这个寄存器在等上一个寄存器的数据,你不知道上一个寄存器的数据存好了没,是新的还是旧的,你要写进去的数据写好了没。如果每个寄存器都用不同的clk,这样设计很容易不同步async,就是我想同时写几个register,但是这个register已经写完了,那个我不知道他存好了没,全局的clk能帮助解决很多这类问题。这个clk很大程度上左右了设计里面很多东西的读写速度。这么说,clk越快就越好?也不对的,因为理论上虽然是这样,真实世界里面,这些电子元件全部都有反应速度的,clk变化比他们的setup time快的话,数据有可能还没来得及写进去,clk就变0了,写不进了。真实世界clk也不是方波,因为即使电压变得再快,从0到1v的变化也是需要时间的,不会是无时间从0突然变成1v。

链接:https://www.zhihu.com/question/29685396/answer/145507426

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

这大概要从,为什么有时钟(Clock)这个概念开始说。

这又要从flop和register开始说。

电子设备中,你要怎么去“保存”一个数据,读取和写入它呢?方法很多,现在只说教科书中最常见的。

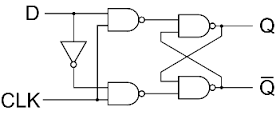

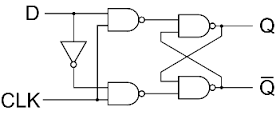

这种,三角形带个泡泡的叫非门,像个横着的门带个泡泡的叫nand gate(与非门?) 非门是这样的,输入是0输出就是1,输入是1输出就是0。与非门,只当输入都是1时,输出是0,其他时侯输出是1。上面这个设计叫d flipflop,当clk是1的时候,D的值就会被写进去,然后clk=0的时候,Q就会一直是之前那个D,clk是0的时候,D的值再变,Q也不会变。

当然,实际上的设计一般clk还会AND 一个叫enable的输入,那么当enable是0的时候,clk那边就一直是0,你要写进去这个flipflop,就需要enable=1,clk=1,这时候D就被存进去了。

为什么需要clk呢,因为你的设计里面,这个寄存器在等上一个寄存器的数据,你不知道上一个寄存器的数据存好了没,是新的还是旧的,你要写进去的数据写好了没。如果每个寄存器都用不同的clk,这样设计很容易不同步async,就是我想同时写几个register,但是这个register已经写完了,那个我不知道他存好了没,全局的clk能帮助解决很多这类问题。这个clk很大程度上左右了设计里面很多东西的读写速度。这么说,clk越快就越好?也不对的,因为理论上虽然是这样,真实世界里面,这些电子元件全部都有反应速度的,clk变化比他们的setup time快的话,数据有可能还没来得及写进去,clk就变0了,写不进了。真实世界clk也不是方波,因为即使电压变得再快,从0到1v的变化也是需要时间的,不会是无时间从0突然变成1v。

1001

1001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?