一、指令格式

指令:操作码字段 地址码字段

指令字(简称指令):表示一条指令的机器字。

指令格式:是指令自用二进制代码表示的结构形式,由操作码字段和地址码字段组成。

操作码字段:表征指令的操作特性与功能 (指令的唯一标识) 不同的指令操作码不能相同

地址码字段:指定参与操作的操作数的地址码

二、操作码分类

操作码可以分为固定长度的代码和可变长度的代码

1、固定长度的代码

多有指令操作码的长度相等

例如:某计算机共有64条指令,采用固定长度操作码,需要6位编码,从000000~111111 2的6次方为64

优点:编码方法简单,便于指令的译码

确定:不方便指令系统中增加新的指令(扩展不方便)

2、可变长度的代码

不等长的指令操作码可以减小操作码的平均长度,提高指令编码的效率,从指令的扩展性来看,也希望操作码长度可变。

例如:设某台计算机有100条指令,要求:

1)采用固定长度操作码编码,请设计其操作码编码

2)假设这100条指令中有10条指令的使用改了达到90%。其余90条指令的使用概率达到10%,请采用不定长编码设计一种操作码编码的方案,并求出操作码的平均长度(常用指令用短编码 不常用指令用长编码)

答、1)采用固定长度操作码编码,需要7位操作码,取其中100个代码作为操作码 0000000~1100011之间的代码代表100条指令(长度为7)

其余的1100100~1111111共28个代码可用于增加新的操作码

2)采用不固定长度的操作码编码,可以用4位代码对10条指令进行编码,用8位代码对90条指令进行编码

0000~1001对应10条常用的指令,从未使用的1010~1111的代码后面扩展4位

10100000~10101111 16个

10110000~10111111 16个

11000000~11001111 16个

11010000~11011111 16个

11100000~11101111 16个

11110000~11111001 10个

已上的1010 ,0000~1111,1001之间的90个代码表示其余90条指令

指令操作码的平均长度为:

4*90%+8*10%=4.4 小于等长编码的7位

剩余的编码11111010~1111111(6个)可用于操作码长度的进一步的扩展

例:设有一台简单计算机的指令系统共有10条指令,各指令的使用频率如下:

11 20% 12 12% 13 11% 14 15% 15 8% 16 3% 17 2% 18 18% 19 10% 110 1%

1)用霍夫曼编码设计这10条指令的操作码,并计算操作码的平均长度

2)设计只有2中长度,且平均长度不大于3.20位的等长扩展操作码,并计算操作码的平均长度

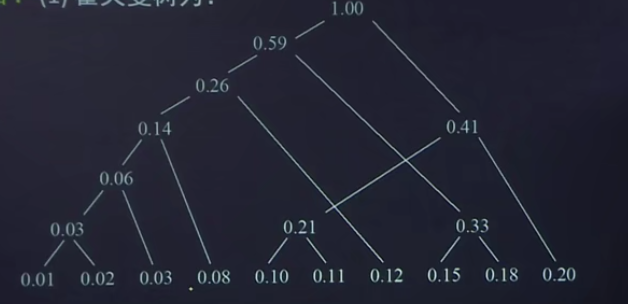

答:1)霍夫曼树为

霍夫曼编码结果如:(左支代表0 右支代表1 从最后边0.20开始霍夫曼编码如下)

11 011 010 001 101 100 0001 00001 000001 000000

平均长度:3.03 =2*0.2+3*-.18+3*0.15+....

2)一种设计方案是取3位和4位两种长度,如000 001 010 011 100 101 1100 1101 1110 1111

平均长度为3.14

3位可以表示8种编码,我们选取7个来表示三位编码,还剩4个需要扩展 也就是需要2位

另一种设计方案是选择3和5两种长度,如:000 001 010 011 100 101 110 11100 11101 11110

平均长度为3.12

选取3位表示7个 然后固定前3位为111 扩展2位 2的2次方就是4>3 也满足

三、地址码

指令中指定操作数存储位置的字段称为地址码,地址码中可以包含存储器地址。也可包含寄存器编号。

指令中可以有一个、两个或者三个操作数,也可没有操作数,根据一条指令有几个操作数地址,可将指令分为零地址指令。一地址指令、二地址指令、三地址指令。4个地址码的指令很少被使用。

操作码字段

地址码

操作码

A1

A2

A3

三指令地址

操作码

A1

A2

二指令地址

操作码

A1

一指令地址

操作码

零指令地址

零地址指令:只有操作码,没有地址码(空操作 停止等)

一地址指令:指令编码中只有一个地址码,指出了参加操作的一个操作数的存储位置,如果还有另一个操作数则隐含在累加器中

eg: INC AL

INC [S1]

二地址指令:指令编码中有两个地址,分别指出了参加操作的两个操作数的存储位置,结果存储在其中一个地址中

(op a1,a2:a1 op a2 a1)

eg: MOV AL ,BL

ADD AL,30

三地址指令:指令编码中有3个地址码,指出了参加操作的两个操作数的存储位置和一个结果的地址

(op a1,a2,a3: a1 op a2 a3)

二地址指令格式中,从操作数的物理位置来说有可归为三种类型

寄存器-寄存器(RR)型指令:需要多个通用寄存器或个别专用寄存器,从寄存器中取操作数,把操作结果放入另一个寄存器,机器执行寄存器-寄存器型的指令非常快,不需要访存。

寄存器-存储器(RS)型指令:执行此类指令时,既要访问内存单元,又要访问寄存器。

标签:编码,指令系统,计算机,地址,地址码,操作码,指令,长度,原理

来源: https://www.cnblogs.com/dream-to-pku/p/11597028.html

4015

4015

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?