在前两期的论文研读中,笔者和大家一起学习了 LeNet-5 和 AlexNet 这两个经典的卷积神经网络结构和基本实现方式。今天我们继续 CNN 经典论文研读之路——VGGNet。VGGNet 是牛津大学计算机视觉组(Visual Geometry Group)和谷歌 DeepMind 一起研究出来的深度卷积神经网络,因而冠名为 VGG。在2014年的 ILSVRC 中取得了第二名的成绩,可能你会问这么厉害的网络为什么不是第一名,因为当年实际提交 VGG 版本时作者并未作进一步的优化,而当年的第一名则是我们后面要继续研读的 Google Inception Net。

相较于之前的 LeNet-5 和 AlexNet,VGGNet 结构中大量使用 3x3 的卷积核和 2x2 的池化核,首次将卷积神经网络的卷积深度推向更深,最为典型的 VGGNet 是 VGG16 和 VGG19,其中的 16 的含义即网络中包含16个卷积层和全连接层, 19即即网络中包含19个卷积层和全连接层。VGGNet 的网络虽然开始加深但其结构并不复杂,但作者的实践却证明了卷积网络深度的重要性。深度卷积网络能够提取图像低层次、中层次和高层次的特征,因而网络结构需要的一定的深度来提取图像不同层次的特征。

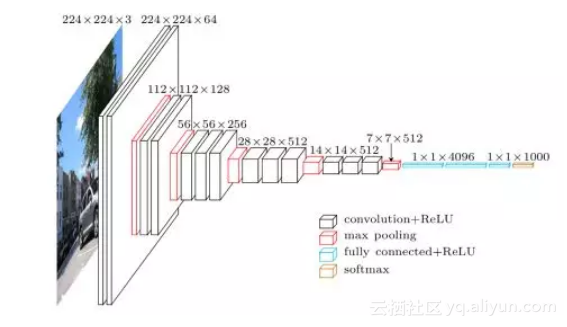

VGG的网络结构

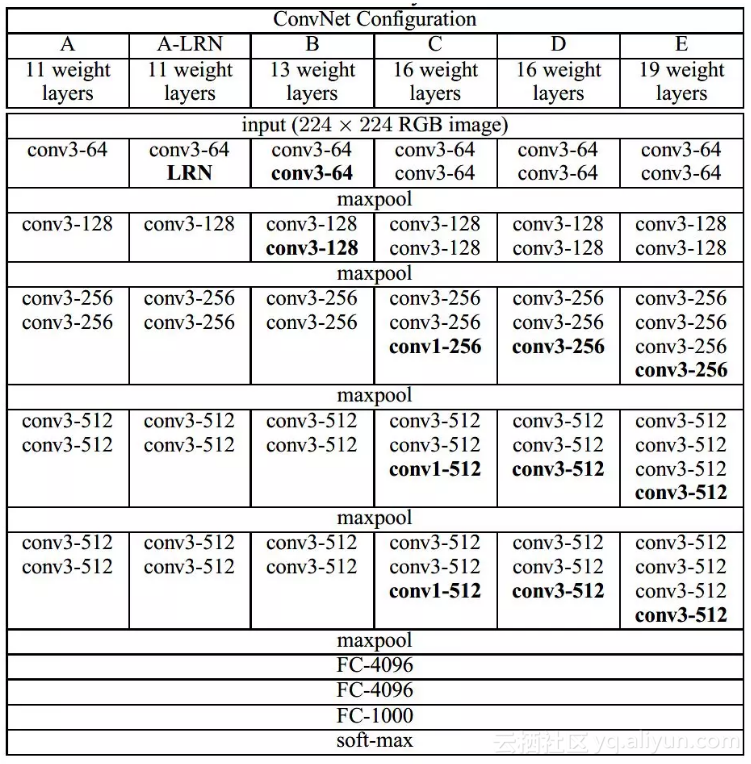

在论文中,作者使用了 A-E 五个不同深度水平的卷积网络进行试验,从A到E网络深度不断加深:

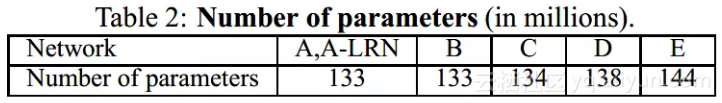

各结构网络所含训练参数:

其中 D 和 E 即我们常说的 VGG16 和 VGG19。可以看到 VGG16 网络需要训练的参数数量达到了 1.38 亿个,这个数量是巨大的。我们以 VGG16 为例简单探究一下它的网络结构。

VGG16 各层的结构和参数如下:

C1-1层是个卷积层,其输入输出结构如下:

输入: 224 x 224 x 3 滤波器大小: 3 x 3 x 3 滤波器个数:64

输出: 224 x 224 x 64

C1-2层是个卷积层,其输入输出结构如下:

输入: 224 x 224 x 3 滤波器大小: 3 x 3 x 3 滤波器个数:64

输出: 224 x 224 x 64

P1层是C1-2后面的池化层,其输入输出结构如下:

输入: 224 x 224 x 64 滤波器大小: 2 x 2 滤波器个数:64

输出: 112 x 112 x 64

C2-1层是个卷积层,其输入输出结构如下:

输入: 112 x 112 x 64 滤波器大小: 3 x 3 x 64 滤波器个数:128

输出: 112 x 112 x 128

C2-2层是个卷积层,其输入输出结构如下:

输入: 112 x 112 x 64 滤波器大小: 3 x 3 x 64 滤波器个数:128

输出: 112 x 112 x 128

P2层是C2-2后面的池化层,其输入输出结构如下:

输入: 112 x 112 x 128 滤波器大小: 2 x 2 滤波器个数:128

输出: 56 x 56 x 128

C3-1层是个卷积层,其输入输出结构如下:

输入: 56 x 56 x 128 滤波器大小: 3 x 3 x 128 滤波器个数:256

输出: 56 x 56 x 256

C3-2层是个卷积层,其输入输出结构如下:

输入: 56 x 56 x 256 滤波器大小: 3 x 3 x 256 滤波器个数:256

输出: 56 x 56 x 256

C3-3层是个卷积层,其输入输出结构如下:

输入: 56 x 56 x 256 滤波器大小: 3 x 3 x 256 滤波器个数:256

输出: 56 x 56 x 256

P3层是C3-3后面的池化层,其输入输出结构如下:

输入: 56 x 56 x 256 滤波器大小: 2 x 2 滤波器个数:256

输出: 28 x 28 x 256

C4-1层是个卷积层,其输入输出结构如下:

输入: 28 x 28 x 256 滤波器大小: 3 x 3 x 256 滤波器个数:512

输出: 28 x 28 x 512

C4-2层是个卷积层,其输入输出结构如下:

输入: 28 x 28 x 512 滤波器大小: 3 x 3 x 256 滤波器个数:512

输出: 28 x 28 x 512

C4-3层是个卷积层,其输入输出结构如下:

输入: 28 x 28 x 512 滤波器大小: 3 x 3 x 256 滤波器个数:512

输出: 28 x 28 x 512

P4层是C4-3后面的池化层,其输入输出结构如下:

输入: 28 x 28 x 512 滤波器大小: 2 x 2 滤波器个数:512

输出: 14 x 14 x 512

C5-1层是个卷积层,其输入输出结构如下:

输入: 14 x 14 x 512 滤波器大小: 3 x 3 x 512 滤波器个数:512

输出: 14 x 14 x 512

C5-2层是个卷积层,其输入输出结构如下:

输入: 14 x 14 x 512 滤波器大小: 3 x 3 x 512 滤波器个数:512

输出: 14 x 14 x 512

C5-3层是个卷积层,其输入输出结构如下:

输入: 14 x 14 x 512 滤波器大小: 3 x 3 x 512 滤波器个数:512

输出: 14 x 14 x 512

P5层是C5-3后面的池化层,其输入输出结构如下:

输入: 14 x 14 x 512 滤波器大小: 2 x 2 滤波器个数:512

输出: 7 x 7 x 512

F6层是个全连接层,其输入输出结构如下:

输入:4096

输出:4096

F7层是个全连接层,其输入输出结构如下:

输入:4096

输出:4096

F8层也是个全连接层,即输出层,其输入输出结构如下:

输入:4096

输出:1000

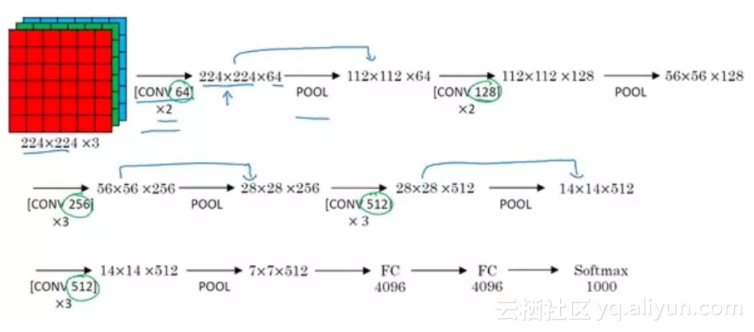

大致过程如 NG 老师的演示图:

从上述的 VGG 结构分析中,我们可以看到这种网络结构非常规整,2-2-3-3-3的卷积结构也非常利于编程实现。卷积层的滤波器数量的变化也存在明显的规律,由64到128再到256和512,每一次卷积都是像素成规律的减少和通道数成规律的增加。

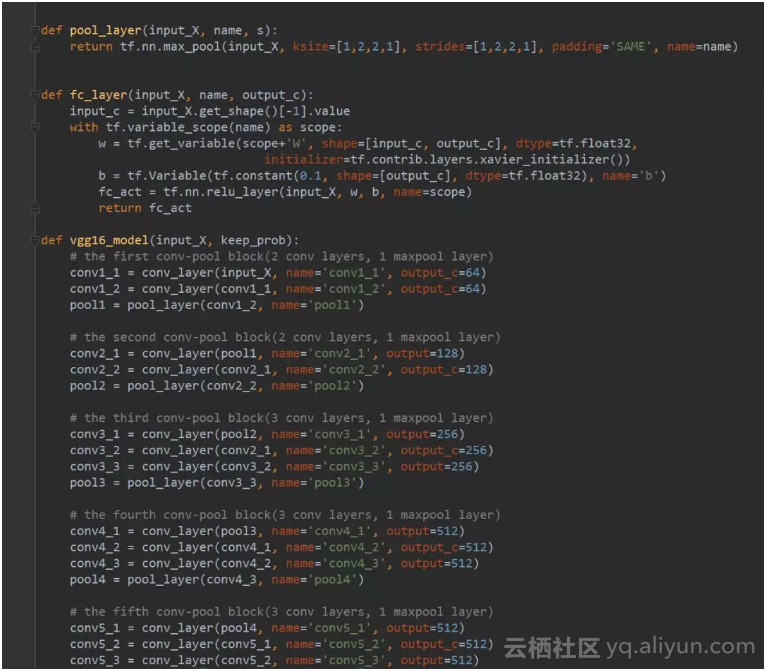

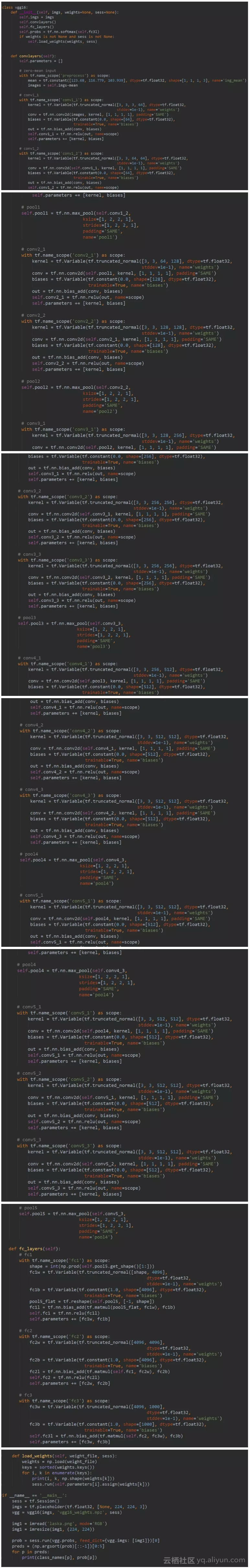

VGG16 的简单实现

原本自己利用 Tensoflow 简单写了个 VGG16 的网络结构,但去谷歌一搜发现别人的代码写的实在太好了,以至于这里就不用自己代码展示 VGG16 了。编写的思路无非就是定义卷积过程、池化过程和全连接过程,然后将其封装到 VGG16 的模型函数中去,其中注意一些编写细节即可。

笔者自己写的部分代码截图:

GitHub 上大佬的开源实现:

https://gist.github.com/ksimonyan/211839e770f7b538e2d8#file-readme-md

原文发布时间为:2018-10-10本文作者:louwill本文来自云栖社区合作伙伴“ Python爱好者社区”,了解相关信息可以关注“ Python爱好者社区”。

2613

2613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?