本节书摘来自华章出版社《计算机存储与外设》一书中的第1章,第2节,作者Computer Organization and Architecture: Themes and Variations[英]艾伦·克莱门茨(Alan Clements) 著,沈 立 肖晓强 王苏峰 译,更多章节内容可以访问云栖社区“华章计算机”公众号查看。

1.2 Cache存储器的性能

在判断加入Cache是否划算之前,需要知道增加Cache对计算机性能会产生多大的影响。这里首先介绍一个简单的模型,忽略实际Cache系统的细节:每个系统的Cache都不完全一样。特别是,该模型假定每个Cache项都为一个字宽,而实际Cache存放的是一个块(包含若干个字)。

Cache系统的主要参数就是命中率(hit ratio)h,它定义为所有访问操作在Cache中命中的概率,由系统操作统计结果决定。访问局部性的作用使得命中率通常较高,基本保持在98%左右。本章的后续部分将讨论影响命中率的因素以及使h保持较高值的方法。

在计算Cache对处理器性能的影响之前,需要引入一些术语:

主存储器访问时间 tm

Cache访问时间 tc

命中率 h

失效率 m

加速比 S

加速比(speedup ratio)是没有Cache时存储系统的访问时间与具有Cache时系统访问时间的比值。对于N次访存,如果没有Cache,则总的访问时间为Ntm。

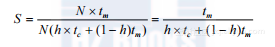

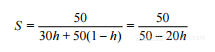

对于N次访存,如果有Cache,总访问时间是N(htc+mtm)。失效率m,定义为m=1-h,因为访问要么命中要么不命中。因此,具有Cache的系统的加速比为:

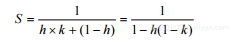

该表达式假定所有操作均为访存操作,这是不正确的,因为处理器也要完成内部操作。后面还会谈到这一点。如果不关心主存储器和Cache的绝对速度的话,可以引入一个参数,k=tc/tm,它定义了Cache相对主存储器的速度比例。由h和k定义的加速比为:

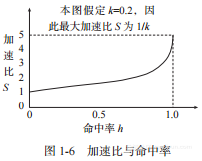

图1-6显示了当k=0.2时加速比S与命中率h的关系曲线。正如大家理解的那样,当h=0时的加速比为1,因为所有访存操作都访问了主存储器。当h=1时,所有访存操作都在Cache中进行,因此加速比为1/k。

从图1-6中得出的一个最重要的结论是,加速比对命中率敏感。只有当h接近90%,Cache的性能影响才十分显著。该结论与常识是一致的。如果h低于90%,访问主存储器的时间占较大比例,快速访问Cache带来的效果对系统性能的影响不大。

上述加速比S的公式适用于存储器和Cache可并行工作的系统,因为它假定每个存储周期开始时,同时(并行)访问主存储器和Cache;也就是,访存地址同时交给Cache和主存储器。如果命中,终止对主存储器的访问。如果Cache不响应,数据将从主存储器中返回。

实际微处理器能够获得的加速比并不如上述公式得到的那样乐观。真实微处理器的操作速度由其时钟周期、每个存储器访问所需时钟周期数以及由于访问存储器而处于等待状态的时间确定。加快Cache的速度并不如减少等待时间重要。即使使用十分快速的Cache,也不可能将访存时间减少到比不包含等待状态的一个总线周期还要短。

看看下面这个例子。

微处理器的时钟周期时间 10ns

每个总线周期所需最小时钟周期数 3

存储器访问时间 40ns

由于访存带来的等待时间 2个时钟周期

Cache访问时间 10ns

由于访问Cache带来的等待状态 0

这些数据表明,存储器访问需要(3个时钟周期+ 2个等待状态)×10ns=50ns,访问Cache需要3×10ns=30ns。该计算过程并不包含主存储器和Cache的实际访问时间。加速比为:

假设平均命中率为95%,根据上式计算的加速比是1.61(即161%)。该结果比直接拿Cache和主存储器的访存时间来计算得到的结果(即2.46)要小。

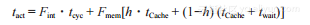

以上公式省略了不需访问存储器的内部操作的影响。下面看看德克萨斯仪器公司操作说明书中给出的既考虑非存储器访问操作又考虑访问Cache和主存储器中的数据时,微处理器的平均周期时间tact。

式中:

Fint为处理内部操作指令所占比例(以70%为例);

Fmem为访存操作指令所占比例(以30%为例);

tcyc为处理器的时钟周期时间(以10ns为例);

twait为由于Cache失效导致的等待时间(以50ns为例);

tCache为Cache访问时间(以5ns为例);

h为命中率(以0.9为例)。

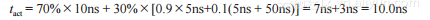

把给出的实际参数的例子代入公式计算,可得:

即使是这个结果也没有给出全部事实,因为实际系统不会一次仅在Cache和主存储器间移动一个字的数据。Cache基本存储单元的容量不只是一个字,而是一块(line),它通常包括4~64个字节。当发生失效时,从存储器中会传输一块数据到Cache。因此,失效开销不仅仅是调入一个数据,而是包括一块数据。

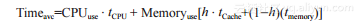

此时,也许可以对前面提到的存储墙进行讨论。假设某系统以周期为单位的指令平均执行时间Timeavc为:

式中,CPUuse表示非访存指令所占比例(以80%为例);tCPU表示这类指令执行需要的时钟周期数(假定为1);Memoryuse表示访存指令所占比例;tmemory表示这类指令执行需要的时钟周期数(假定为10)。如果命中率h为0.95,则:

Timeave = 0.80·1 + 0.20·0.95·1 + 0.20·(1-0.95)·10 = 0.80 + 0.19 + 0.10 = 1.09个周期

经过一段时间,处理器的速度提高10倍,Cache的速度提高5倍,DRAM的速度提高2倍。CPU、Cache与DRAM的访问时间之比不再是1∶1:10,而是1∶2∶50。此时,

Timeave = 0.80·1 + 0.20·0.95·2 + 0.20·(1-0.95)·50 = 0.80 + 0.38 + 0.50 = 1.68个周期

假设第二种情况下,时钟周期时间是第一种情况的1/10,加速比为10.9/1.68=6.488。这表明时钟和CPU的速度快了10倍,而吞吐量只增加了6倍。

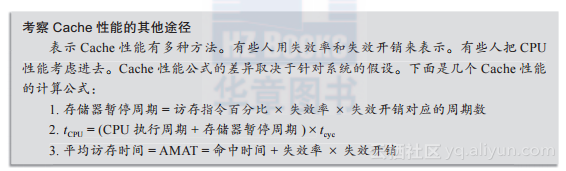

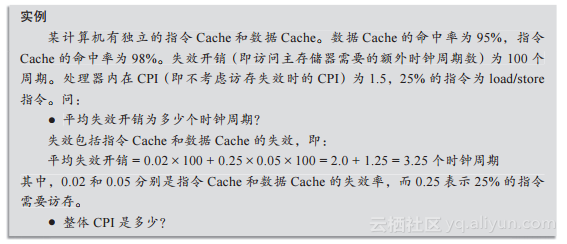

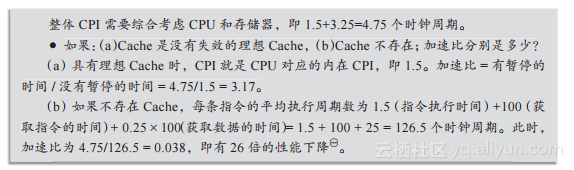

如果考虑Cache的写失效,可以重新审视Cache的性能。

999

999

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?