计算机组成原理-第四章-存储器思维导图

思维导图在文末

目录

计算机组成原理-第四章-存储器思维导图

存储器

4.1概述

4.1.1存储器分类

1 按存储介质分类

2. 按存取方式分类

3.按在计算机的作用分类

4.1.2 存储器的层次结构

缓存——主存层次

主存——辅存层次

4.2主存储器

4.2.1概述

4.2.2半导体存储芯片简介

1.基本结构

2.半导体存储芯片的译码驱动方式

4.2.3随机存取存储器

3.1.静态RAM

3.2.动态RAM

3.3动态RAM与静态RAM比较

3.5动态RAM缺点

4.2.5存储器与CPU的连接

5.1存储器容量拓展

5.2存储器与CPU连接

4.2.6存储器的校验

4.2.7提高访存速度的措施

4.3高速缓冲存储器

4.3.1概述

4.3.2Cache——主存地址映射

4.3.3替换策略

4.4辅助存储器

4.4.1概述

4.4.2磁记录原理和记录方式

4.4.3硬磁盘存储器 4.4.3软磁盘存储器 4.4.5磁带存储器 4.4.6循环冗余检验码

4.4.7光盘存储器

存储器

4.1概述

4.1.1存储器分类

1 按存储介质分类

半导体存储器

磁表面存储器

磁芯存储器

光盘存储器

2. 按存取方式分类

随机存取器

只读存储器

串行访问存储器

3.按在计算机的作用分类

主存储器、

辅助存储器

缓冲存储器。

4.1.2 存储器的层次结构

缓存——主存层次

解决CPU和主存速度不匹配的问题

主存——辅存层次

主要解决存储系统容量问题

4.2主存储器

4.2.1概述

主存储存单元地址的分配:常用8位为进制数表示一个字节

主存的技术指标是:存储容量和速度

1.存储容量:存储容量=存储单元个数*存储字长 字节表示除8即可

2.存储速度:由存取时间和存取周期来表示

3.存储器带宽:表示单位时间内存储器存取信息量,单位:字/秒或字节/秒或位/秒

4.2.2半导体存储芯片简介

1.基本结构

地址线:单向输入的,其位数与芯片容量有关

数据线:双向的其位数与芯片可读出或写入的数据有关。数据线的位数与芯片容量有关

控制线:主要有读写控制线与片选线两种。

地址线和数据线的位数共同反映存储芯片的容量

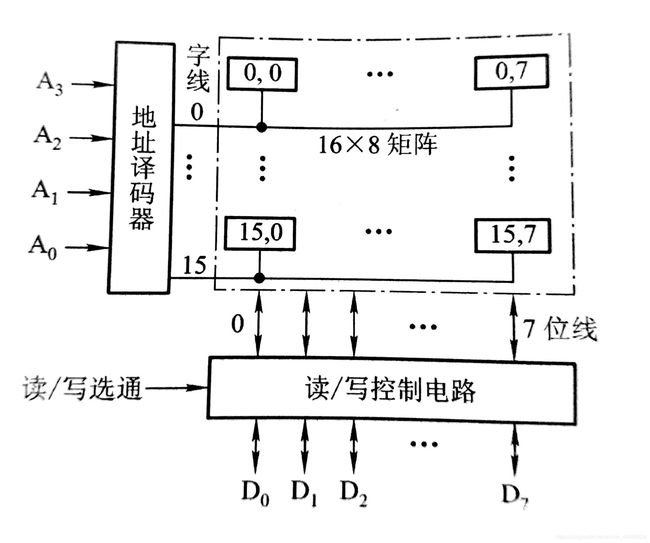

2.半导体存储芯片的译码驱动方式

1.线选法

线选法

线选法

适用容量不大的存储芯片

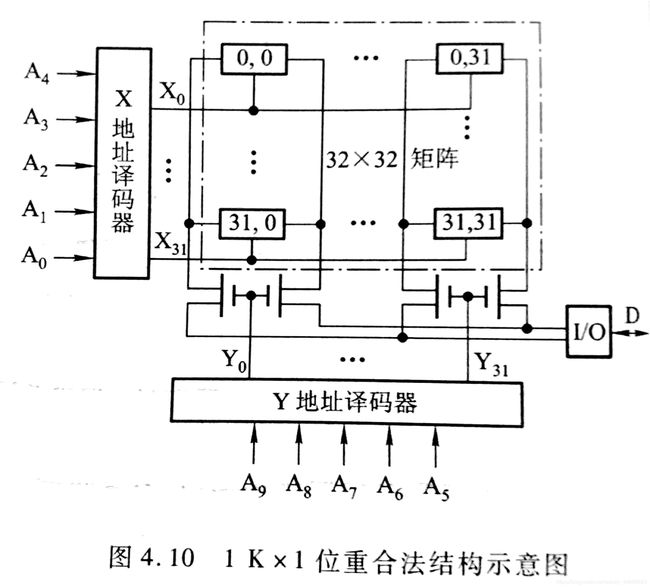

2.重合法

重合法

重合法

4.2.3随机存取存储器

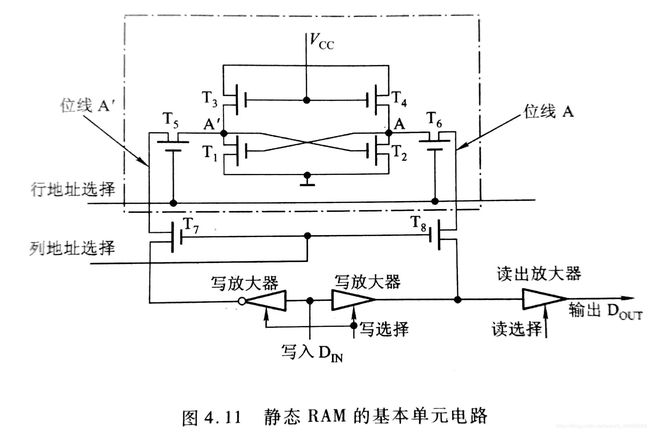

3.1.静态RAM

1.基本单元电路

电路图

电路图

3.2.动态RAM

动态RAM的刷新(原因)

刷新:实质上就是将原信息读出,再由刷新放大器形成原信息并重写入的再生过程。

原因:由于存储单元是被随机访问的,有可能某些存储单元长期得不到访问,不进行存储器的读/写操作,其存储单元内的原信息将会慢慢消失。

刷新周期:一般取2ms

1.集中刷新

在规定刷新周期对全部存储单元集中一段时间逐行进行刷新,此时必须停止读/写操作。缺点:会出现“死时间”"死区"。

2.分散刷新

分散到每个存取周期内完成 优缺点:不存在读取死时间,但存取周期长了,降低系统速度

3.异步刷新

钱两种方式结合,既可以缩短“死时间”,又充分利用最大刷新时间间隔为2ms的特点。

3.3动态RAM与静态RAM比较

1.在同样大小芯片中,动态RAM的集成度远高于静态RAM。

2.动态RAM行,列地址按先后顺序输送,减少芯片引脚,封装尺寸也减少了。

3.动态RAM功耗比静态RAM小

4.动态RAM的价格比静态RAM便宜。广泛应用于计算机主存。

3.5动态RAM缺点

1.由于使用动态元件,因此速度比静态RAM低。

2.动态RAM需要再生,故需要配置再生电路,需要消耗一部分功率。

4.2.5存储器与CPU的连接

5.1存储器容量拓展

1.位扩展:指增加存储字长。

2.字扩展:指增加存储字的数量。

3.字,位扩展:增加存储字长和存储字数量。

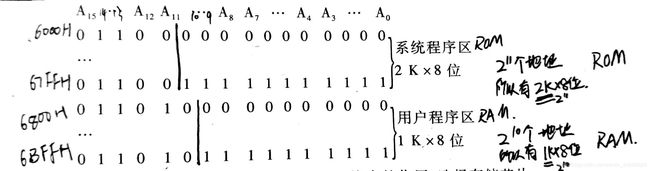

5.2存储器与CPU连接

1.地址线的连接

将CPU地址线的低位与存储芯片的地址线相连。CPU地址线的高位预留给存储芯片扩充时用或者其他用途。

2.数据线的连接

两者数据线 线数也不相等,必须对存储芯片扩位使其数据位数与CPU线数相等。

3.读/写命令线的连接

读写控制端可直接与CPU读写命令线相连,

一般高电平——>读,低电平——>写。

4.片选线的连接

5.合理选择存储芯片

6.连接五部曲

第一步:写出地址的二进制范围

@taokee

@taokee

第二步:选择芯片的种类和数量

第三步:地址线的连接

第四步:数据线的连接和 读/写控制线的连接

第五步:形成片选信号

4.2.6存储器的校验

6.1汉明码

纠错理论:L-1=D+C且D>=C

↑编码距离L越大,其检测错误的位数D越大,纠错的位数C也越大,且纠错能力恒小于或等于检错能力

满足关系:2^k>=n+k+1 n:二进制代码位数,k为检测位数

奇偶配置

6.2汉明码纠错

关于汉明码的纠错,我找到一份ppt专门讲汉明码组成和纠错的,这里不过多介绍。

汉明码pdf文件:汉明码详解

永久链接:汉明码详解pdf

4.2.7提高访存速度的措施

7.1单体多字系统

7.2多体并行系统

7.3高性能存储芯片

1.SDRAM

2.RDRAM

4.3高速缓冲存储器

4.3.1概述

I/O设备向主存请求级别高于cpu访存。为避免CPU与I/O设备争抢访存,在CPU与主存之间加一级缓存。

Cache 命中率:h=N(C)/(N(C)+N(M)) N(c)表示:总命中次数,N(m):访问主存总次数。

Cache的读写操作

1.写直达法,

2.写回发

4.3.2Cache——主存地址映射

1.直接映射

i=j mod C或i=j mod 2^c i为缓存块,j为主存块号,C为缓存块数。mod 取余。

某一个缓存块可以和若干个主存块建立对应关系 某一个主存块可以和唯一缓存块建立对应关系

优点实现简单。

2.全相联映射

允许主存中每一字块映射到Cache中的任何一块位置上

缺点:所需逻辑电路多,成本高

3.组相联映射

4.3.3替换策略

1.先进先出FIFO算法

2.近期最少使用LRU算法

3.随机法

4.4辅助存储器

4.4.1概述

辅存特点:容量大,速度慢,价格低,可以脱机保存信息。

4.4.2磁记录原理和记录方式

记录方式

1.归零制

2.不归零制

3.见1就翻的 不归零制

4.调相制

5.调频制

6.改进调频制

4.4.3硬磁盘存储器

4.4.3软磁盘存储器

4.4.5磁带存储器

4.4.6循环冗余检验码

CRC冗余检验在计算机网络学过一次,不多打字了,附上ppt资源链接,可自行查看学习。

资源链接:CRC循环冗余检验

永久链接:CRC PDF

4.4.7光盘存储器

思维导图地址:存储器思维导图

喜欢的话一键四连(点赞,收藏,转发,赞赏哦)

4624

4624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?