上一篇文章在介绍存储器时,提到了CPU高速缓存,这是计算机在硬件层面上应用缓存技术的一个典型设计,CPU的每个核心都拥有自己的L1 Cache和L2 Cache,并且共享L3 Cache。在单核情况下,这种缓存方案很好理解:CPU加载一部分内存数据放到自己的高速缓存空间中,利用高速缓存中的内容进行运算,修改了内存数据后也会暂时放在高速缓存中,必要时刻将缓存内容更新进内存中。那么,这个必要时刻是怎么定义的呢?

高速缓存的写入与写回

数据写入

高速缓存的数据都是从内存中来的,不同于我们使用redis等内存结构作为数据库数据缓存的概念,高速缓存是一个实实在在存在于CPU中的物理结构,它与内存之间存在一个映射关系 ,映射的最小单位为Cache Line(缓存块,对应内存中的内存块),这个映射关系可以准确的将内存中的数据块映射到高速缓存中。

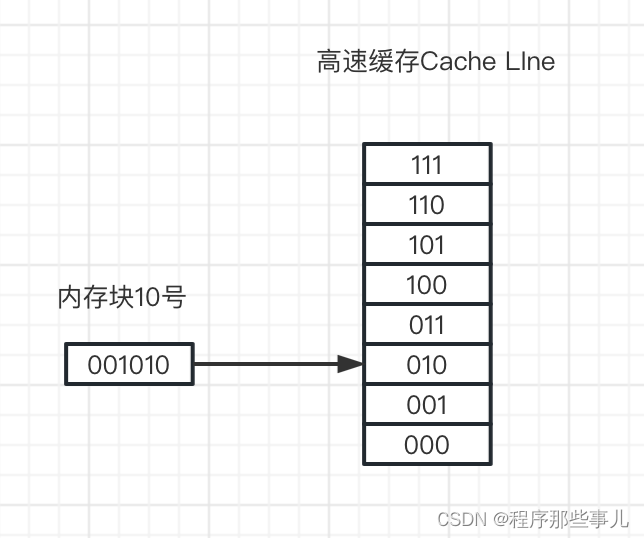

我们这里从最基本的直接映射说起,Cache Line的大小一般为64K,所以整个内存也会被切分成n多个64K大小的块,简称内存块,直接映射采用取模运算,保证每个内存块都可以被映射到高速缓存上(有点类似于HashMap的存储模式)。例如高速缓存中有8个Cache Line,内存中的内存块有32个,那么编号为10的内存块就会被映射到Cache Line 2号位上,这个Cache Line的位置记为010,也既是内存块编号的低三位。

这里自然可以想到,有可能多个内存块会被映射到同一个Cache Line上,怎么区分当前Cache Line中存放的是哪个内存块呢?Cache Line中存了一个组标记,用来记录内存块的高三位即001,这样高三位和低三位就组成了一个完整的内存块的唯一索引。

除了组标记外,Cahe Line中还存放了另外两个内容:有效位和数据。数据自然就是从内存中加载过来的数据。有效位是标识当前Cache Line的数据是否有效,如果是0的话代表无效,也就是此时这个Cache Line中没有数据,如果是1的话代表有效,也就是此Cache Line中已经有数据了。

所以高速缓存的写入过程为

除了直接映射外,缓存和内存间的映射关系还有组相连,全相连策略,理解了直接映射,其他两个映射关系也好理解,这里不在做过多介绍。

数据写回

高速缓存的数据在写入后,如果CPU拿到数据并做了修改后是直接写入内存吗?这肯定很慢;那只写入到高速缓存?这个速度快了,但仍需要在合适的时机将缓存数据写回内存。这涉及到了两种写回策略:写直达(write-throuth)与写回(write-back)。

写直达(write-through)

CPU每次修改完数据后同时更新缓存和主内存中的数据,保证了内存与缓存数据的强一致性,但是速度很慢。

写回(write-back)

CPU修改完数据后会优先更新到缓存中,在某个缓存块(Cache Line)的数据即将被淘汰时,才将缓存块的数据写入到内存中。这种策略执行速度比较快,保证了CPU不被“慢吞吞”的内存拖累执行速度。但是由于缓存与内存会存在短时间的数据不一致,如果系统突然掉电的话,会丢失一部分数据,不过内存中的数据在掉电时也会丢失(基于内存实现的中间件如redis,会有持久化机制,掉电丢数据应该是这一层应该考虑的事),所以这种情况一般不会造成什么问题。

采用写直达还是写回策略,首先要考虑的系统带宽。对于处理器芯片最外层的高速缓存,由于片外带宽有限,往往采用写回策略;而对于内层高速缓存,由于片上带宽较大,因此往往采用写直达策略。所以具体采用哪种策略是CPU内部在做的事,这里不做深究。

上面介绍的写入与写回策略在单核结构下可以正常工作,不存在线程并发时数据不一致的情况。进入多核结构后,每个核心都有自己的缓存空间,并在自己的运算单元中利用缓存数据进行运算,这种情况下会有什么问题呢?

缓存一致性

多核情况下,如果每个核心各自为政的话,缓存数据就有可能出现不一致的情况,如下图所示,两个核心分别读取了内存中的【金额】数据,黄色框代表核心修改了【金额】的值,但是每个核心之间各自为政,这就导致了在核心1修改了【金额】并且还未及时刷回缓存时,核心1与核心2的高速缓存中【金额】的值已经不一样了,如果接下来核心2又继续用【金额】值做运算的话就乱套了。

这种情况也就是多个核心中的缓存数据不一致了。

为了解决多核心之间缓存数据一致性的问题,计算机为多核心引入了一个能保证一致性的协议,即MESI协议。MESI协议的详细信息请待下回分解。

总结

本章介绍了CPU高速缓存是如何与内存进行数据交换的,交换的基本单位为 【高速缓存:缓存块(Cache Line),内存:内存块】,缓存块与内存块之间有着映射关系来保证内存块可以正常映射到缓存块。缓存写回内存的策略有两种,写直达(write-through)和写回(write-back),写直达保证了缓存和内存数据的强一致性,但是速度很慢。写回策略的速度很快,但是会有短时间的数据不一致。多核情况下,每个核心拥有自己的缓存,可能会有核心间数据不一致的问题,下一篇文章我们来看看CPU是如何保证缓存一致性的。

5021

5021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?