assign相当于一条连线,将表达式右边的电路直接通过wire(线)连接到左边,左边信号必须是wire型。当右边变化了左边立马变化,方便用来描述简单的组合逻辑。示例:

当对一组信号进行assign,就需要放到generate中,并用for语句包起来,并且注意,

在Synopsys DC中, 每个for 都要配上begin end。示例:

当对一组信号进行assign,就需要放到generate中,并用for语句包起来,并且注意,

在Synopsys DC中, 每个for 都要配上begin end。示例:

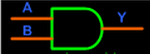

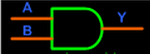

wire a, b, y;

assign y = a & b;

综合结果图:

当对一组信号进行assign,就需要放到generate中,并用for语句包起来,并且注意,

在Synopsys DC中, 每个for 都要配上begin end。示例:

当对一组信号进行assign,就需要放到generate中,并用for语句包起来,并且注意,

在Synopsys DC中, 每个for 都要配上begin end。示例:

input wire [QUANT*BITWID-1:0] predecessor_vertex_i;

wire [BITWID-1:0] predecessor[0:QUANT-1];

genvar j;

generate

for (j=0; j<QUANT; j=j+1)

begin: vector2array

assign predecessor_vertex[j][BITWID-1:0]

= predecessor_vertex_i[BITWID*(j+1)-1:BITWID*j];

end

endgenerate

你可以理解为画一条导线,将等号两边的两个信号连起来

转自:https://www.zhihu.com/question/24208772

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?