上一章我们搞懂了总线的底层逻辑,知道它是计算机各组件数据传输的“高速公路网”。而数据传输的核心目的地之一,就是CPU内部的通用寄存器——它们是CPU处理数据的“贴身操作台”,所有运算、数据暂存、地址定位都围绕它们展开。

在众多CPU架构中,x86架构的32位通用寄存器是最具代表性的——它不仅奠定了现代PC的计算基础,更是底层编程(汇编、系统内核开发)的核心认知载体。很多程序员在学习汇编时,对EAX、EBX这些寄存器的用途一知半解,本质就是没搞懂它们的底层原理和设计逻辑。

这一章我们就把x86架构32位通用寄存器彻底讲透:从它的核心原理(为什么是32位?如何实现数据存储与运算协同?),到8个核心通用寄存器的具体类型与专属用途,再到它们如何组成寄存器组、配合栈帧构建复杂电路,最后拆解它在计算机系统中的实际应用,以及对底层编程的关键影响——搞懂这8个寄存器,你才能真正打通“CPU运算→数据传输→编程实现”的底层逻辑,读懂汇编代码,理解程序的底层执行流程。

一、先搞核心:x86 32位通用寄存器的本质与设计初衷

在讲具体类型之前,我们先明确x86架构32位通用寄存器的核心定位:CPU内部集成的32位高速数据存储与运算交互单元,兼具“通用性”(可自由存储数据/地址)和“专用性”(部分寄存器有默认用途),是连接ALU运算单元、总线与内存的核心枢纽。

1. 核心原理:32位宽度的底层逻辑——适配32位计算与地址空间

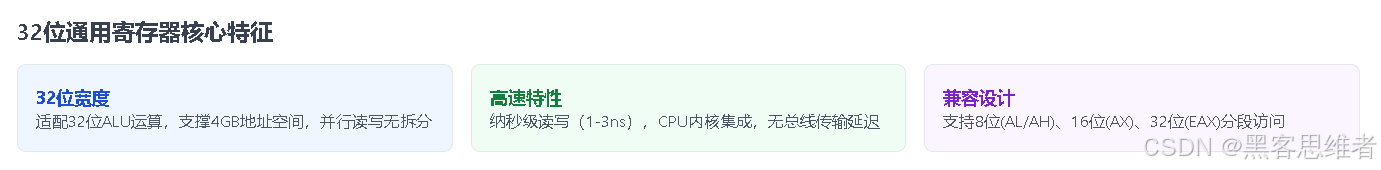

x86架构32位通用寄存器的核心特征是“32位数据宽度”,这个宽度不是随意定义的,而是与32位CPU的整体设计深度绑定:

-

适配32位运算:32位ALU(算术逻辑单元)的运算宽度为32位,通用寄存器的32位宽度可直接与ALU对接,无需数据拆分/拼接,大幅提升运算效率——比如执行32位整数加法时,EAX寄存器的32位数据可直接传入ALU,运算结果也能直接写回EAX;

-

支撑32位地址空间:32位通用寄存器可直接存储32位内存地址(对应2³²=4GB地址空间),与x86 32位架构的地址总线宽度匹配——比如EBX寄存器可存储数组的基地址,通过偏移量就能定位到数组元素的内存位置;

-

高速性根源:与所有寄存器一样,32位通用寄存器由32个D触发器并行组成,读写速度为纳秒级(1-3ns),且直接集成在CPU内核,与ALU、控制单元的传输路径极短,无总线传输延迟。

2. 设计初衷:解决“运算数据暂存”与“地址定位”的核心痛点

在32位x86架构出现之前,8位、16位寄存器存在明显局限:8位寄存器只能处理1字节数据,16位寄存器仅能支撑64KB地址空间,无法满足大型程序和多任务的需求。32位通用寄存器的设计,核心是解决两个痛点:

-

高效暂存运算数据:避免CPU每次运算都从内存读取数据(内存读写速度比寄存器慢100倍以上),将高频使用的运算数据(比如循环变量、累加结果)暂存到寄存器,提升运算效率;

-

精准定位内存地址:32位宽度可覆盖4GB内存空间,能直接存储内存地址,配合总线实现CPU与内存的高效数据交换——这是多任务操作系统(比如Windows XP、Linux 32位)能稳定运行的基础。

二、x86 32位通用寄存器的组成:从触发器到寄存器组

x86 32位通用寄存器不是单一的硬件单元,而是由“单个32位寄存器的内部组成”和“8个寄存器的集群组成”两部分构成,既保证单个寄存器的高速读写,又实现多个寄存器的协同工作。

1. 单个32位通用寄存器的内部组成:32个D触发器的并行架构

每个32位通用寄存器(如EAX)的核心组成是32个独立的D触发器,按并行方式连接,配合控制逻辑实现32位数据的同步读写:

-

核心组件:32个D触发器(每个对应1位二进制数据,0或1)、1组读写控制信号、1个时钟同步信号(CP);

-

工作逻辑:

写入时:控制单元发送“写允许”信号,时钟信号触发(上升沿),32位数据同时写入32个D触发器(并行写入,无先后顺序); -

读取时:控制单元发送“读允许”信号,32个D触发器的状态同时输出(并行读取),直接传输到ALU或总线接口;

-

稳定性保障:D触发器的“边沿触发”特性,确保只有在时钟信号触发时才会更新数据,避免数据传输过程中的干扰。

兼容设计:支持16位、8位模式:为了兼容16位、8位程序,32位通用寄存器在硬件上支持“分段访问”——比如EAX寄存器的低16位可作为独立的16位寄存器AX使用,AX的低8位可作为8位寄存器AL使用,高8位可作为8位寄存器AH使用。这种设计通过“位选择器”实现:控制单元发送不同的位选择信号,即可读取/写入不同宽度的数据。

2. 8个通用寄存器的集群组成:寄存器组与控制逻辑

x86 32位架构共有8个通用寄存器(EAX、EBX、ECX、EDX、ESI、EDI、EBP、ESP),它们共同组成“通用寄存器组”,由CPU的控制单元统一调度:

-

核心组件:8个32位通用寄存器、寄存器选择器、数据总线接口、控制信号解码器;

-

工作逻辑:

指令解码后,控制单元通过“寄存器选择器”确定要操作的寄存器(比如执行add eax, ebx时,选择EAX和EBX); -

通过数据总线接口,将选中寄存器的数据传输到ALU,或接收ALU的运算结果;

-

多个寄存器可并行工作(比如ESI负责读取数据,EDI负责写入数据),提升数据处理效率。

三、x86 32位通用寄存器的8大类型:功能细分,各司其职

虽然名为“通用寄存器”,但8个寄存器在硬件设计上存在“默认功能分工”——这种分工是x86架构的指令集约定,让指令执行更高效(比如部分指令默认使用特定寄存器存储操作数)。我们逐一拆解每个寄存器的核心用途、典型场景和硬件约定。

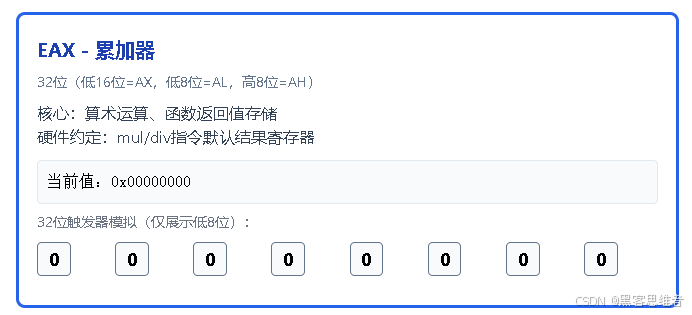

1. EAX:累加器——运算与返回值的“专用容器”

-

核心用途:算术运算(加法、乘法等)的累加器,函数返回值的默认存储位置;

-

硬件约定:很多算术运算指令(如

add、mul)默认将EAX作为运算目标或结果存储寄存器; -

典型场景:

执行int a = 10 + 20时,10和20的加法结果先存入EAX,再写入内存a的地址; -

C语言函数返回int类型值时,返回值会自动存入EAX,调用方从EAX读取结果;

-

兼容模式:低16位为AX(累加器),AX低8位为AL,高8位为AH,可用于8位/16位运算(比如

add al, 0x05)。

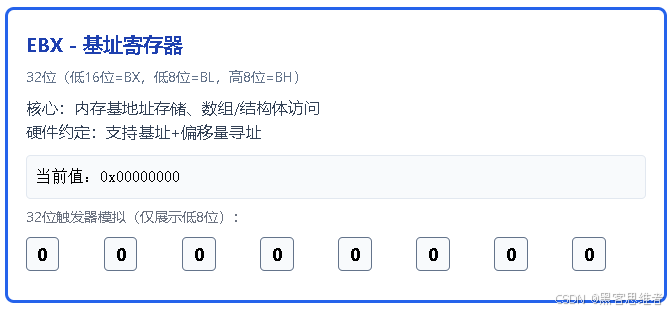

2. EBX:基址寄存器——内存访问的“基准定位器”

-

核心用途:存储内存地址的“基地址”,配合偏移量实现对连续内存区域的访问(比如数组、结构体);

-

硬件约定:支持“基址+偏移量”的寻址方式(如

mov eax, [ebx + 4]),适合访问复杂数据结构; -

典型场景:

访问数组时,EBX存储数组的起始地址,通过ebx + i*4(i为索引,4为int类型宽度)定位第i个元素; -

访问结构体时,EBX存储结构体的基地址,通过偏移量访问结构体的成员(比如

mov eax, [ebx + 8]访问结构体中偏移量为8的成员); -

兼容模式:低16位为BX,BX低8位为BL,高8位为BH。

3. ECX:计数器——循环与重复操作的“自动计时器”

-

核心用途:存储循环次数或重复操作的计数,配合循环指令(如

loop)实现自动计数; -

硬件约定:

loop指令执行时,会自动将ECX的值减1,直到ECX为0时结束循环;字符串操作指令(如rep movsb)也默认使用ECX作为重复次数计数器; -

典型场景:

实现for (int i = 0; i < 10; i++)循环时,ECX存储循环次数10,每次循环ECX自减1; -

复制字符串时,ECX存储字符串长度,

rep movsb指令自动重复复制,直到ECX为0; -

兼容模式:低16位为CX,CX低8位为CL,高8位为CH(字符串操作中,CL常存储字符长度)。

4. EDX:数据寄存器——高字节扩展与I/O操作的“辅助工具”

-

核心用途:配合EAX实现64位运算(存储高32位结果),或作为I/O操作的数据寄存器;

-

硬件约定:乘法运算(

mul)时,若结果超过32位,低32位存入EAX,高32位存入EDX;除法运算(div)时,EDX存储被除数的高32位(与EAX组成64位被除数);I/O指令(in、out)默认使用EDX存储I/O端口地址; -

典型场景:

执行32位×32位乘法(如0x12345678 × 0x87654321)时,结果可能为64位,低32位存EAX,高32位存EDX; -

从I/O端口读取数据时,EDX存储端口地址(如0x60对应键盘端口),

in al, dx指令从该端口读取数据存入AL; -

兼容模式:低16位为DX,可直接存储16位I/O端口地址。

5. ESI:源变址寄存器——数据复制的“源地址指针”

-

核心用途:存储数据复制/传输的“源地址”,配合EDI实现高效的数据块移动;

-

硬件约定:字符串操作指令(如

movsb、cmpsb)默认使用ESI指向源数据地址,且执行后ESI会自动递增/递减(根据方向标志位DF); -

典型场景:

复制数组A到数组B时,ESI存储数组A的起始地址(源地址),EDI存储数组B的起始地址(目的地址),rep movsb指令自动将ESI指向的数据复制到EDI指向的地址; -

比较两个字符串时,ESI指向第一个字符串的起始地址,EDI指向第二个字符串的起始地址,

rep cmpsb指令自动逐字节比较; -

兼容模式:低16位为SI(源变址寄存器),适配16位地址空间。

6. EDI:目的变址寄存器——数据复制的“目的地址指针”

-

核心用途:存储数据复制/传输的“目的地址”,与ESI配对使用,是数据块移动的核心寄存器;

-

硬件约定:与ESI配合,字符串操作指令执行时,EDI会随ESI同步递增/递减;部分指令默认将EDI作为目的地址寄存器(如

stosb,将AL的值存入EDI指向的内存); -

典型场景:

内存数据清零时,EDI存储要清零的内存起始地址,AL存储0,rep stosb指令自动将EDI指向的连续内存单元赋值为0; -

文件数据读取时,ESI指向硬盘缓冲区地址(源),EDI指向内存缓冲区地址(目的),通过数据块复制指令将文件数据写入内存;

-

兼容模式:低16位为DI(目的变址寄存器)。

7. EBP:基址指针寄存器——栈帧的“基准锚点”

-

核心用途:维护函数调用时的“栈帧结构”,存储当前栈帧的基地址,用于定位函数参数和局部变量;

-

硬件约定:函数调用时,EBP会被压入栈中保存,然后将ESP的值赋给EBP(以ESP为基准建立新栈帧);函数执行过程中,通过“EBP+偏移量”访问参数(如EBP+8访问第一个参数),通过“EBP-偏移量”访问局部变量(如EBP-4访问第一个局部变量);函数返回时,从栈中恢复EBP的值;

-

典型场景:

函数int add(int a, int b)调用时,EBP建立栈帧后,通过mov eax, [ebp+8]读取参数a,mov ebx, [ebp+0xC]读取参数b; -

函数内定义局部变量

int c = 0时,通过mov [ebp-4], 0将0存入局部变量c的内存位置; -

兼容模式:低16位为BP(基址指针寄存器),适配16位栈帧。

8. ESP:栈指针寄存器——栈的“动态顶针”

-

核心用途:存储当前栈的“栈顶地址”,控制栈的压入(push)和弹出(pop)操作;

-

硬件约定:栈是“向下生长”的(栈顶地址随数据压入而减小),

push指令执行时,ESP先减4(32位数据),再将数据存入ESP指向的栈顶位置;pop指令执行时,先从ESP指向的栈顶读取数据,再将ESP加4;函数调用时,返回地址会被自动压入栈,ESP同步更新; -

典型场景:

压入数据:push eax将EAX的值压入栈,ESP = ESP - 4; -

弹出数据:

pop ebx将栈顶数据弹出到EBX,ESP = ESP + 4; -

函数返回:

ret指令将栈顶的返回地址弹出到PC寄存器,ESP自动更新,程序跳回调用方继续执行; -

兼容模式:低16位为SP(栈指针寄存器)。

四、32位通用寄存器如何组成复杂电路?栈帧与流水线协同

单个通用寄存器的功能有限,8个寄存器通过“栈帧结构”“流水线协同”等方式组成复杂电路,支撑函数调用、多任务执行等高级功能——这是32位x86架构能实现复杂程序运行的核心。

1. 栈帧电路:EBP与ESP的协同,支撑函数调用与参数传递

栈帧是函数调用时的“内存隔离区域”,由EBP(基址)和ESP(栈顶)共同定义,配合其他通用寄存器组成完整的栈帧电路:

-

组成逻辑:以EBP为固定基址,ESP为动态栈顶,两者之间的内存区域为当前函数的栈帧;配合EAX(返回值)、ESI/EDI(数据传输)实现函数的参数传递、局部变量存储和返回值传递;

-

工作流程(函数调用-执行-返回):

调用方压入函数参数:push b、push a(参数从右到左压栈),ESP递减8; -

调用方压入返回地址:

call add,返回地址(下一条指令地址)压栈,ESP递减4; -

被调用方建立栈帧:

push ebp(保存旧EBP),mov ebp, esp(新EBP = 当前ESP),sub esp, 4(为局部变量分配4字节空间); -

被调用方执行运算:通过

[ebp+8]、[ebp+0xC]读取参数a、b,存入EAX和EBX,运算结果存入EAX; -

被调用方销毁栈帧:

mov esp, ebp(释放局部变量空间),pop ebp(恢复旧EBP); -

被调用方返回:

ret弹出返回地址到PC,ESP递增4,调用方通过add esp, 8释放参数空间。 -

核心价值:实现函数的“隔离执行”——不同函数的栈帧相互独立,局部变量不会相互干扰;同时,通过EBP的基址定位,确保参数和局部变量的精准访问。

2. 流水线协同电路:寄存器与流水线阶段的衔接

32位x86 CPU采用“流水线技术”(如5级流水线:取指-解码-执行-访存-写回),通用寄存器与流水线各阶段通过“流水线寄存器”衔接,组成协同电路:

-

组成逻辑:在流水线各阶段之间插入专用寄存器(如取指-解码寄存器、解码-执行寄存器),存储前一阶段的处理结果(如指令、寄存器地址、数据);通用寄存器与执行阶段的ALU直接对接,提供运算数据和存储运算结果;

-

工作逻辑:

取指阶段:PC寄存器提供指令地址,读取指令存入取指-解码寄存器; -

解码阶段:解读指令中的寄存器操作(如

add eax, ebx),通过寄存器选择器选中EAX和EBX,将其地址存入解码-执行寄存器; -

执行阶段:从EAX和EBX读取数据传入ALU运算,结果存入执行-访存寄存器;

-

写回阶段:将运算结果写入EAX寄存器,完成一次指令执行。

核心价值:让多条指令并行执行(如指令1在执行时,指令2在解码),大幅提升CPU的指令吞吐量——通用寄存器的高速读写能力,确保流水线不会因数据不足而阻塞。

五、32位通用寄存器在计算机系统中的核心应用

32位通用寄存器是32位x86计算机系统的“核心数据处理枢纽”,所有程序的执行、数据的传输、任务的切换都离不开它们——从简单的加减运算到复杂的多任务操作系统,都依赖其高效工作。

1. 程序执行的核心载体:指令的“数据操作台”

任何程序(无论是C、Java还是Python)最终都会被编译为汇编指令,而汇编指令的执行本质就是对通用寄存器的操作:

-

运算类指令:

add、sub、mul等指令,直接操作EAX、EBX等寄存器完成运算; -

数据传输指令:

mov指令将内存数据写入寄存器,或把寄存器数据写入内存; -

控制类指令:

loop、jmp等指令,通过ECX(计数)、EBP/ESP(栈帧)实现程序流程控制。

举例:C语言代码int c = a + b;编译后的汇编指令为:

mov eax, [a] ; 将内存中a的值写入EAX

mov ebx, [b] ; 将内存中b的值写入EBX

add eax, ebx ; EAX = EAX + EBX(运算)

mov [c], eax ; 将EAX的结果写入内存c的地址

可见,程序的运算过程完全依赖通用寄存器作为“临时操作台”。

2. 多任务切换的关键:寄存器上下文保存与恢复

32位操作系统(如Windows XP)支持多任务并发执行,核心是“寄存器上下文切换”——当CPU从一个任务切换到另一个任务时,会将当前任务的所有通用寄存器值(上下文)保存到内存,切换完成后再从内存恢复目标任务的寄存器上下文:

-

切换流程:

操作系统触发任务切换(如时钟中断); -

将当前任务的EAX、EBX、ECX、EDX、ESI、EDI、EBP、ESP等寄存器值压入内存的任务控制块(TCB);

-

从目标任务的TCB中,将保存的寄存器值恢复到对应的通用寄存器;

-

更新PC寄存器的值,切换到目标任务的指令继续执行。

-

核心价值:实现任务的“无缝切换”——每个任务都认为自己独占CPU,因为其寄存器状态被完整保存和恢复。

3. 内存访问的核心定位:地址计算与数据传输

32位通用寄存器是CPU访问内存的“地址定位器”,通过“基址+变址+偏移量”的寻址方式,实现对复杂内存区域的精准访问:

-

寻址方式举例:

基址+偏移量:mov eax, [ebx + 8](EBX为基址,8为偏移量); -

基址+变址:

mov eax, [ebx + esi](EBX为基址,ESI为变址); -

基址+变址+偏移量:

mov eax, [ebx + esi + 4]。

应用场景:访问二维数组、结构体数组等复杂数据结构——比如二维数组int arr[M][N],基址EBX存储数组起始地址,ESI存储行索引,偏移量为列索引×4,通过[ebx + esi*N*4 + col*4]定位元素。

六、与编程的深度关联:搞懂寄存器,才能写好底层代码

很多高级语言程序员觉得“寄存器与我无关”,但实际上,寄存器的设计逻辑直接影响代码的执行效率、调试难度和底层兼容性。理解32位通用寄存器,是从“会写代码”到“写好底层代码”的关键。

1. 汇编编程的核心:直接操作寄存器实现功能

汇编语言是“直接操作寄存器和内存”的语言,所有汇编指令都围绕通用寄存器展开——不懂寄存器的用途,就无法编写和读懂汇编代码:

-

举例:实现“从键盘读取一个字符并输出”的汇编代码,核心依赖EDX(I/O端口地址)、AL(数据存储):

mov edx, 0x60 ; EDX存储键盘I/O端口地址0x60 in al, dx ; 从键盘端口读取字符存入AL mov edx, 0x61 ; EDX存储显示器I/O端口地址0x61 out dx, al ; 将AL中的字符输出到显示器 -

应用场景:操作系统内核开发、嵌入式编程、性能极致优化——这些场景需要直接操作寄存器,实现对硬件的精准控制。

2. 高级语言优化:理解寄存器分配,提升代码效率

编译器会自动将高级语言中的变量分配到通用寄存器(寄存器分配优化),理解寄存器的用途和数量限制,能帮助我们写出更易被编译器优化的代码:

-

优化原则1:减少频繁访问的变量数量:32位x86只有8个通用寄存器,若频繁访问的变量超过8个,编译器会将部分变量“溢出”到内存(称为“溢出变量”),导致访问速度变慢;编程时应尽量合并变量,减少高频变量数量;

-

优化原则2:循环变量优先用局部变量:局部变量更易被编译器分配到ECX(计数器)等寄存器,而全局变量因可能被多线程修改,通常存储在内存;比如循环变量

i定义为局部变量,编译器会自动将其分配到ECX,配合loop指令实现高效循环; -

优化原则3:避免不必要的参数传递:函数参数通过栈传递(超过寄存器数量时),栈访问速度比寄存器慢;编程时应尽量减少函数参数数量(优先使用3-4个参数),或通过结构体指针传递多个参数(指针占1个寄存器)。

3. 程序调试:通过寄存器状态定位底层问题

调试底层代码(如汇编、内核代码)时,寄存器的状态是定位问题的关键——调试器(如GDB)会显示所有通用寄存器的值,通过分析这些值可快速定位问题:

-

定位循环问题:若循环无法结束,查看ECX的值——若ECX始终不为0,可能是循环条件逻辑错误;

-

定位函数调用问题:若函数返回值错误,查看EAX的值——若EAX的值不符合预期,可能是函数内部运算错误;若函数参数读取错误,查看EBP+偏移量对应的内存值(通过EBP定位参数位置);

-

定位栈溢出问题:栈溢出会破坏EBP和ESP的值,若调试时发现EBP的值异常(如指向非法内存地址),大概率是栈溢出导致栈帧被破坏。

4. 理解数据类型与内存布局:寄存器宽度决定数据范围

32位通用寄存器的宽度(32位)直接决定了32位系统中数据类型的范围:

-

int类型:32位,范围为-2³¹2³¹-1(-21474836482147483647),正好匹配EAX等寄存器的宽度;

-

指针类型:32位,可存储4GB范围内的内存地址,与寄存器的地址存储能力匹配;

-

编程启示:在32位系统中,避免使用超过32位的数据类型(如64位long long),否则会导致编译器拆分数据,通过多个寄存器协同存储,大幅降低效率。

七、寄存器是底层逻辑的“万能钥匙”

以前学习汇编时,我只是死记硬背“EAX存返回值、ECX是计数器”,但不理解为什么这么设计。现在明白:32位通用寄存器的8个成员,每一个的用途都与x86架构的指令集、内存模型、函数调用规范深度绑定——它们不是孤立的硬件单元,而是协同工作的“数据处理体系”。

理解32位通用寄存器,最大的价值不是为了写汇编代码,而是为了“看透程序的底层执行逻辑”:为什么局部变量比全局变量快?为什么函数参数不宜过多?为什么多任务切换会有开销?这些问题的答案,都藏在寄存器的设计和工作原理中。

对于程序员而言,底层认知是拉开差距的关键——而32位通用寄存器,就是打开底层认知大门的“万能钥匙”。它能帮你从硬件视角理解代码的执行效率,精准定位底层bug,写出更适配硬件的高效代码。

1101

1101

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?