本章介绍了设备的USB。

16.1 Introduction

USB控制器通过提供在线路/总线速度高达480Mbps的USB设备之间进行数据传输的机制,为许多消费者便携式设备提供了低成本的连接解决方案。设备USB子系统有两个独立的USB 2.0模块,围绕两个OTG控制器构建。还支持OTG补充功能,即对动态角色更改的支持。每个端口都支持双重角色功能,从而实现额外的多功能性,从而实现主机或外围设备的操作能力。两个端口具有相同的功能,并且彼此独立运行。

每个USB控制器都是围绕Mentor USB OTG控制器(musbmhdrc)和TI PHY构建的。每个USB控制器都有用户可配置的32K字节端点FIFO,并支持15“传输”

端点和除端点0之外的15个“接收”端点。USB子系统利用CPPI 4.1 DMA通过专用DMA硬件加速数据移动。

两个USB模块共享CPPI DMA控制器和随附的队列管理器、中断起搏器、电源管理模块和PHY/UTMI时钟。

在接下来对USB子系统的描述中,术语USB控制器或USB PHY用于表示/指代存在于USB子系统内的两个USB控制器或PHY中的任何一个。术语USB模块用于表示/指两个USB模块中的任何一个。USB0用于指代USB模块中的一个,USB1用于指代另一个USB模块。

16.1.1首字母缩略词、缩写词和定义

AHB | Advanced High-performance Bus |

CBA | Common Bus Architecture |

CDC | Change Data Capture |

CPPI | Communications Port Programming Interface |

CPU | Central Processing Unit |

DFT | Design for Test |

DMA | Direct Memory Access |

DV | Design Verification |

EOI | End of Interrupt |

EOP | End of Packet |

FIFO | First-In First-Out |

FS | Full-Speed USB data rate |

HNP | Host Negotiation |

HS | High-Speed USB data rate |

INTD | Interrupt Distributor |

IP | Intellectual Property |

ISO | Isochronous transfer type |

LS | Low-Speed USB data rate |

MHz | Megahertz |

MOP | Middle of Packet |

OCP | Open Core Protocol |

OCP HD | OCP High Performance |

OCP MMR | OCP Memory Mapped Registers |

OTG | On-The-Go |

PDR | Physical Design Requirements |

PHY | Physical Layer Device |

PPU | Packet Processing Unit |

RAM | Random Access Memory |

RNDIS | Remote Network Driver Interface Specification |

RX | Receive |

SCR | Switched Central Resource |

SOC | System On a Chip |

SOP | Start of Packet |

SRP | Session Resume |

TX | Transmit |

USB | Universal Serial Bus |

USB0 | One of the two USB 2.0 Compliant USB Module |

USB1 | One of the two USB2.0 Compliant USB Module |

USBSS | USB Subsystem (contains USB0 and USB1) |

UTMI | USB 2.0 Transceiver Macrocell Interface |

XDMA | Transfer DMA (DMA other than CPPI DMA used within the Controller) |

16.1.2 USB功能

USB子系统的主要功能是:

•包含2个usb20otg_f控制器模块,具有以下功能:

–围绕Mentor USB 2.0 OTG核心(musbmhdrc)构建

–支持USB 2.0外围设备,速度为HS(480 Mb/s)和FS(12 Mb/s)

–支持USB 2.0主机或OTG,速度为HS(480 Mb/s)、FS(12 Mb/s)和LS(1.5 Mb/s)

–支持所有传输模式(控制、批量、中断和同步)

–支持高带宽ISO模式

–支持16个发送(TX)和16个接收(RX)端点,包括端点0

–支持用于会话恢复(SRP)和主机协商(HNP)的USB OTG扩展

–包括一个32K端点FIFO RAM,并支持可编程FIFO大小

–包括RNDIS模式,用于加速使用短数据包终止的RNDIS类型协议

通用串口总线

–包括CDC Linux模式,用于通过短数据包终止加速CDC类型的协议

通用串口总线

–包括类似RNDIS的模式,用于在不使用短数据包的情况下终止RNDIS类型的协议

为支持MSC应用程序而终止

•包括两个USB2.0 OTG PHY

•通过3个OCP接口与CPU接口:

–DMA的主OCP HP接口

–队列管理器的主OCP HP接口

–从OCP MMR接口

•包括一个符合CPPI 4.1的DMA控制器子模块,具有30个RX和30个TX同时数据

连接

•包括一个CPPI 4.1 DMA调度器

•DMA支持CPPI主机描述符格式

•DMA支持因缓冲区不足而暂停

•支持高达4M字节的数据缓冲区

•每个TX/RX端点的CPPI FIFO接口

•提供具有92个队列的CPPI队列管理器模块,用于排队/取消排队数据包。

•中断的DMA定步逻辑

•使用UTMI接口进行环回MGC测试

16.1.3不支持的USB OTG和PHY功能

此设备支持USBOTG模块主机、设备和OTG功能。

16.2集成

该设备实现USB2.0 OTG双端口模块和PHY,用于作为外围设备或主机与USB接口。

图16-1显示了USB模块在此设备上的集成。

16.2.1 USB连接属性

USB模块本身具有大量的中断输出。为了便于集成,这些输出都被路由到一对中断聚合器。这些聚合器块在第一次出现来自模块的USB或DMA逻辑的任何中断时生成单个中断。

USB时钟和复位管理

每个USB控制器都有一个PHY模块,用于生成UTMI时钟。UTMI时钟在用于60MHz(480Mb/s)的8位接口的UTMI规范中是固定的。PHY需要低抖动的960MHz源时钟。

16.2.3 USB引脚列表

USB外部接口信号如表16-3所示。

16.2.4 USB GPIO详细信息

USB模块支持将DP和DM引脚配置为直通GPIO。在该设备中,GPIO模式用于提供UART over USB接口功能。芯片级逻辑允许UART TX/RX数据信号在正常或反相状态下连接到DP或DM,如图16-2所示。该图显示了UART2/USB0端口的实现。此逻辑也被复制到UART3/USB1端口。

16.2.5 USB未绑定PHY焊盘

USBOTGSS包括两个USB PHY模块。在只有1个PHY连接到引脚的封装上

(例如13x13包装),必须遵循以下程序,以确保未粘合

PHY焊盘不会导致USBOTGSS操作出现问题:

•必须通过设置USB Core DEVCTL寄存器的Bit2将与未绑定PHY相对应的USB控制器置于主机模式。

•必须通过设置USB Core POWER寄存器的Bits[1:0]将未绑定PHY置于SUSPEND状态。

•与未绑定PHY相对应的控制模块USB_CTRLx寄存器必须具有如下编程位,如图所示:

–CHGDET_DIS=1

–CM_PWRDN=1

–GPIOMODE=0

16.3功能描述

除了端点0之外,设备中的USB控制器还支持15个传输端点和15个接收端点。(这些端点用于IN和OUT事务取决于USB控制器是用作设备/外围设备还是用作主机。当用作外围设备时,IN事务通过TX端点处理,OUT事务通过Rx端点处理。当用作主机时,IN事务通过Rx端点处理,OUT事务通过TX端点处理。)

这些额外的端点可以在软件中单独配置,以处理批量传输(这也允许它们处理中断传输)、同步传输或控制传输。此外,端点还可以动态分配给不同的目标设备功能,从而最大限度地增加可以同时支持的设备数量。

每个端点都需要在FIFO中分配一块内存来与之关联。USB模块有一块FIFO RAM(大小为32 KB),供所有端点共享。端点0的FIFO要求为64字节深,并将缓冲1个数据包。FIFO RAM的前64字节由硬件为端点0的使用保留,因此用户软件不需要(也没有能力)为端点0分配FIFO。FIFO RAM的其余部分可由用户配置其他端点FIFO的大小可以是8到8192字节并且可以缓冲1个或2个分组。

单独的FIFO可以与每个端点相关联:或者,具有相同端点编号的TX端点和Rx端点可以配置为使用相同的FIFO,例如,以减少所需的RAM块的大小,前提是它们永远不能同时处于活动状态。

USB控制器承担的角色(主机或设备)由用户固件对USB子系统空间内定义的相应USB控制器MODE寄存器进行编程来选择。请注意,一些USB引脚尚未绑定,这些引脚的功能由用户软件通过专用寄存器控制。

用户可以通过OCP从机接口通过CPU访问控制器。用户可以完全从CPU处理USB事务,也可以使用DMA来执行数据传输。CPPI DMA可以用于服务端点1到15,而不是端点0。CPU访问方法用于为终结点0事务提供服务。

16.3.1 VBUS电压源控制

当任何USB控制器承担主机的角色时,USB需要通过其VBUS线向连接的设备提供5V电源。为了实现这一任务,USB控制器需要使用能够提供5V电源的外部电源逻辑(或电荷泵)。

USB_DRVVBUS用作控制信号,以启用/禁用该外部电源逻辑,从而在VBUS线上供电或禁用电源。USB_DRVVBUS上的控制是自动的,由USB控制器处理。只要适当的硬件连接和软件初始化到位,控制就应该对用户透明。当USB控制器在会话中扮演主机角色时,USB控制器将USB_DRVVBUS信号驱动为高电平。当承担设备的角色时,控制器将USB_DRVVBUS信号驱动为低电平,从而禁用外部电荷泵/电源逻辑;因此,VBUS线上没有电力被驱动(在这种情况下,电力预计由外部主机提供)。

请注意,两个USB都是自供电的,并且当承担设备的角色时,设备不依赖由外部主机提供的VBUS线上的电压来进行控制器操作。VBUS上的电源用于识别主机的存在。它还用于为D+线上的上拉供电。

USB PHY将持续监测VBUS上的电压,并将状态报告给USB控制器。

16.3.2上拉/下拉电阻器

由于USB控制器是双重角色控制器,能够承担主机或设备的角色,因此所需的上拉/下拉电阻器不能存在于设备外部。这些上拉/下拉电阻器存在于设备内部,更具体地说,存在于PHY内,并且基于控制器所承担的允许动态硬件配置的角色来启用和禁用。当承担主机的角色时,数据线被启用内部15K欧姆电阻器的PHY拉低。当承担设备的角色时,D+线上所需的15K欧姆上拉电阻器会自动启用,以向作为FS设备的外部主机表示USB能力(HS操作在重置总线条件期间协商)

16.3.3角色扮演方法

对于OTG控制器,控制器承担主机或辅助设备角色所遵循的通常方法由ID引脚的状态控制,而ID引脚又由USB电缆连接器类型控制。

该设备已将这些ID引脚连接起来,并允许直接从连接器处理控制,即USB控制器将根据插入迷你或微型A/B连接器的电缆端承担角色。一种替代方法,其中ID引脚信号被旁路,并且固件通过寄存器访问来控制控制器所承担的角色,从而允许对不需要使用USB ID引脚的系统进行额外控制。在这种情况下,USBnMODE[Bit7=IDDIG_MUX]需要使用值1进行编程,以便使用寄存器编程。

两个寄存器,偏移量为10E8h的USB0模式寄存器和偏移量为18E8h的USB 1模式寄存器,用于用户选择USB控制器承担的角色。用户需要在USB控制器进行会话之前对相应的寄存器进行编程。

16.3.4时钟、PLL和PHY初始化

在配置USB模块寄存器之前,需要解除USB子系统和PHY的重置,启用互连和控制器时钟,并使用适当的设置配置USB PHY。并非所有与此任务相关的寄存器都包含在本文档中。有关PHY配置寄存器的定义,请参阅时钟和控制模块的PRCM。

16.3.5索引和非索引寄存器空间

USB控制器提供了两种用于访问端点控制和状态寄存器的机制;索引和非索引方法。

索引的端点控制/状态寄存器空间。这个寄存器空间可以被认为是一个由代理寄存器填充的区域。对于USB0,该寄存器空间是偏移1410h到141Fh处的存储器映射区域,对于USB1,该寄存器区域是偏移1C10h到1C1Fh处的存储映射区域。在该区域映射的端点寄存器空间是通过对控制器的相应INDEX寄存器(分别用于USB0和USB1的@offset 140Eh和1C0Eh)进行编程来选择的。

通过使用相应的端点编号对INDEX寄存器进行编程,可以从此索引区域访问与该特定端点对应的控制和状态寄存器。换句话说,索引寄存器区域充当访问选定端点寄存器的代理。无索引端点控制/状态寄存器空间。这些区域是专用端点寄存器,内存映射驻留在USB0的偏移1500h到16FFh以及USB1的偏移1D00h到1EFFh。寄存器在偏移1500h到150Fh处属于端点0;偏移1510h到151Fh处的寄存器属于端点1…并且最后偏移16F0h到16FFh处的暂存器属于USB0的端点15。类似地,偏移1D00h到1E0Fh处的寄存器属于端点0;偏移量1D10h到1D1Fh处的寄存器属于端点1…并且最后偏移量1DF0h到1DFFh处的暂存器属于USB1的端点15。

这允许用户/固件直接从端点寄存器区域的唯一空间访问端点寄存器区域,如在非索引区域内指定的,或者通过对相应的索引寄存器进行编程从代理空间访问。

注:控制和状态寄存器/区域适用于给定端点的Tx和Rx。也就是说,端点1 Tx和端点1 Rx寄存器占用相同的寄存器空间。

有关USB控制器寄存器的详细信息,请参阅第16.5节

16.3.6动态FIFO大小

每个USB模块总共支持32K字节的FIFO RAM,以便将FIFO动态分配给所有正在使用的端点。每个端点都需要一个FIFO与之关联。每个端点有一组寄存器可用于FIFO分配,不包括端点0。FIFO配置寄存器是索引寄存器,不能直接访问;通过访问代理寄存器进行配置。地址140Eh或1C0Eh处的INDEX寄存器必须设置为适当的端点。换句话说,端点FIFO配置寄存器不具有非索引区域。

将FIFO空间分配给不同的端点需要使用以下信息为每个Tx和Rx端点编程:

•RAM块内FIFO的起始地址

•支持的最大数据包大小

•是否需要双重缓冲

(最后两个共同定义了需要分配给FIFO的空间量。)

固件有责任确保在当前USB配置中活动的所有Tx和Rx端点(端点0除外)都分配了一块FIFO RAM供其使用。端点0所需的最大FIFO大小为64字节深,足够缓冲一个数据包。由于这个原因,FIFO存储器的前64个字节被保留给端点0使用,并且该资源分配被暗示在任何时候都是可用的,并且端点0不需要FIFO分配。

对于端点0以外的端点,FIFO RAM接口是可配置的,并且必须具有最小8字节的大小,并且应该能够缓冲1或2个数据包。单独的FIFO可以与每个端点相关联:或者,具有相同端点编号的Tx端点和Rx端点可以配置为使用相同的FIFO,以减少所需的RAM块的大小,前提是它们永远不能同时处于活动状态。

注意:动态设置FIFO大小的选项仅适用于端点1-15。端点0 FIFO具有固定大小(64字节)和固定位置,该位置是FIFO的第一个64字节(FIFO地址0-63)。

16.3.7 USB控制器主机和外围设备模式操作

这两个USB模块可以在一系列不同的环境中使用。它们可以用作高速或全速USB外围设备,以点对点类型的布置连接到传统的USB主机(例如PC)。作为主机,USB模块也可以点对点排列与任何速度(高速、全速或低速)的另一个外围设备一起使用,或者可以在多点设置中用作一系列外围设备的主机;通过集线器一对多。请注意,每个USB控制器所承担的角色是相互独立的。USB角色假设/配置有两个选项(h/w或s/w)。

对于USB外围设备配置,用户可以选择使用电缆端通过连接电缆的迷你或微型b侧来选择角色(可以将其视为h/w选项),或者使用可选方法,其中需要固件在USB控制器进入会话之前用值“1”对相应的USB模式寄存器IDDIG位字段进行编程(可以将此视为s/w选项)。

类似地,对于USB主机配置,用户可以选择使用电缆端通过连接电缆的迷你或微型a侧来选择角色(可以将其视为h/w选项),或者使用可选方法,其中需要固件在USB控制器进入会话之前用“0”值编程相应的USB模式寄存器IDDIG位字段(可以将此视为s/w选项)。

当使用s/w选项时,USB ID引脚状态被忽略/绕过(这是一种类似的配置,其中不存在ID引脚),主机或外围设备(设备)的USB2.0控制器角色自适应取决于相应USB模式寄存器IDDIG字段的状态。如果用户在USB进入会话之前将IDDIG字段编程为值“1”,则它将扮演外围设备/设备的角色。但是,如果IDDIG字段被编程为值“0”,USB控制器将扮演主机的角色。这意味着,将无法控制OTG控制器的角色,并且用户需要在执行USB连接之前了解固件程序设置。USB2.0 OTG控制器确定其操作模式(USB控制器承担主机或外围设备的角色)的过程在USB 2.0控制器进入会话时开始。当USB 2.0控制器感测到USBx_VBUSIN引脚上的电压(>=4.4V)并且控制器设置其DEVCTL[session]位字段时,或者当固件设置DEVCTL[session]比特时,USB 2.0控制器处于会话中;假设它将作为主机运行。

当DEVCTL[SESSION]位被设置时,控制器将开始感测Iddig信号的状态,该信号又由USBx_ID引脚(h/w选项)或模式寄存器的Iddig位字段(s/w选项)控制。如果发现iddig信号的状态为低(iddig用“0”编程),则USB2.0控制器将扮演主机的角色,当发现iddig信号为高(iddig用“1”编程)时,则其将扮演设备的角色。请注意,iddig是一个内部信号,可以通过专用寄存器的固件将其驱动到高电平或低电平。

当USB控制器确定其作为主机的角色时,它将驱动USBx_DRVVBUS引脚为高电平,以启用外部电源逻辑,从而开始提供所需的5V电源(必须≥4.4V,但为了考虑电缆上的电压降,建议在4.75V附近)。然后,USB2.0控制器将等待USBx_VBUSIN的电压变高。100毫秒后,如果它没有看到USBX_VBUSIN引脚上的电压在Vbus有效范围内(>=4.4V),它将产生Vbus错误中断。假设发现USBX_VBUSIN的电压电平在Vbus Valid范围内,则USB 2.0主机控制器将等待设备连接;即它看到它的一条数据线USB0/1_DP/DM被拉高。当承担外围设备的角色时,假设固件已经设置了POWER[SOFTCON]位,并且USBx_ID引脚是浮动的(h/w选项)或者USBx模式寄存器IDDIG位字段被编程为“1”(s/w选项)并且外部主机正在USBx_VBUSIN线上供电,则USB2.0控制器将设置DEVCTL[SESSION]位,指示控制器进入会话。并不是说USBx_VBUSIN引脚上的电压必须在Vbus有效范围内(即大于或等于4.4V)。当控制器进入会话时,它将迫使USB2.0控制器感测iddig信号的状态。一旦它检测到iddig信号为高电平,它将启用其1.5Kohm上拉电阻器,以向外部主机表明它是全速设备。请注意,即使在作为高速外围设备进行操作时;USB控制器必须首先设置为全速,然后再转换为高速。然后,USB2.0控制器将等待来自外部主机的重置信号。然后,如果选择了高速选项,它将协商高速操作,如果主机接受了它的请求,它将在数据线上启用其精度为45欧姆的终端电阻器(以停止信号反射),并禁用1.5Kohm的电阻器。

16.3.8协议描述

本节介绍USB模块对USB协议的实现

16.3.8.1 USB控制器外围模式操作

当USBx_ID引脚浮动或USB模式寄存器[idig=bit8]在控制器进入会话之前被用户应用程序设置为1(前提是iddig_mux,即USBnMODE的bit7也被设置为1)时,USB控制器承担外围设备的角色。当USB控制器进入会话时,它将扮演设备的角色。

软连接–POR或USB模块软复位后,POWER寄存器的SOFTCONN位(第6位)被清除为0。因此,控制器将显示为断开状态,直到软件将SOFTCONN位设置为1。然后,应用软件可以选择何时将PHY设置为其正常模式。初始化过程较长的系统可能会使用此方法来确保初始化完成,并且系统已准备好在连接到USB之前执行枚举。一旦设置了SOFTCONN位,软件也可以通过将该位清除为0来模拟断开。

进入挂起模式–当作为外围设备运行时,控制器监测总线上的活动,当3毫秒内没有活动发生时,控制器进入挂起方式。如果已启用挂起中断,此时将生成一个中断。此时,控制器可以保持活动状态(因此能够检测USB上何时发生Resume信令),或者应用程序可以安排通过停止其时钟来禁用控制器。然而,如果时钟没有运行,控制器将无法检测到USB上的Resume信号。如果是这种情况,将需要外部硬件来检测恢复信令(通过监测DM和DP信号),以便可以重新启动到控制器的时钟。

恢复信号——当总线上出现恢复信号时,如有必要,必须首先重新启动控制器的时钟。然后控制器将自动退出挂起模式。如果恢复中断被启用,将产生一个中断。启动远程唤醒-如果软件希望在控制器处于挂起模式时启动远程唤醒,则应将POWER[RESUME]位设置为1。软件应将该位设置保留约10ms(最小2ms,最大15ms),然后将其重置为0。

注意:当软件启动远程唤醒时,不会产生恢复中断。

重置信号——当总线上出现重置信号或总线状况时,控制器执行以下操作:

•将FADDR寄存器清除为0

•将INDEX寄存器清除为0

•清除所有端点FIFO

•清除所有控制器控制/状态寄存器

•生成重置中断

•启用核心级别的所有中断。

如果POWER寄存器内的HSENA位(位5)被设置,则控制器也尝试协商高速操作。是否选择高速操作由POWER寄存器的HSMODE位(位4)指示。当应用程序软件接收到重置中断时,它应该关闭任何打开的管道并等待总线枚举开始。

16.3.8.2 USB控制器主机模式操作

当USBx_ID引脚状态接地或USB模式寄存器[idig=bit8]在控制器进入会话之前被用户应用程序清除为0(前提是iddig_mux,即USBnMODE的bit7也被设置为1)时,USB控制器承担主机的角色。当USB控制器进入会话时,应用程序/固件将DEVCTL[session]位设置为1,它将承担主机的角色。

•进入暂停模式。当作为主机操作时,可以通过在POWER寄存器中设置SUSPENDM位来提示USB控制器进入挂起模式。当该位被设置时,控制器将完成当前事务,然后停止事务调度器和帧计数器。

不会启动进一步的事务,也不会生成SOF数据包。

如果设置了ENSUSPM位(POWER寄存器的位0),则当控制器进入挂起模式时,UTMI+PHY将进入低功率模式。

•发送恢复信号。当应用程序要求控制器离开挂起模式时,它需要清除POWER寄存器中的SUSPENDM位,设置RESUME位,并保持设置20ms。当RESUME位为高时,控制器将在总线上产生RESUME信号。之后20ms,CPU应清除RESUME位,此时帧计数器和事务调度程序将启动。

•响应远程唤醒。如果在控制器处于挂起模式时从目标检测到Resume信令,则UTMI+PHY将退出低功率模式,并重新启动UTMI时钟。

然后,控制器将退出暂停模式,并自动将POWER寄存器中的RESUME位(位2)设置为“1”,以接管从目标生成RESUME信号。如果启用了恢复中断,将生成一个中断。

•重置信号。如果在控制器处于主机模式时设置了POWER寄存器中的RESET位(第3位),它将在总线上生成RESET信号。如果POWER寄存器中的HSENAB位(位5)被设置,它也将尝试协商高速操作。软件应保持RESET位设置至少20ms,以确保目标设备的正确复位。在软件已经清除该位之后,

控制器将启动其帧计数器和事务调度器。是否选择高速操作将由POWER寄存器的HSMODE位(位4)指示

16.3.8.2.1控制事务:主机模式

主机控制事务通过端点0进行,并且需要软件来处理可能通过端点0发送或接收的所有标准设备请求(如通用串行总线规范,修订版2.0中所述)。端点0只能通过CPU提供服务,不能使用DMA模式。

有三类标准设备请求需要处理:零数据请求(其中所有信息都包含在命令中);写入请求(其中命令后面将跟着附加数据);以及读取请求(其中要求设备将数据发送回主机)。

1.零数据请求包括SETUP命令和IN状态阶段。

2.写入请求包括SETUP命令,后面跟着OUT数据阶段,OUT数据阶段又跟着in状态阶段。

3.读取请求包括SETUP命令,后面跟着IN数据阶段,IN数据阶段又跟着OUT状态阶段。

可以设置超时以限制主机控制器将重试被目标持续NAKed的事务的时间长度。这个限制可以在2到2个15帧/微帧之间,并且是通过NAKLIMIT0寄存器设置的。

以下部分通过查看控制事务的不同阶段要采取的步骤,描述了CPU在发出这些不同类型的请求时需要采取的操作。

注意:在作为主机启动任何事务之前,需要设置FADDR寄存器以寻址外围设备。首次连接设备时,应将FADDR设置为零。发出SET_ADDRESS命令后,应将FADDR设置为目标的新地址。

6.3.8.2.1.1控制事务的设置阶段:主机模式

对于控制事务的设置阶段(图16-8),驱动USB主机设备的软件需要:

1.将所需设备请求命令的8个字节加载到端点0 FIFO

2.设置SETUPPKT和TXPKTRDY(分别为HOST_CSR0的位3和1)。

注意:必须将这些位设置在一起。

然后,控制器继续向被寻址设备的端点0发送SETUP令牌,然后发送8字节命令/请求,必要时重试。注意:出现错误时,控制器会重试事务三次。

3.在发送8字节请求数据的尝试结束时,控制器将生成Endpoint 0中断。然后,软件应读取HOST_CSR0,以确定是否设置了RXSTALL位(位2)、ERROR位(位4)或NAK_TIMEOUT位(位7)。

如果设置了RXSTALL,则表示目标未接受该命令(例如,因为目标设备不支持该命令),因此已发出STALL响应。如果设置了ERROR,则表示控制器已尝试发送SETUP数据包和以下数据包三次,但没有得到任何响应。

如果设置了NAK_TIMEOUT,则意味着控制器已接收到对每次发送SETUP数据包的尝试的NAK响应,时间长于HOST_NAMEKLIMIT0中设置的时间。然后,可以通过清除NAK_TIMEOUT位,或者在清除NAK_TIMEOUT位之前通过刷新FIFO来中止事务。

4.如果未设置RXSTALL、ERROR或NAK_TIMEOUT,则SETUP Phase(设置阶段)已被正确确认,并且软件应进入为特定标准设备请求指定的以下IN数据阶段、OUT数据阶段或IN状态阶段。

16.3.8.2.1.2控制事务的数据阶段(IN数据阶段):主机模式

对于控制事务的IN数据阶段(图16-9),驱动USB主机设备的软件需要

1.设置HOST_CSR0的REQPKT位(位5)

2.等待控制器发送IN令牌并接收所需的数据。

3.当控制器产生端点0中断时,读取HOST_CSR0以确定RXSTALL位(位2)、ERROR位(位4)、NAK_TIMEOUT位(位7)或RXPKTRDY位(位0)是否已被设置。

如果设置了RXSTALL,则表示目标已发出STALL响应。

如果设置了ERROR,则表示控制器已尝试发送所需的IN令牌三次,但没有得到任何响应。如果设置了NAK_TIMEOUT位,则意味着控制器已经接收到对每次发送IN令牌的尝试的NAK响应,持续时间长于HOST_NAMEKLIMIT0中设置的时间。这个然后可以指示控制器通过清除NAK_TIMEOUT位来继续尝试该事务(直到它再次超时),或者通过在清除NAK_ TIMEOUT位之前清除REQPKT来中止该事务

4.如果已设置RXPKTRDY,则软件应从端点0 FIFO读取数据,然后清除RXPKTRDY。

5.如果期望进一步的数据,软件应重复步骤1-4。当所有数据都已成功接收时,CPU应进入控制事务的OUT状态阶段。

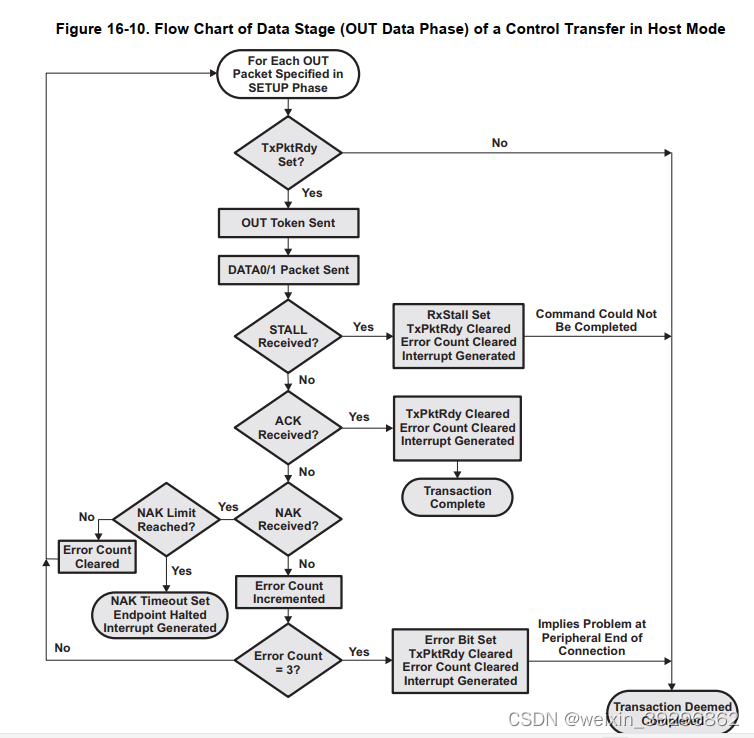

16.3.8.2.1.3控制事务的数据阶段(OUT数据阶段):主机模式

对于控制事务的OUT数据阶段(图16-10),驱动USB主机设备的软件

需要:

1.将要发送的数据加载到端点0 FIFO中。

2.设置HOST_CSR0的TXPKTRDY位(位1)。然后,控制器继续从FIFO向被寻址设备的端点0发送数据所允许的OUT令牌,必要时重试。

3.在发送数据的尝试结束时,控制器将生成Endpoint 0中断。然后,软件应读取HOST_CSR0,以确定RXSTALL位(位2)、ERROR位(位4)或NAK_TIMEOUT位(位7)是否已设置。

如果设置了RXSTALL位,则表示目标已发出STALL响应。

如果设置了ERROR位,则表示控制器已尝试发送OUT令牌和以下数据包三次,但没有得到任何响应。如果设置了NAK_TIMEOUT,则意味着控制器已接收到对每次发送OUT令牌的尝试的NAK响应,时间长于在HOST_NAMEKLIMIT0寄存器中设置的时间。然后可以指示控制器通过清除NAK_TIMEOUT位来继续尝试该事务(直到它再次超时),或者通过在清除NAK_ TIMEOUT位之前刷新FIFO来中止该事务。

如果没有设置RXSTALL、ERROR或NAKLIMIT,则OUT数据已被正确确认。

4.如果需要发送更多数据,软件应重复步骤1-3。

成功发送所有数据后,软件应进入控制事务的IN状态阶段。

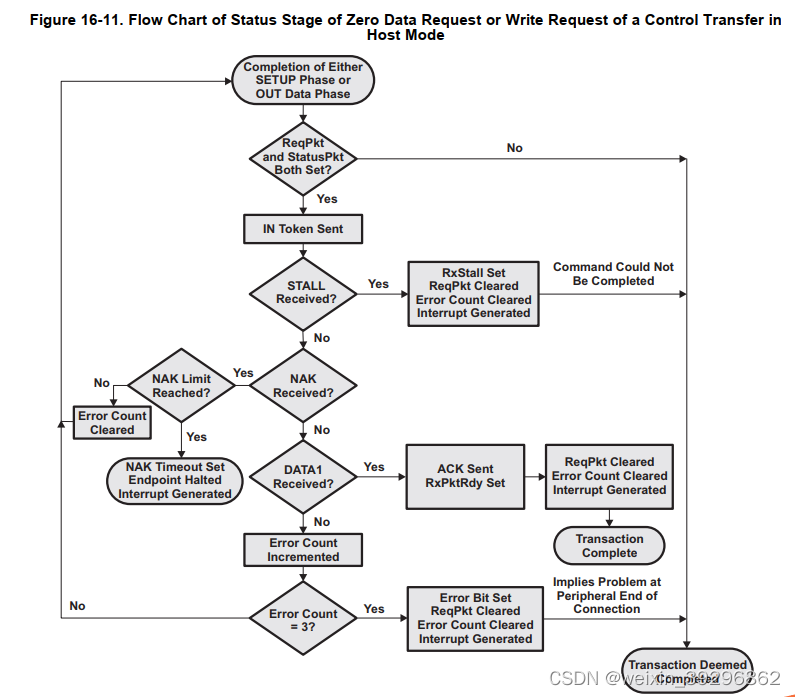

16.3.8.2.1.4控制事务的状态阶段(OUT数据阶段或设置阶段的状态):主机模式

对于零数据请求或控制传输的写入请求,存在控制传输的IN状态阶段。如果不存在控制传输的数据阶段,则IN状态阶段在Setup阶段之后,或者控制传输数据阶段的OUT数据阶段。

对于控制事务的IN状态阶段(图16-11),驱动USB主机设备的软件需要:

1.设置HOST_CSR0的STATUSPKT和REQPKT位(分别为位6和位5)。

2.等待控制器发送IN令牌并从USB外围设备接收响应。

3.当控制器产生端点0中断时,读取HOST_CSR0以确定RXSTALL位(位2)、ERROR位(位4)、NAK_TIMEOUT位(位7)或RXPKTRDY位(位0)是否已被设置。

如果设置了RXSTALL位,则表示目标无法完成命令,因此已发出STALL响应。

如果设置了ERROR位,则表示控制器已尝试发送所需的IN令牌三次,但没有得到任何响应。

如果设置了NAK_TIMEOUT位,则意味着控制器已经接收到对每次发送IN令牌的尝试的NAK响应,持续时间长于在HOST_NAMEKLIMIT0寄存器中设置的时间。然后,可以通过清除

或在清除NAK_TIMEOUT位之前通过清除REQPKT位和STATUSPKT位来中止事务。

4.CPU应清除HOST_CSR0的STATUSPKT位以及RxPktRdy(即,在与之相同的写入操作中)(如果已设置)。

16.3.8.2.1.5控制事务读取请求的状态阶段:主机模式

OUT状态对于读请求或主机控制器接收数据的控制传输,存在控制传输的阶段。OUT状态阶段在控制传输的IN数据阶段之后。

对于控制事务的OUT状态阶段(图16-12),驱动主机设备的CPU需要:

1.设置HOST_CSR0的STATUSPKT和TXPKTRDY位(分别为位6和位1)。

注意:这些位需要一起设置

2.等待,同时控制器发送OUT令牌和零长度DATA1分组。

3.在发送数据的尝试结束时,控制器将生成Endpoint 0中断。然后,软件应读取HOST_CSR0,以确定是否设置了RXSTALL位(位2)、ERROR位(位4)或NAK_TIMEOUT位(位7)。

如果设置了RXSTALL位,则表示目标无法完成命令,因此已发出STALL响应。

如果设置了ERROR位,则表示控制器已尝试发送STATUS数据包和以下数据包三次,但没有得到任何响应。

如果设置了NAK_TIMEOUT位,则意味着控制器已经接收到对每次发送IN令牌的尝试的NAK响应,持续时间长于在HOST_NAMEKLIMIT0寄存器中设置的时间。然后,可以通过清除来指示控制器继续尝试此事务(直到它再次超时)TIMEOUT位或通过在清除NAK_ TIMEOUT位之前刷新FIFO来中止事务。

4.如果没有设置RXSTALL、ERROR或NAK_TIMEOUT位,则STATUS Phase已被正确确认。

16.3.8.2.2批量传输:主机模式

大容量事务由端点0以外的端点处理。它用于处理非周期性、大突发通信,通常用于使用任何可用带宽的传输,也可以延迟到带宽可用为止。

16.3.8.2.2.1批量输入事务:主机模式

批量输入事务可用于将非周期性数据从外部USB外围设备传输到主机

以下可选功能可用于在主机模式下使用的Rx端点,以接收数据:

•双数据包缓冲:启用时,从主机接收数据包时,最多可将两个数据包存储在FIFO中。这允许在读取另一个分组的同时可以接收一个分组。通过设置RXFIFOSZ寄存器的DPB位(第4位)启用双数据包缓冲。

•DMA:如果为端点启用DMA,则每当端点的FIFO中有数据包时,都会生成DMA请求。此功能可用于允许DMA控制器在无需处理器干预的情况下从FIFO卸载数据包。

启用DMA时,将不会为完成数据包接收而生成端点中断。只有在出现错误的情况下才会生成端点中断。有关更多信息,请参阅CPPI DMA部分

16.3.8.2.2.1.1批量输入设置:主机模式

在主机模式下启动任何批量输入事务之前:

•要使用的端点的HOST_RXTYPE寄存器需要编程为:

–speed位字段(第7位和第6位)中的工作速度。

–在批量传输的PROT字段中设置10(二进制值)。

–RENDPN字段中目标设备的端点编号。这是目标设备在枚举期间返回的Rx端点描述符中包含的端点编号。

•控制器端点的RXMAXP寄存器必须使用传输的最大数据包大小(以字节为单位)写入。此值应与目标终结点的标准终结点描述符的wMaxPacketSize字段相同。

•HOST_RXINTERVAL寄存器需要写入NAK限制所需的值(2-215帧/微帧),或者如果不需要NAK超时功能,则设置为零。

•应设置INTRRXE寄存器中的相关中断启用位(如果此端点需要中断)。

注意:无论是从PDR级别还是核心级别处理中断,都需要在核心级别启用中断。请参阅核心中断寄存器、CTRLR寄存器以及中断处理部分的详细信息

•AUTOREQ位字段应仅在使用CPU模式为传输提供服务时使用,并且在使用DMA模式时必须清除。对于DMA模式,存在专用寄存器USB0/1 Req寄存器,并且应清除HOST_RXCSR[AUTOREQ]。

启用DMA时,HOST_RXCSR寄存器的以下位应设置为:

–清除AUTOCLEAR。

–如果此端点需要DMA请求,则将DMAEN(第13位)设置为1。

–将DSINYET(第12位)清除为0,以允许正常的PING流量控制。这将只影响高速事务。

–将DMAMODE(位11)清除为0。

注意:如果启用DMA,则可以设置USB0/1 Auto Req寄存器,以便在接收数据后自动生成IN令牌。将位字段RXn_AUTOREQ(其中n是端点编号)设置为二进制值01或11。

当首次配置端点时,应通过使用HOST_RXCSR的DATATOGWREN和DATATOG位(位10和位9)切换当前设置或通过设置HOST_RXCSRCLRDATATOG位(位7)将端点数据切换清除为0。这将确保数据切换(由控制器自动处理)在正确的状态下启动。此外,如果FIFO中有任何数据包(由正在设置的RXPKTRDY位(HOST_RXCSR的位0)指示),则应通过设置HOST_RXCSRFLUSHFFIFO位(位4)来刷新它们。

注:如果启用了双缓冲,则可能需要连续两次设置此位。

16.3.8.2.2.1.2批量输入操作:主机模式

当USB外围设备需要批量数据时,软件应在相应的HOST_RXCSR寄存器中设置REQPKT位(第5位)。然后,控制器将向所选的外围端点发送IN令牌,并等待返回数据。

如果数据被正确接收,则设置HOST_RXCSR的RXPKTRDY位(位0)。如果USB外围设备以STALL响应,则设置RXSTALL位(HOST_RXCSR的第6位)。如果接收到NAK,则控制器再次尝试并继续尝试,直到事务成功或到达HOST_RXINTERVAL寄存器中设置的POLINTVL_ NAKLIMIT。如果根本没有收到响应,则在控制器通过设置HOST_RXCSR的error位(位2)报告错误之前再进行两次尝试。

然后,控制器产生适当的端点中断,于是软件应该读取相应的HOST_RXCSR寄存器,以确定是否设置了RXPKTRDY、RXSTALL、ERROR或DATAERR_NAMEKTIMEOUT位并相应地采取行动。如果设置了DATAERR_NAMEKTIMEOUT位,则可以通过清除DATAERR_NAMEKTIMEOUT位,或通过在清除DATAERR_NAKTIMEOUT位之前清除REQPKT位来中止事务。

接收到的数据包不应超过RXMAXP寄存器中指定的大小(因为这应该是发送到主机的端点描述符的wMaxPacketSize字段中设置的值)。

在一般情况下,应用软件(如果CPU正在为端点提供服务)将需要单独从FIFO读取每个数据包。如果正在传输大块数据,则调用通过使用DMA可以避免卸载每个数据包的中断服务例程。

注:使用DMA时,请参阅第16.3.9节,通信端口编程接口(CPPI)4.1

DMA,用于正确配置核心寄存器HOST_RXCSR。

16.3.8.2.2.1.3批量输入错误处理:主机模式

如果目标想要关闭Bulk IN管道,它将向IN令牌发送STALL响应。这将导致HOST_RXCSR的RXSTALL位(位6)被设置。

16.3.8.2.2.2批量输出事务:主机模式

Bulk OUT事务可以用于将非周期性数据从主机传输到USB外围设备。

以下可选功能可用于在主机模式下用于传输此数据的Tx端点:

•双数据包缓冲:启用时,最多可将两个数据包存储在FIFO中,等待传输到外围设备。通过设置TXFIFOSZ寄存器的DPB位(第4位)启用双数据包缓冲。

•DMA:如果为端点启用DMA,则只要端点能够接受其FIFO中的另一个数据包,就会生成DMA请求。此功能可用于允许DMA控制器加载

数据包进入FIFO而无需处理器干预。有关使用DMA的更多信息,请参阅讨论CPPI DMA的部分。

当DMA被启用并且HOST_TXCSR寄存器中的DMAMODE位被设置时,将不会生成用于完成数据包接收的端点中断。只有在出现错误的情况下才会产生端点中断。

16.3.8.2.2.2.1批量输出设置:主机模式

在启动任何批量输出交易之前:

•需要在TXFUNCADDR寄存器中为所选控制器端点设置目标功能地址。(TXFUNCADDR寄存器可用于从EP0到EP15的所有端点。)

•要使用的端点的HOST_TXTYPE寄存器需要编程为:

–speed位字段(第7位和第6位)中的工作速度。

–将PROT字段设置为10b以进行批量传输。

–在TENDPN字段中输入目标设备的端点编号。这是端点编号包含在目标设备在枚举期间返回的OUT(Tx)端点描述符中。

•控制器端点的TXMAXP寄存器必须以传输的最大数据包大小(字节)写入。此值应与目标终结点的标准终结点描述符的wMaxPacketSize字段相同。

•HOST_TXINTERVAL寄存器需要写入NAK限制所需的值(2-215帧/微帧),或者如果不需要NAK超时功能,则设置为零。

•应设置INTRTXE寄存器中的相关中断启用位(如果此端点需要中断)。

•HOST_TXCSR寄存器的以下位应设置为:

–将MODE(模式)位(位13)设置为1,以确保启用FIFO(仅当FIFO与Rx端点共享时才需要)。

–将FRCDATATOG位(第11位)清除为0,以允许正常的数据切换操作。

–清除/设置AUTOSET位(位15)。此位的设置取决于用户/应用程序的需求

在使用CPU服务事务时自动设置TXPKTRDY位。

注意:如果需要使用DMA代替CPU,下表显示主机模式下核心寄存器HOST_TXCSR寄存器的设置。有关CPPI DMA寄存器设置,请参阅本文档中关于CPPI DMA的部分。

当首次配置端点时,应通过使用HOST_TXCSR的DATATOGWREN位和DATATOG位(位9和位8)切换当前设置或通过设置HOST_TXCSRCLRDATATOG位(位6)将端点数据切换清除为0。这将确保数据切换(由控制器自动处理)在正确的状态下启动。此外,如果FIFO中有任何数据包(由被设置的HOST_TXCSR寄存器的FIFONOTEMPTY位(位1)指示),它们应该通过设置FLUSHFFIFO位(HOST_TXCSR3)来刷新。

注:如果启用了双缓冲,则可能需要连续两次设置此位。

16.3.8.2.2.2.2大容量输出操作:主机模式

当需要将批量数据发送到USB外围设备时,软件应将数据的第一个数据包写入FIFO(如果是双缓冲的,则写入两个数据包),并在相应的HOST_TXCSR寄存器中设置TXPKTRDY位(位0)。然后,控制器将向选定的外围端点发送OUT令牌,然后从FIFO发送第一个数据包。

如果外围设备正确接收到数据,则应接收到ACK,于是控制器将清除HOST_TXCSR的TXPKTRDY位(位0)。如果USB外围设备以STALL响应,则设置HOST_TXCSR的RXSTALL位(第5位)。如果收到NAK,控制器会再次尝试并继续尝试,直到事务成功或达到HOST_TXINTERVAL中设置的NAK限制

到达寄存器。如果根本没有收到响应,则在控制器通过设置HOST_TXCSR中的error位(第2位)报告错误之前再进行两次尝试。

然后,控制器产生适当的端点中断,于是软件应该读取相应的HOST_TXCSR寄存器,以确定RXSTALL(位5)、ERROR(位2)或NAK_TIMEOUT(位7)位是否被设置并相应地动作。如果设置了NAK_TIMEOUT位,则可以指示控制器通过清除NAK_TIMEOUT位来继续尝试该事务(直到它再次超时),或者通过在清除NAK_IMEOUT位之前刷新FIFO来中止该事务。

如果正在传输大块数据,那么可以通过使用DMA来避免调用中断服务例程来加载每个数据包的开销。

16.3.8.2.2.2.3批量输出错误处理:主机模式

如果目标想要关闭Bulk OUT管道,它将发送一个STALL响应。这通过设置HOST_TXCSR寄存器的RXSTALL位(位5)来指示。

16.3.8.2.3中断传输:主机模式

当控制器作为主机运行时,与USB外围设备上的中断端点的交互处理方式与等效的批量事务处理方式(如前所述章节)。

就操作步骤而言,主要区别在于需要设置HOST_RXTYPE和HOST_TXTYPE的PROT字段(位5-4)(二进制值)来表示中断事务。还需要在HOST_RXINTERVAL和HOST_TXINTERVAL寄存器。

16.3.8.2.4等时传输:主机模式

使用等时数据时使用等时传输。等时传输在主机和设备之间提供周期性、连续的通信。

Isochronous IN事务用于将周期性数据从USB外围设备传输到主机

16.3.8.2.4.1同步IN事务:主机模式

以下可选功能可用于在主机模式下用于接收此数据的Rx端点:

•双数据包缓冲:启用时,从主机接收数据包时,最多可将两个数据包存储在FIFO中。这允许在读取另一个分组的同时可以接收一个分组。通过设置RXFIFOSZ寄存器的DPB位(第4位)启用双数据包缓冲。

•自动请求:当启用自动请求功能时,当清除RXPKTRDY位时,将自动设置HOST_RXCSR的REQPKT位(第5位)。这仅适用于使用CPU为端点提供服务的情况。使用DMA时,需要将此位字段清除为零。CPPI DMA有自己的配置寄存器,用于呈现类似的任务,USB0/1 Auto Req寄存器,需要使用该寄存器才能具有类似的效果。有关更多信息,请参阅第16.3.9节,通信端口编程接口(CPPI)4.1 DMA。

•DMA:如果为端点启用了DMA,则只要端点有FIFO中的数据包。此功能可用于允许DMA控制器从

先进先出,无需处理器干预。然而,这个特性对于等时性并不是特别有用

•启用DMA时,不会为完成数据包接收而生成端点中断。

只有在出现错误的情况下才会产生端点中断。

16.3.8.2.4.1.1同步IN传输设置:主机

在主机模式下启动同步IN事务之前:

•需要在RXFUNCADDR寄存器中为所选控制器端点设置目标功能地址(RXFUNCADD寄存器可用于从EP0到EP4的所有端点)。

•要使用的端点的HOST_RXTYPE寄存器需要编程为:

–speed位字段(第7位和第6位)中的工作速度。

–在PROT字段中设置01(二进制值)以进行等时传输。

–RENDPN字段中目标设备的端点编号。这是包含在

在枚举期间由目标设备返回的Rx端点描述符。

•控制器端点的RXMAXP寄存器必须使用最大数据包大小(in

字节)进行传输。此值应与目标终结点的标准终结点描述符的wMaxPacketSize字段相同。

•HOST_RXINTERVAL寄存器需要以所需的事务间隔写入(通常每帧/微帧一个事务)。

•应设置INTRRXE寄存器中的相关中断启用位(如果此端点需要中断)。

•HOST_RXCSR寄存器的以下位应设置为:

–清除AUTOCLEAR

–如果此端点需要DMA请求,则将DMAEN位(位13)设置为1。

–将DISNYET it(第12位)清除为0,以允许正常的PING流量控制。这只会影响高

加快交易速度。

–将DMAMODE位(第11位)清除为0。

•如果启用DMA,则可以设置AUTOREQ寄存器,以便在接收后自动生成IN令牌

数据。将位字段RXn_AUTOREQ(其中n是端点编号)设置为二进制值01或11。

有关使用CPPI DMA的详细信息,请参阅本文档中的相关章节。

16.3.8.2.4.1.2同步IN操作:主机模式

操作从HOST_RXCSR的软件设置REQPKT位(第5位)开始。这导致控制器向目标发送一个IN令牌。

当接收到数据包时,生成一个中断,软件可以使用该中断从FIFO卸载数据包,并以与Bulk Rx端点相同的方式清除HOST_RXCSR寄存器中的RXPKTRDY位(位0)。由于中断几乎可以在一帧(/微帧)内的任何时间发生,FIFO卸载请求的定时可能是不规则的。如果端点的数据接收器要连接到一些外部硬件,那么最好在卸载FIFO之前等待每个帧结束,从而最大限度地减少对额外缓冲的需求。这可以通过使用来自控制器的SOF_PULSE信号来触发数据包的卸载来实现。SOF_PULSE每帧(/微帧)生成一次。中断仍然可以用于清除HOST_RXCSR中的RXPKTRDY位。

16.3.8.2.4.1.3异时IN错误处理:主机模式

如果在接收分组期间发生CRC或比特填充错误,则分组仍将被存储在FIFO中,但是HOST_RXCSR的DATAERR_NAMEKTIMEOUT比特(比特3)被设置为指示数据可能被破坏。

注意:在任何微帧中发送的USB数据包的数量将取决于要发送的数据量

并且通过用于各个分组的PID来指示。如果指示的

到微帧结束时尚未接收到数据包,HOST_RXCSR中的INCOMPRX位

寄存器将被设置为指示FIFO中的数据不完整。同样,如果接收到错误数据类型的数据包,则PID错误位为HOST_RXCSR寄存器将被设置。然而,在每种情况下,仍将产生中断,以允许从FIFO读取已接收的数据。

16.3.9通信端口编程接口(CPPI)4.1 DMA

CPPI DMA模块支持USB数据包的传输和接收。CPPI DMA的设计有助于将符合CPPI的数据包分割和重组到与每个网络端口的特定要求本地兼容的较小数据块。为DMA内的所有端点(不包括端点0)提供多个Tx和Rx信道,从而允许并行(但实际上不是同时)有效地执行多个分段或重组操作。DMA控制器维护每个端口/信道的状态信息,这允许分组分割和重组操作在信道之间时分复用,以便共享底层DMA硬件。DMA调度器用于控制这种多路复用发生的顺序和速率。

CPPI(4.1版)DMA控制器子模块是一个常见的15端口DMA控制器。它支持15个Tx和15个Rx通道,每个端口都连接到控制器中的相关端点。端口1映射到端点1,端口2映射到端点2,依此类推,其中端口15映射到端点15;端点0不能利用DMA,并且固件负责通过CPU加载或卸载端点0的FIFO。

16.3.9.1 CPPI术语

Host —主机是一种智能系统资源,用于配置和管理每个通信控制模块。主机负责分配内存、初始化所有数据结构以及响应端口中断。

Main Memory —由CPU管理的数据存储区域。CPPI DMA(CDMA)从主存储器读取CPPI数据包并将其写入主存储器。此内存可以存在于设备内部或外部

Queue Manager (QM) —QM负责加速各种数据包的管理队列和空闲描述符/缓冲区队列。当队列为空或满时,它向CDMA调度器提供状态指示。

CPPI DMA(CDMA)-CDMA负责在CPPI FIFO和主存储器之间传输数据。它从QM(接收-提交队列)获取空闲缓冲描述符,用于存储接收到的数据,将接收到的分组指针发布到接收完成队列,发送存储在发送-提交队列(发送队列)上的分组,并将完成的发送分组发布到发送完成队列。

CDMA调度器(CDMAS)-CDMAS负责调度CDMA发送和接收操作。它使用来自QM和CDMA的队列指示符来确定要调度的操作类型。

CPPI FIFO — CPPI FIFO提供FIFO接口(用于15个发送和15个接收端点中的每一个)。

Transfer DMA (XDMA)-----XDMA从Mentor USB 2.0 Core接收DMA请求,并向CPPI FIFO启动DMA。

Endpoint FIFOs —端点FIFO是Mentor USB 2.0 Core用于数据包传输或接收的USB数据包存储元件。XDMA在用于发送操作的CPPI FIFO和端点FIFO之间以及用于接收操作的端点FIFO和CPPI FIFO之间传输数据。

端口-端口是一个通信模块(外围硬件),包含单个发送/接收接口或一组接口的直接内存访问控制逻辑。每个端口可以具有使用同质或异构协议传输数据的多个通信信道。端口通常被细分为相互独立的发送对和接收对。每个端点(不包括端点0)都有自己的专用端口。

通道-通道是指跨端口传输的信息(流)的细分。每个通道都有相关的状态信息。通道用于根据所使用的协议、调度要求(例如:CBR、VBR、ABR)或并发要求(即避免阻塞)来隔离信息流。每个USB模块的所有十五个端口都有专用的单通道,即通道0,用于在USB应用程序中使用。

数据缓冲区-数据缓冲区是一种单一的数据结构,包含向端口发送或从端口接收的有效载荷信息。数据缓冲区为字节对齐的连续内存块,用于存储数据包有效载荷数据。数据缓冲器可以保存数据包的任何部分,并且可以链接在一起(通过描述符)与其他缓冲器进行比较以形成分组。数据缓冲器可以被分配到32位存储器空间内的任何位置。数据包描述符的Buffer Length字段指示缓冲区中有效数据字节的数量。在每个缓冲器中可能存在从1到4M-1的有效数据字节。

16.3.9.2数据结构

两种数据结构主要用于识别分组描述符和缓冲区描述符所使用的数据缓冲区。存在第三个描述符,即撕裂描述符。此描述符的用途是一个通道停止和拆除事件。这些描述符布局中的每一个以及位字段如下所示。

16.3.9.2.1主机数据包描述符/数据包描述符(SOP描述符)

描述符被设计用于当类似USB的应用程序需要支持真实的、无限制的碎片计数分散/收集类型的操作时使用。分组描述符是多个描述符设置中的第一个描述符,或者是单个描述符设置中唯一的描述符。数据包描述符包含以下信息:

•将描述符标识为数据包描述符的指示符(始终为10h

•来源和目的地标签(保留)

•数据包类型

•数据包长度

•特定于协议的区域大小

•特定于协议的控制/状态

•指向SOP数据缓冲区中第一个有效字节的指针

•SOP数据缓冲区的长度

•指向中的下一个缓冲区描述符的指针

分组描述符的大小可以根据其定义字段的设计而变化,从32字节到104字节。在该范围内,分组描述符总是包含32字节的所需信息,并且还可以包含8字节的软件特定标记信息和高达64字节(以4字节增量表示)的协议特定信息。有多少特定于协议的信息(以及因此分配的描述符大小)取决于应用程序。端口将仅使用前32个字节。

从通用USB使用的角度来看,32字节描述符大小是后缀,正常USB使用时预计会使用此大小。

数据包描述符布局如图16-13所示,并在表16-9至表16-16中进行了描述。

16.3.9.3 Queue Manager

队列管理器(QM)是一个硬件模块,负责加速队列的管理,即队列保持在队列管理器模块内。通过将32位描述符地址写入队列管理器模块中的特定内存映射位置,将数据包添加到队列中。数据包通过读取特定队列的相同位置而被取消排队。单个队列管理器存在于设备内,并处理USB子系统内所有可用的156个队列。通过将描述符指针写入队列N寄存器D,描述符被排队到逻辑队列(推送)上。当写入队列N注册表D时,这启动队列管理器,使其将描述符添加到队列尾部。

QM跟踪在队列中推送的描述符的顺序或描述符的链接状态。为了实现这种链接状态,QM将首先将32位描述符指针解析为16位索引,该索引用于链接队列指针。

一旦执行了地址到索引的计算,即确定了物理索引信息,QM将通过将链接信息写入队列管理器外部的链接RAM,将该描述符链接到为该逻辑队列维护的描述符链上。关于RAM链接的更多讨论将在后面的章节中进行。QM还将适当地更新队列尾部指针。由于队列管理器中的逻辑队列是使用链表来维护的,因此队列不会变满,并且在对数据包描述符进行排队之前不需要检查是否已满。

16.3.9.3.1队列类型

CPPI 4.1 DMA中存在几种类型的队列(总共156个队列)。无论队列的类型如何,队列都用于在主机和/或系统中的任何端口之间传递指向数据包或缓冲区描述符的指针。所有队列都维护在单个队列管理器模块中。

存在以下类型的队列:

•自由描述符队列(未分配给特定端点,但分配给特定的端点类型;接收端点–可用作接收-提交队列)

•传输提交队列

•传输完成(返回)队列

•接收完成(返回)队列

•拆除队列

存在专用队列,其中为使用单个端点分配了一个或多个队列,而存在不需要为端点分配特定队列的非专用队列(但仅适用于接收端点)。不允许传输终结点使用空闲描述符队列。

存在用于每个特定端点使用的专用队列,并且存在可由任何/所有接收端点使用的非专用队列。为每个端点/端口保留三个队列用于传输操作,其中三个队列中的两个是传输提交队列,而其余队列用作完成/返回队列。对于接收操作,唯一的专用队列是完成/返回队列;

为每个接收端点分配/保留一个队列。存在32个没有专用端点队列分配的空闲描述符队列,并且这些队列用于作为接收-提交队列为任何接收端点提供服务。

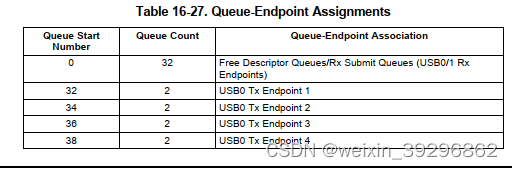

表16-27显示了队列端点分配。

16.3.9.3.2自由描述符队列(接收-提交队列)

接收端点/通道使用队列(称为空闲描述符队列或接收提交队列)将完成的接收数据包转发到主机。空闲描述符队列上的条目具有预先附加的空缓冲区,其大小和位置在描述符的原始缓冲区信息字段中进行了描述。在向可用的空闲描述符队列之一添加(提交)描述符之前,主机需要分配描述符和缓冲区并预链接它们。前32个队列(队列0到队列31)被保留用于所有30个USB0/1(每个USB模块的端点1到15)接收端点/通道以处理到设备的传入分组。

16.3.9.3.3传输-提交队列

传输端口使用数据包队列(称为传输提交队列)来存储等待传输的数据包。每个传输端点都有专用队列(每个端口2个队列),这些队列专门留给单个端点使用。为每个端口/信道分配多个队列,以便为需要QoS的应用程序提供服务质量(QoS)。前30个队列,队列32到队列61,分配给USB0传输端点1到15,每个端点有两个队列。队列62到队列91,分配给传输USB1端点1到15。

16.3.9.3.4传输完成(返回)队列

传输端口使用分组队列,简称为“传输完成队列,用于在数据包传输后将数据包描述符返回到主机。单个队列保留给单个传输端点使用。应用程序s/w需要确保在数据包发送完成后,根据使用的端点编号,使用正确的队列集来返回描述符。对于USB0传输端点1至15,队列93–107分别被保留和分配用作完成队列。类似地,对于USB1传输端点1至15,队列125至139分别用作完成队列。

传输完成队列还用于在执行传输通道拆卸操作时返回数据包描述符。

16.3.9.3.5接收完成(返回)队列

接收端口使用数据包队列,称为接收完成队列,在接收到数据包后将数据包描述符返回到端口。单个队列被保留以供单个接收端点使用。应用程序s/w需要确保在完成基于所使用的端点号的分组接收之后,使用正确的队列集来返回描述符。对于USB0接收端点1保留/分配多达15个队列122-136,分别用作接收完成队列。

类似地,对于USB1接收端点1至15,队列137至151分别用作完成队列。

接收事务不需要接收通道拆卸,并且没有可用的通道拆卸信息或资源

16.3.9.3.6将队列数据包从一个队列转移到另一个队列

主机可以通过将源队列号和目标队列号写入队列转移寄存器,将一个队列的全部内容移动到另一个队列。当转移数据包时描述符被推送到目的地队列的尾部。

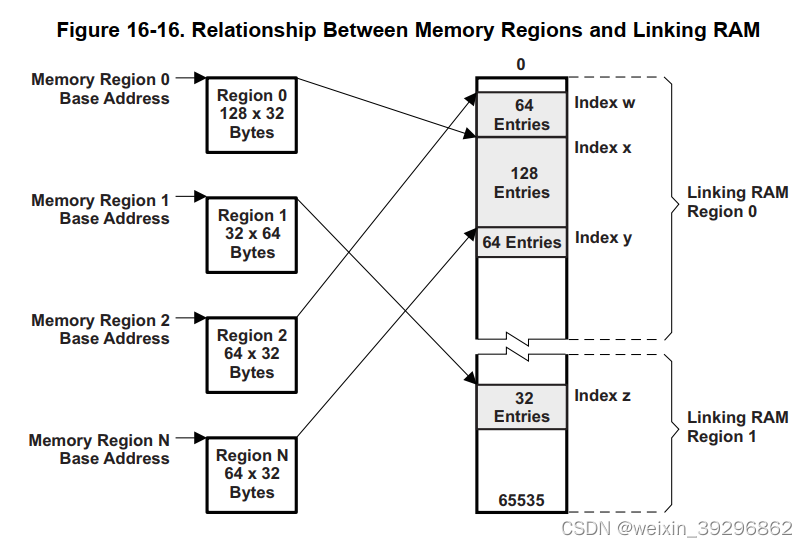

16.3.9.4内存区域和链接RAM

除了为原始数据分配缓冲区和为描述符分配内存外,主机还负责分配额外的内存以独占使用CPPI DMA队列管理器,用作暂存垫锤。队列管理器使用此内存来管理在提交队列。换句话说,该存储器不需要由用户软件和固件管理责任仅在于为队列管理器的使用分配/保留一块内存。这个分配的内存可以是连续的单个内存块,也可以是不连续。这两个内存块被称为链接RAM区域,不应与用于存储描述符的存储器区域混淆。也就是说,区域一词的使用应在其使用的上下文中使用。

为了完成提交描述符的链接,队列管理器将首先将32位描述符指针解析为16位索引,该索引用于链接和队列指针目的。一旦确定了物理索引信息,队列管理器将通过将链接信息写入队列管理器外部的链接RAM,将该描述符链接到为该逻辑队列维护的描述符链上。队列管理器还将适当地更新队列尾部指针。由于队列管理器中的逻辑队列是使用链表来维护的,因此队列不会变满,并且在对数据包描述符进行排队之前不需要检查是否已满。

要分配的链接RAM区域的实际物理大小取决于在所有存储器区域内定义的描述符的总数。需要为所有16个存储器区域内定义的每个描述符分配至少四个字节的存储器。

队列管理器能够管理多达16个内存区域。这些存储器区域用于存储大小可变的描述符。队列管理器可以管理的描述符总数不应超过64K。每个存储器区域具有一个可配置大小的描述符,也就是说,具有不同大小的描述符不能容纳在单个存储器区域内。这些64K描述符在队列管理器中由16位数量索引内部引用。

关于链接RAM区域和分配的大小的信息通过专用于此目的的三个寄存器传送到CPPI DMA。三个寄存器中的两个用于存储

链接RAM区域的32位对齐起始地址。剩下的一个寄存器用于存储第一链接RAM的大小。此处存储的链接RAM大小值是指由该区域内的队列管理器管理,而不是缓冲区的物理大小,即描述符数量的四倍。

注意,如果第一区域的链接RAM的大小足够大以容纳所定义的所有描述符,则应用程序不需要同时使用两个链接RAM区域。不存在用于链接RAM区域2的链接RAM大小寄存器。当使用时,第二链接RAM的大小是从定义的描述符的总数减去由第一链接RAM管理的描述符的数量来间接计算的

图16-16显示了几个内存区域和链接RAM之间的关系。

16.3.9.5零长度数据包

一种特殊情况是使用符合CPPI 4.1的DMA控制器处理空数据包。在接收到零长度USB数据包时,XFER DMA将向DMA控制器发送一个数据块,该数据块的字节计数为零,并且设置了INFO Word 2的零字节数据包位。DMA控制器随后将在不传输数据的情况下执行分组的正常分组结束终止。

如果接收到零长度的USB数据包,则XDMA将向CDMA发送字节计数为0的数据块和该比特集。CDMA随后将在不传输数据的情况下执行分组的正常EOP终止。对于传输,如果数据包设置了此位,则XDMA将忽略CPPI数据包大小,并向USB控制器发送零长度数据包。

16.3.9.6 CPPI DMA调度器

CPPI DMA调度器负责控制CPPI DMA控制器中提供的不同Tx和Rx线程/传输之间的速率和顺序。调度器表RAM存在于调度器中。

DMA控制器维护每个信道的状态信息,这允许在信道之间时分复用分组分割和重组操作,以便共享底层DMA硬件。DMA调度器用于控制排序和速率这种多路复用

16.3.9.6.1 CPPI DMA调度器操作

一旦调度程序被启用,它将开始处理表中的条目。在适当的时候,调度器将把信用传递给DMA控制器以执行Tx或Rx操作。DMA控制器的操作如下:

1.启用DMA调度程序后,它以表索引设置为0开始。

2.调度器读取索引所指向的条目,并检查所讨论的信道当前是否处于可以接受DMA操作的状态。

(a) DMA通道必须启用AND

(b) 信道与之通信的CPPI FIFO在TX上有空闲空间(FIFO满信号未断言)或

Rx上的有效块(未断言FIFO空信号)

3.如果DMA信道能够处理信用以传送块,则DMA调度器将通过DMA调度接口发出该信用,DMA调度接口是DMA调度器和DMA控制器之间的点对点连接。

(a) DMA控制器可能没有准备好立即接受信用,并且被提供用于暂停调度器直到其可以接受信用的sched_ready信号。DMA控制器仅在处于IDLE状态时断言sched_ready信号。

(b) 一旦信用被接受(由同时断言的sched_req和sched_ready指示),调度器将把索引增加到下一个条目,并将在步骤2再次开始。

4.如果所讨论的信道当前不能处理信用,则调度器将把调度器表中的索引增加到下一个条目,并从步骤2开始。

5.请注意,当调度器试图将其索引增加到表大小寄存器中编程的值时,索引将重置为0。

16.3.9.6.1.1 CPPI DMA调度器初始化

在使用调度程序之前,需要主机初始化并启用块。此初始化执行如下:

1.主机初始化调度器中的内部存储器阵列内的条目。该阵列包含多达256个条目(每个表字n 4个条目,其中n=0-63),并且每个条目由DMA信道号和指示这是Tx还是Rx机会的位组成。这些条目表示将处理各种Tx和Rx信道的顺序和频率。256个条目的表大小允许以总DMA带宽的1/256的最大精度分配信道带宽。

给定信道的条目越多,该信道将被给定的带宽切片就越大。可以调整较大的表格以获得更高的精度。此数组只能由主机写入,不能读取。

2.如果应用程序不需要使用整个256个条目,固件可以初始化256个条目的部分,并通过写入调度器中的内部寄存器来指示所使用的条目的大小它设置了数组的实际大小(可以小于256个条目)。

3.主机写入一个内部寄存器位以启用调度器。不需要禁用计划程序即可更改计划程序数组内容。

16.3.9.6.1.2 CPPI DMA调度器编程示例

考虑在具有以下配置的系统上使用三个端点:EP1 Tx、EP2 Rx和EP2-Tx。考虑了两个假设:

情况1:假设您希望为每个启用的端点(EP1 Tx、EP2 Rx和EP2 Tx)提供服务

具有同等优先级。

调度器处理由编程的信用数量为端点提供服务的速率(条目)。调度程序最多有256个

它可以授予的信用,对于这个例子,用户可以将条目/信用的数量配置为具有一组3个条目的从3到256的任意位置。

然而,这种情况下的最佳和直接编程将仅编程前三个调度程序的条目通过调度程序表WORD[0]。由于这种情况下计划程序只使用在前三个条目中,通过用2编程DMA_SCHED_CTRL.LAST_ENTRY来进行通信

(即3-1)。启用端点编号和数据传输方向由对WORD[0]的前三个条目进行编程(ENTRY0_CHANNEL=1:ENTRY0_RXTX=0;ENTRY1_CHANNEL=2:ENTRY1_RXTX=1;ENTRY2_CHANNEL=2:ENTRY2_RXTX=0)。有了这个

在编程时,调度器将只以循环方式为前三个条目提供服务,并检查每个条目

用于一个接一个地传输的贷记端点,并为有数据要传输的端点提供服务。

情况2:启用端点EP1 Tx的服务速率是其他启用端点的两倍(EP2 Rx

以及EP2-Tx)。

必须授予EP1 Tx的条目/学分数量必须是其他条目/学分的两倍。

四个条目/学分将后缀以满足我们的要求,EP1 Tx有两个学分,EP2有一个学分-

Rx和一个用于EP2-Tx的信用。通过将四个条目中的任意两个分配给

EP1 Tx端点。对于这个例子,调度程序表WORD[0]就足够了,因为它可以处理

前4个条目。尽管有几种场景可以对这种情况下的服务顺序进行编程

场景将允许背靠背地服务EP1 Tx,然后是其他启用的端点。

用3(即4-1)编程DMA_SCHED_CTRL.LAST_ENTRY。程序WORD[0]

(entry_CHANNEL=1:entry_RXTX=0;entry_CHANNEL=1:ENTRY1_RXTX=0;

ENTRY2_CHANNEL=2:ENTRY2_RXTX=1;ENTRY3_CHANNEL=2:ENTRY3_RXTX=0)。

16.3.9.7 CPPI DMA状态寄存器

端口必须存储和维护每个发送和接收端口/通道的状态信息。状态信息被称为Tx DMA状态和Rx DMA状态。

16.3.9.7.1传输DMA状态寄存器

Tx-DMA状态是控制字段和协议专用端口暂存区空间的组合,用于操作数据结构和传输数据包。每个传输通道都有两个队列。每个队列都有一个头描述符指针和一个完成指针。有三十个Tx DMA状态寄存器;每个端口/通道一个。

以下信息存储在Tx DMA状态中:

•Tx队列头描述符指针

•Tx完成指针

•特定于协议的控制/状态(端口草稿)

16.3.9.7.2接收DMA状态寄存器

Rx-DMA状态是控制字段和协议专用端口暂存区空间的组合,用于操作数据结构以接收分组。每个接收通道只有一个队列。每个通道队列都有一个头描述符指针和一个完成指针。有三十个Rx DMA状态寄存器;每个端口/通道一个。

以下信息存储在Rx DMA状态中:

•Rx队列头描述符指针

•接收队列完成指针

16.3.9.8支持的CPPI DMA协议

CPPI 4.1 DMA支持四种不同类型的DMA传输;透明、RNDIS、通用

RNDIS和Linux CDC。以下部分将概述这些DMA传输类型的详细信息。

16.3.9.8.1透明DMA传输

透明模式DMA操作是默认的DMA模式,每当

DMA数据包被传输。在透明模式下,DMA数据包大小不能大于USB

端点的最大PktSize。这种传输类型非常适合小于

最大数据包大小。

16.3.9.8.1.1透明DMA传输设置

以下将为透明DMA传输类型配置所有30个端口/通道。

确保全局禁用RNDIS模式。这允许应用程序配置CPPI DMA

使用中的协议将根据端点需要进行配置。要禁用RNDIS操作,请清除

与USB模块对应的USB控制寄存器(默认设置),即CTRL0[RNDIS]=0,以及

CTRL1[RNDIS]=0。

为中的Endpoint字段配置USB0/1 Tx/Rx DMA模式寄存器(USB0/1 Tx(Rx)MODE0/1)

使用编程为透明模式,即TXMODE0/1[TXn_Mode]=00b和

RXMODE 0/1[RXn_MODE]=00b。

16.3.9.8.2 RNDIS DMA传输

RNDIS模式DMA用于大型传输(即,要传输的总数据大小大于USB

MaxPktSize,其中MzxPktSize是64字节的倍数),其需要多个USB数据包。这是

通过将较大的数据包分解为较小的数据包来实现,其中每个数据包大小都是USB

MaxPktSize,最后一个数据包除外,该数据包的大小小于USB MaxPktSize,包括零字节。这

意味着MaxPktSize的多个USB数据包将作为单个数据包一起接收和传输大的DMA传输,并且DMA中断仅在DMA的完全接收结束时生成转移该协议通过接收一个短的USB数据包(较小

大于USB规范2.0中提到的USB MaxPktSize)。如果DMA数据包大小是精确的倍数

对于USB MaxPktSize,DMA控制器在完全传输结束时等待零字节数据包表示转让完成。

注意:只有当USB MaxPktSize是64字节的整数倍时,才支持RNDIS模式DMA。

16.3.9.8.2.1 RNDIS DMA传输设置

如果所有使用中的端点都希望在RNDIS模式下操作,那么配置RNDIS DMA只是后缀

全局级RNDIS模式下的操作,应用程序可以忽略单个端点DMA模式

配置这是通过用“1”对CTRLR0/1[RNDIS]进行编程来实现的

但是,如果需要在端点级别配置DMA模式,则需要禁用全局级别的RNDIS,这是通过清除RNDIS位字段(CTRLR0/1[RNDIS]=0)来实现的,因为全局配置优先于端点配置。

要配置RNDIS DMA模式使用,请配置与USB模块端点对应的字段使用相应的USB0/1 TX(RX)模式寄存器,即TXMODE0/1[TXn_Mode]=01b,以及RXMODE 0/1[RXn_MODE]=01b

16.3.9.8.3通用RNDIS DMA传输

通用RNDIS DMA传输模式在几乎所有方面都与普通RNDIS模式相同,除了传输的最后一个数据包可以是短数据包或MaxPktSize的例外情况。当最后一个数据包大小等于MaxPktSize时,则没有额外的零字节数据包

在使用通用RNDIS传输时发送。通用RNDIS传输使用USB0/1通用RNDISEPn大小寄存器(每个端点都有一个寄存器),必须使用

在发布传输事务之前,USB模块(USB0或USB1)的传输的传输大小(以字节为单位)。如果传输大小是USB MaxPktSize的整数倍,则没有额外的零字节

当使用通用RNDIS传输时发送分组。然而,如果在编程大小计数之前发送了短数据包,则传输将以类似于RDIS传输的方式结束。例如,如果USB MaxPktSize(Tx/RxMaxP)被编程为值64,则该端点的通用RNDIS EP Size寄存器必须被编程为64的整数倍(例如,64、128、192、256等),因为它的行为与RNDIS传输不同。换句话说,当使用

通用RNDIS模式,DMA的任务是传输小于或等于USB0/1通用RNDISEPn大小寄存器中编程的大小值的数据传输大小。

这意味着通用RNDIS模式将以与RNDIS方式相同的方式执行数据传输,如果接收到大小小于USB MaxPktSize大小值的USB数据包,则关闭CPPI数据包。

否则,当达到Generic RNDIS EP Size寄存器中的值时,数据包将被关闭。

使用USB0/1 GENERIC RNDIS EPn Size寄存器,可以传输高达64K字节(65536字节)的数据包。这是为了允许主机软件对USB模块进行编程,以传输精确的数据

USB MaxPktSize(Tx/RxMaxP编程值)的倍数,而不必发送额外的短分组来终止。

注:与RNDIS模式一样,任何通用的USB最大数据包大小(Tx/RxMaxp编程值)

启用RNDIS模式的端点必须是64字节的倍数。对于最大数据包大小不是64字节倍数的端点,不应启用通用RNDIS加速。仅透明模式

应用于此类端点。

16.3.9.8.3.1通用RNDIS DMA传输设置

在全局级别禁用RNDIS的使用,这是通过清除RNDIS位字段(CTRLR0/1[RNDIS]=0)来实现的,因为全局配置优先于端点配置。

使用相应的USB0/1 TX(RX)模式寄存器配置与USB模块端点对应的字段,即TXMODE0/1[TXn_Mode]=11b和RXMODE0/1[RXn_Mode=11b。

16.3.9.8.4 Linux CDC DMA传输

Linux CDC DMA传输模式的操作方式与RNDIS数据包相同,除了最后一个数据与最大USB数据包大小匹配的情况外,需要在RNDIS模式下进行额外的零字节数据包传输,而Linux CDC的情况并非如此。如果传输的最后一个数据包是数据大小大于零且小于USB MaxPktSize的短数据包,则Linux CDC DMA传输类型的行为与RNDIS DMA传输类型相同。唯一的例外是当终止传输的短数据包长度为空数据包时。在这种情况下,它将传输一个大小为1字节、数据值为00h的数据包,而不是传输Null数据包。

在传输操作中,如果配置了端点或CDC Linux模式,则在从CPPI DMA接收到空分组时,XFER DMA将生成包含1字节数据的分组,其值为00h,

指示传输的结束。在接收操作期间,XFER DMA将把一个字节的零分组识别为数据传输的终止,并向CPPI DMA控制器发送具有EOP指示符集和字节计数为1的数据块。实现传输结束的CPPI DMA

终止将不会更新/增加主机分组描述符的分组大小计数。

16.3.9.8.4.1 Linux CDC DMA传输设置

在全局级别禁用RNDIS的使用,这是通过清除RNDIS位字段(CTRLR0/1[RNDIS]=0)来实现的,因为全局配置优先于端点配置。

使用相应的USB0/1 TX(RX)模式寄存器配置与USB模块端点对应的字段,即TXMODE0/1[TXn_Mode]=10b和RXMODE0/1[RXn_Mode]

16.3.9.9使用DMA的USB数据流

使用CPPI 4.1 DMA执行USB数据传输所需的必要步骤通过发送和接收两种情况的示例来表达。假设USB0已准备好执行大小为608字节的USB数据传输(见图16-17)。

使用三个描述符来描述要传输的608字节的数据。由于定义了每个数据缓冲区在具有256字节大小的单个描述符内,608字节的数据缓冲器将需要三个描述符

假设示例:

•CPPI数据缓冲区的长度为256字节。

•USB0模块将用于执行此传输。请注意,USB1使用所需的步骤类似。

•USB0端点1 Tx和Rx端点1大小经过编程,可处理512字节的最大USB数据包大小。

•单个传输长度为608字节。

•SOP偏移为0。

以上转换为以下多描述符设置:

传输案例

传输设置如下:

•一个数据包描述符,数据包长度(这不是数据缓冲区长度,这里使用的术语数据包是指传输长度,而不是USB数据包)字段为608字节,数据缓冲区大小为256字节,链接到第一个主机缓冲区描述符。

•具有第一个缓冲描述符的两个缓冲描述符(这是链接到数据包描述符的一个)

定义256字节的第二数据缓冲区大小,该第二数据缓冲器大小依次链接到下一个(第二)缓冲区描述符。

•第二个缓冲区fescriptor,其fata缓冲区大小为96字节(可以更大,数据包描述符包含数据包的大小),没有链接到其他描述符(NULL)。

接收案例

对于这个例子,由于每个数据缓冲区大小是256字节,我们将需要至少三个描述符来定义608字节的数据缓冲区尺寸。接收设置如下:

•两个缓冲描述符,数据缓冲区大小为256字节

•一个具有96字节(可以更大)数据缓冲区大小的缓冲区描述符

在本节的其余部分中,使用了以下命名法:

BD-缓冲区描述符或主机缓冲区描述符

DB-256字节的数据缓冲区大小

PBD-指向主机缓冲区描述符的指针

PD-主机数据包描述符

PPD-指向主机数据包描述符的指针

TXSQ-传输队列或传输提交队列(对于USB0 EP1,使用队列32或33,对于USB1 EP1

使用队列62或63)

TXCQ-传输完成队列或传输返回队列(对于USB0 Tx EP1,使用队列93,以及

对于USB1 Tx EP1使用队列125)

RXCQ-接收完成队列或接收返回队列(对于USB0 Rx EP1,使用队列109,对于

USB1 Rx EP1使用队列141)

RXSQ-接收空闲/缓冲描述符队列或接收提交队列。(对于USB0 Rx EP1队列0

并且对于USB1 Rx,应使用EP1队列16

3860

3860

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?