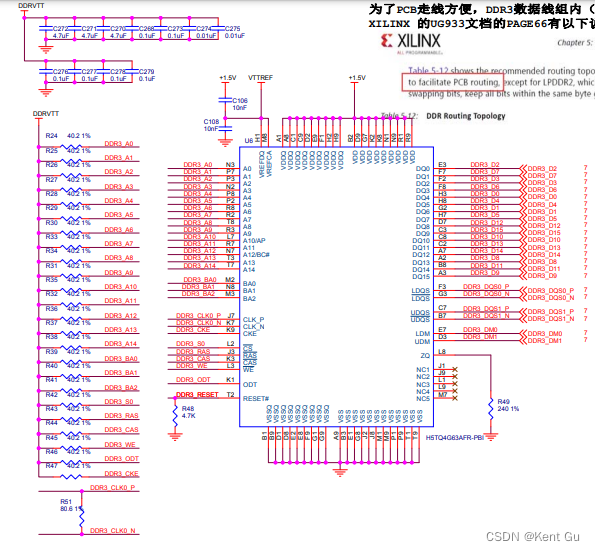

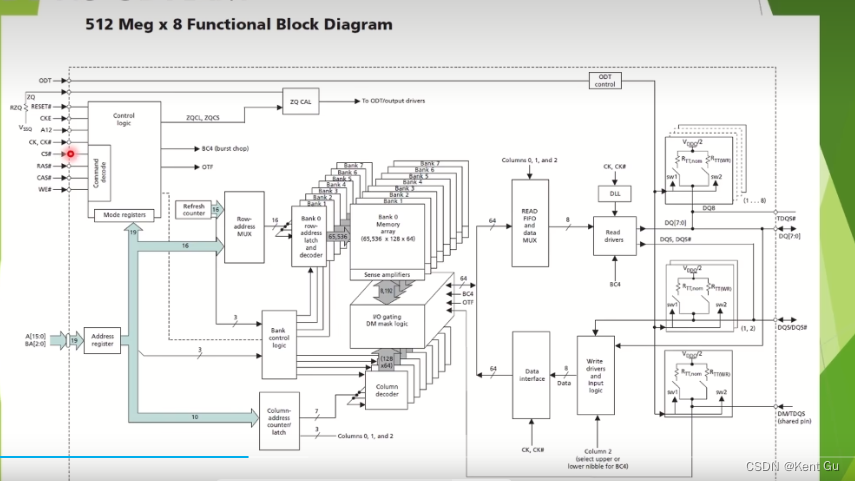

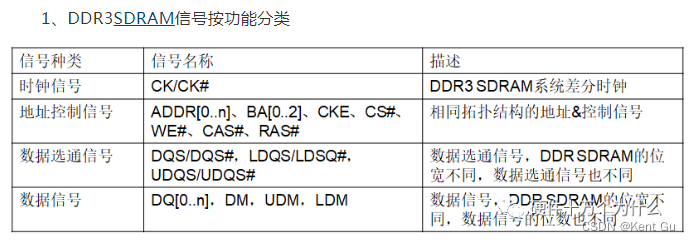

1. 信号分类 & 框架图

ddr3_dq:DDR3数据总线

ddr3_dqs_n:DDR3数据选通反相端

ddr3_dqs_p:DDR3数据选通同相端

ddr3_addr:DDR3地址总线

ddr3_ba:DDR3块地址输入

ddr3_ras_n、ddr3_cas_n、ddr3_we_n:DDR3命令输入端

ddr3_reset_n:DDR3复位

ddr3_ck_p:DDR3输入时钟同相端

ddr3_ck_n:DDR3输入时钟反相端

ddr3_cke:DDR3时钟使能

ddr3_cs_n:DDR3片选,用于使能命令解释器

ddr3_dm:DDR3输入数据掩码

ddr3_odt:DDR3启用内部终端匹配电阻

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?