本篇文章继续介绍处理器中存储器系统:处理器存储器管理,高速缓存Cache和虚拟内存。

处理器存储器管理

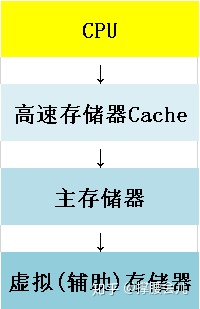

存储器系统的组织结构按作用可以划分为4级:寄存器、cache、主存储器和辅助存储器,对于简单的嵌入式系统来说,没有必要把存储器系统设计成4级,最简单的只需寄存器和主存储器即可。

寄存器包含在微处理器内部,用于指令执行时的数据存放,如:R0-R15等;

高速缓存Cache,通常采用SRAM类型的存储芯片;

主存储器是程序执行代码及数据的存放区,通常采用DRAM类型的存储芯片;

虚拟(辅助)存储器通常是Flash类型的芯片,作用类似通用计算机中的外存。

通常,在处理器存储系统中,级数越高的存储器内存大小越小,处理器读写速度越快。

接下来看一下处理器访问存储器时间(Average Memory Access Time)和其缩短的方法。首先,有以下公式:

其中Hit Time和Hit Rate分别为处理器成功读写存储器的时间和比率,反之,Miss Time和Miss Rate为读写失败的时间和比率。

高速缓存Cache

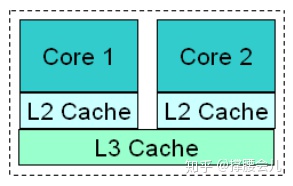

Cache位于CPU和主存储器DRAM之间,通常使用SRAM来实现,规模较小,但速度很高,CPU的速度远高于内存,当CPU直接从内存中存取数据时要等待一定时间周期,而Cache则可以保存CPU刚用过或循环使用的一部分数据,如果CPU需要再次使用该部分数据时可从Cache中直接调用,这样就避免了重复存取数据,减少了CPU的等待时间,因而提高了系统的效率。Cache又分为L2Cache(二级缓存)和L3Cache(三级缓存)。

当处理器采用高速缓存Cache时,对于写操作命中时hit而言,它的写内存操作有两种模式:直写模式(Write-through)和回写模式(Write-back)。

Write-through:在数据更新时,处理器同时写入缓存Cache和后端各存储器。此模式的优点是操作简单。缺点是因为数据修改需要同时写入内存,总线工作繁忙,内存的带宽被大大占用,因此运行速度会受到影响数据。假设一段程序在频繁地修改一个局部变量,局部变量生存周期很短,而且其他进程/线程也用不到它,处理器依然会频繁地在Cache和后端各存储器之间交换数据,造成不必要的带宽损失;

Write-back:在数据更新时只写入缓存Cache,而不是立即写入后端存储器。只在数据被替换出Cache时,被修改的缓存数据才会被写到后端存储器。此模式的优点是数据写入速度快,因为不需要写存储器;缺点是一旦更新后的数据未被写入存储器时出现系统掉电的情况,数据将无法找回(RAM特性)。对一Cache的多次写命中都在Cache中快速完成修改,只是需被替换时才写回速度较慢的主存储器,减少了访问主的次数从而提高了效率。

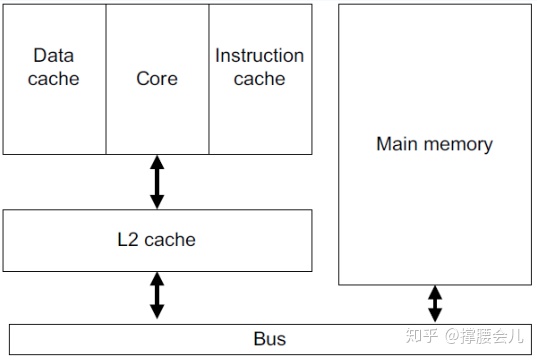

ARM架构中的Cache架构是Harvard结构的,分为data cache和instruction cache;还有一种Cache架构是统一型的,此时处理器中数据和指令均使用同一Cache。

虚拟内存

虚拟内存是计算机系统内存管理的一种技术。它使得应用程序认为它拥有连续可用的内存(一个连续完整的地址空间),而实际上,它通常是被分隔成多个物理内存碎片,还有部分暂时存储在外部磁盘存储器上,在需要时进行数据交换。与没有使用虚拟内存技术的系统相比,使用这种技术的系统使得大型程序的编写变得更容易,对真正的物理内存(例如RAM)的使用也更有效率。

虚拟内存能提供一大块连续的地址空间,对程序来说它是连续的,完整的,实际上虚拟内存是映射在多个物理内存碎片上,还有部分映射到了外部磁盘存储器上。虚拟内存的最大空间就是CPU的最大寻址空间,不受内存大小的限制,能提供比内存更大的地址空间,例如,对于一个32位处理器,它的寻址能力从0x00000000-0xFFFFFFFF即4GB大小的容量。

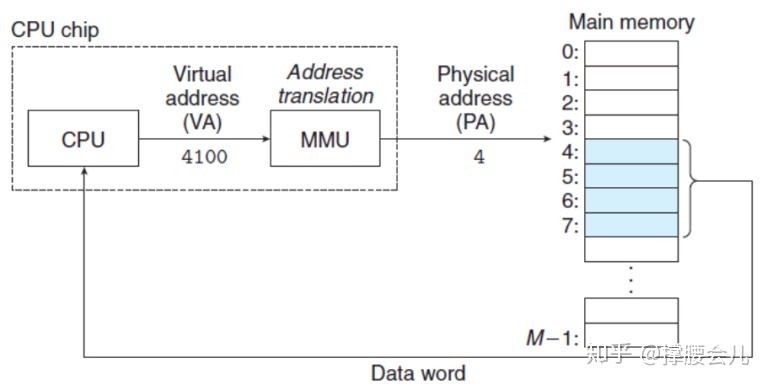

处理器要访问虚拟内存地址时,需要经过地址翻译成物理地址才能访问,需要通过内存管理单元MMU(memory management unit)来翻译成对应的内存物理地址。例如CPU要访问虚拟地址4100,通过MMU翻译成对应内存的物理地址4,然后CPU在内存地址4的位置上取到数据返回。

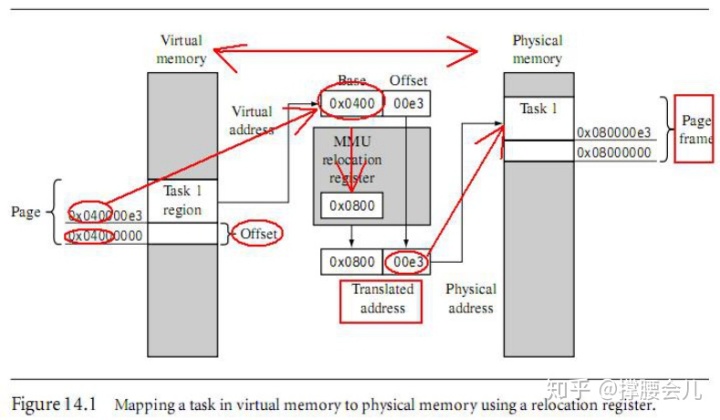

可见,在虚拟地址追寻回物理地址时起最大作用的部分为MMU,下面简单说一下MMU的工作原理。如下图所示,Task1在虚拟内存中起始地址为0x40000000,MMU中的重定位寄存器relocation register通过该任务的虚拟地址翻译得到它在物理地址中的起始地址为0x80000000。当其有偏移量时,加上偏移量即可得到物理地址;当Task1任务结束,Task2在虚拟内存中起始地址依然为0x40000000时,可通过修改MMU中重定位寄存器来使其映射到另外的物理地址上。虚拟地址中从起始地址到加上offset地址称为页(Page),映射到物理地址的部分称为页帧(Page frame)。

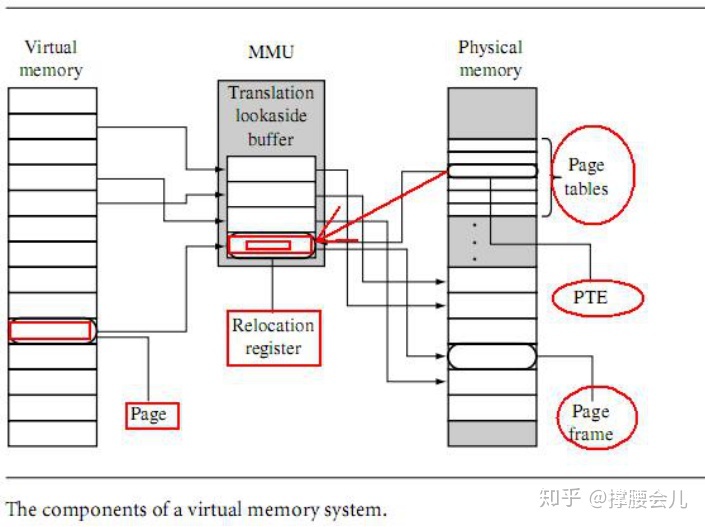

如上所述,一个重定位寄存器仅可译出一个物理地址,所以可以引入旁路缓冲器TLB(Translation Lookaside Buffer),它由64个重定位寄存器Cache组成。除了使用重定位寄存器外,MMU还使用在主存中的表来存放描述虚拟内存映射的数据,这个表被称为页表(Page Table)而页表的每个子表存储了一个页转换到物理存储器的一个页帧所需要的信息。

以上是对虚拟内存映射物理内存过程的简单介绍,谢谢。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?