1.什么是Cache?

高速缓存(Cache)主要是为了解决CPU运算速度与内存(Memory)读写速度不匹配的矛盾而存在, 是CPU与内存之间的临时存贮器,容量小,但是交换速度比内存快。

百度百科是这样介绍缓存的:

CPU要读取一个数据时,首先从Cache中查找,如果找到就立即读取并送给CPU处理;如果没有找到,就用相对慢的速度从内存中读取并送给CPU处理,同时把这个数据所在的数据块调入Cache中,可以使得以后对整块数据的读取都从Cache中进行,不必再调用内存。

正是这样的读取机制使CPU读取Cache的命中率非常高(大多数CPU可达90%左右),也就是说CPU下一次要读取的数据90%都在Cache中,只有大约10%需要从内存读取。这大大节省了CPU直接读取内存的时间,也使CPU读取数据时基本无需等待。总的来说,CPU读取数据的顺序是先Cache后内存。

2.Cache的分类?

Cache硬件实现通常有一级,二级,或者很多级Cache。这里说以二级cache为例。

对于一级Cache,又有 Instruction Cache(指令缓存,通常称为 I-Cache)和 Data Cache(数据缓存,通常称为 D-Cache)之分,二级Cache有Scache。二级cache一般都大于一级cache,一级cache是最靠近CPU的,然后是二级cache。

本文是本人学习什么时候需要写回缓存,什么时候无效缓存,什么时候写回并无效缓存的总结。

以D-Cache为例,指令缓存 I-Cache 原理一样。

3.Cache 数据访问原理

写入数据时:

- 第一步,CPU 将数据写入 Cache;

- 第二步,将 Cache 数据传送到 Memory 中相应的位置;

读取数据时:

- 第一步,将 Memory 中的数据传送到 Cache 中;

- 第二步,CPU 从 Cache 中读取数据;

具体硬件实现,Cache写操作有写直通和写回两种

(1)写直通(write through)

当执行store操作时,cache中的数据被修改,那么主存中的数据也会被同步更新,两者保持一致。

(2)写回(write back)

当执行store操作时,cache中的数据被修改,并不会立即同步数据到主存中,而是在tag中将dirty位置位。当cache中的数据被替换或者显式地写回时,才会将数据更新到主存中。

写直通的方式性能低于写回方式,现在的 CPU 设计基本上都是采用 Cache 回写方式。

4.Cache line

cache line

cache被平均分成了多个cache line。

cache line是cache和DDR之间数据传输的最小单位。

什么意思呢?当CPU试图load一个字节数据的时候,如果cache miss,那么cache控制器会从主存中一次性的load cache line大小的数据到cache中。

例如,cache line大小是64字节。CPU即使读取一个byte,在cache缺失后,cache会从主存中load 64字节填充整个cache line

每条cache line 都有两个标志位。

vaild bit:表示cache line中数据是否有效(例如:1代表有效;0代表无效)。当系统刚启动时,cache中的数据都应该是无效的.

读:

1. 缓存没有命中(cache miss或者cache line状态为invalid),直接从内存读取数据+写 入 到cache+标记cache line为valid

2. 缓存命中 && cache line状态为valid,直接从cache中读取数据

写:

1. 向所有cache发送写信号

2. 如果有cache中有这条数据 && cache line状态为valid,将这个cache line的状态改为invalid

3. 将新数据写入到内存与cache,并将相关的cache line标记为valid

优点:减少了从主存中读取数据的次数

缺点:每次写操作都要刷回主存

dirty bit:表示cache line里面的数据是否和下一级存储一致。=0非dirty,和下一级存储一致,=1 dirty,和下一级存储不一致。

cache的3种操作:

clean:

检查对应内存cache line 的dirty bit。如果dirty bit为1,将cache line的内容写回下一级存储,并将dirty bit置为0.

invalid:

检查对应内存cache line 的valid bit.如果valid bit 为1,置为0.

flush:

每条cache line 先clean,再invalid.

6.因为Cache引起的数据不一致问题

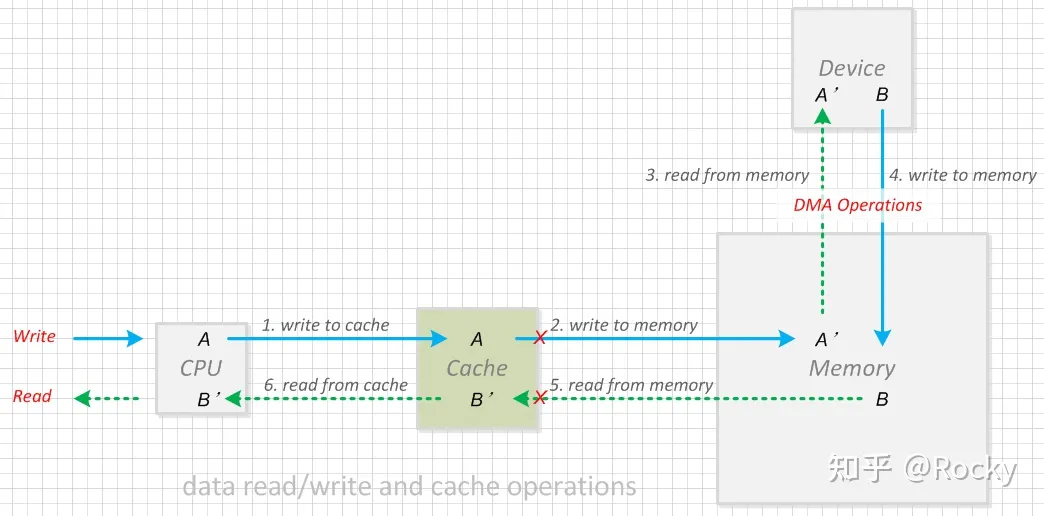

在有设备进行 DMA 操作的情况下,设备读写数据不再通过 Cache,而是直接访问内存。在设备和 CPU 读写同一块内存时,所取得的数据可能会不一致,如图二。

设备和CPU读写同一块内存时数据不一致

图二、设备和CPU读写同一块内存时数据不一致

CPU 执行步骤1将数据 A 写入 Cache,但并不是每次都会执行步骤 2 将数据 A 同步到内存,导致 Cache 中的数据 A 和内存中的数据 A’不一致;步骤 3 中,外部设备通过 DMA 操作时直接从内存访问数据,从而取得的是A’而不是A。

设备DMA操作完成后,通过步骤 4 将数据 B 写入内存;但是由于内存中的数据不会和 Cache 自动进行同步,步骤 5不会被执行,所以 CPU 执行步骤 3 读取时数据时,获取的可能是 Cache 中的数据 B’,而不是内存中的数据B;

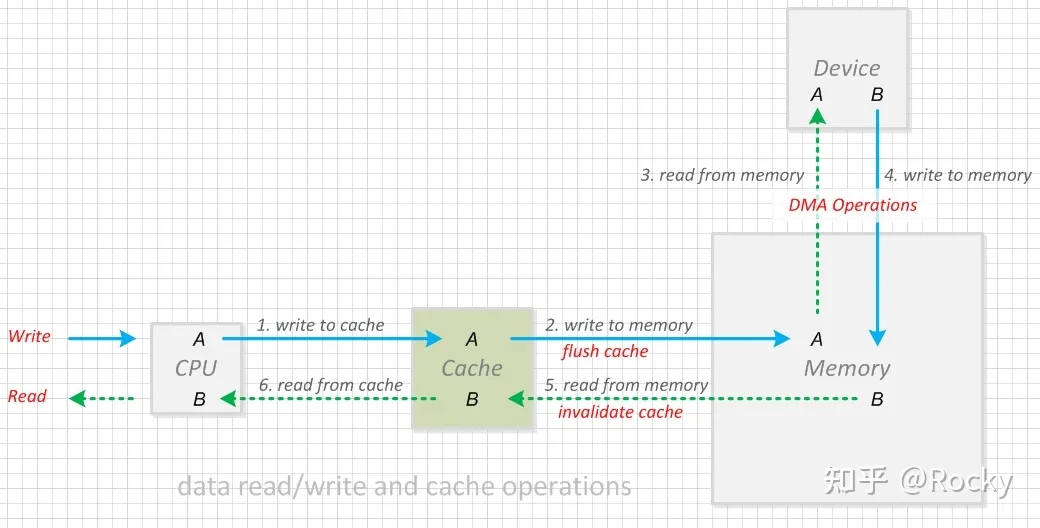

在 CPU 和外设访问同一片内存区域的情况下,如何操作 Cache 以确保设备和 CPU 访问的数据一致就显得尤为重要,见图三。

Cache操作同步数据

图三、Cache操作同步数据

CPU 执行步骤 1 将数据 A 写入 Cache,由于设备也需要访问数据 A,因此执行步骤 2 将数据 A 通过 flush 操作同步到内存;步骤 3 中,外部设备通过 DMA 操作时直接从内存访问数据 A,最终 CPU 和设备访问的都是相同的数据。

设备 DMA 操作完成后,通过步骤 4 将数据 B 写入内存;由于 CPU 也需要访问数据 B,访问前通过 invalidate 操作作废 Cache 中的数据,从而通过 Cache 读取数据时 Cache 会从内存取数据,所以 CPU 执行步骤 6 读取数据时,获取到的是从内存更新后的数据;

参考链接:https://zhuanlan.zhihu.com/p/505025934

刷cache的3种操作:clean/invalid/flush_小葫芦写代码的博客-CSDN博客_cache flush

本文介绍了缓存(Cache)的基本概念及其在计算机系统中的作用,包括缓存的分类、工作原理以及不同类型的缓存操作(如写直通与写回)。此外还探讨了缓存一致性问题及解决方案。

本文介绍了缓存(Cache)的基本概念及其在计算机系统中的作用,包括缓存的分类、工作原理以及不同类型的缓存操作(如写直通与写回)。此外还探讨了缓存一致性问题及解决方案。

202

202

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?