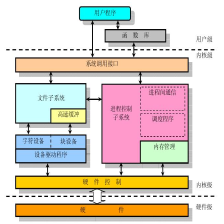

宏内核(Monolithic Kernel)和微内核(Microkernel)在系统实时性方面的表现存在显著差异,主要取决于它们的架构设计、任务调度机制以及系统调用的实现方式。以下是详细对比分析:

1. 宏内核的实时性表现

优势:

• 低延迟的系统调用

宏内核将所有核心功能(如文件系统、驱动、内存管理)直接编译到内核空间,系统调用无需跨进程通信(IPC),直接在内核态完成,延迟极低(通常纳秒级)。

示例:Linux(宏内核)通过实时补丁(PREEMPT_RT)可实现微秒级响应。

• 高效的中断处理

中断服务程序(ISR)直接运行在内核态,与内核功能无缝集成,中断延迟可控。

• 共享内存的高效通信

内核模块间通过直接函数调用共享数据,无需IPC开销,适合对延迟敏感的任务。

劣势:

• 资源竞争导致不可预测性

多任务竞争内核资源(如锁、内存)时可能引发优先级反转或死锁,破坏实时性约束。

• 扩展性受限

内核代码庞大,修改或添加新功能可能引入性能波动,难以保证确定性响应。

典型场景:

传统实时系统(如VxWorks早期版本)通过宏内核+实时调度策略(如EDF、RM)实现硬实时,但需严格避免内核资源竞争。

2. 微内核的实时性表现

优势:

• 模块化与隔离性

核心功能(如驱动、文件系统)运行在用户态,通过IPC通信,避免内核级资源竞争,提高可预测性。

• 动态扩展能力

新功能模块可独立加载/卸载,不影响内核稳定性,适合混合关键性系统(Mixed-Criticality Systems)。

劣势:

• 高IPC开销

用户态模块间通信需跨特权级(如Mach的IPC延迟约1-10μs),可能成为实时任务的瓶颈。

• 调度复杂性

微内核需协调内核态与用户态任务的调度,若设计不当(如L4早期版本),可能导致调度延迟不可控。

优化方向:

• 优化IPC机制:如seL4采用零拷贝IPC,将延迟降至亚微秒级。

• 混合内核设计:如QNX结合微内核的隔离性与部分宏内核的高效性,实现硬实时(ISO 26262认证)。

典型场景:

航空航天(ARINC 653标准)、汽车电子(AUTOSAR Adaptive)等强实时需求领域。

3. 关键对比总结

| 维度 | 宏内核 | 微内核 |

|---|---|---|

| 系统调用延迟 | 极低(纳秒级) | 较高(微秒级,依赖IPC优化) |

| 中断延迟 | 低(直接处理) | 可能较高(需用户态模块协作) |

| 可预测性 | 差(资源竞争风险) | 高(隔离性强) |

| 扩展性 | 低(内核修改风险大) | 高(模块化设计) |

| 典型实时方案 | PREEMPT_RT补丁 | seL4零拷贝IPC、QNX混合架构 |

4. 实际应用建议

• 硬实时系统:优先选择微内核(如seL4)或优化后的宏内核(如VxWorks + RT补丁),需严格测试IPC延迟。

• 软实时系统:宏内核(Linux)通过Cgroups、实时调度类(SCHED_FIFO)即可满足需求。

• 混合关键性系统:微内核(QNX)通过分区隔离保障安全关键任务,同时运行非实时应用。

5. 技术演进趋势

• 混合内核方案:如Redox OS尝试在微内核中内联高频功能模块,平衡性能与隔离性。

• 硬件加速:利用RISC-V的S指令集或Intel TME减少IPC开销,提升微内核实时性。

实际选择需权衡实时性需求、开发成本与硬件资源,现代实时系统常采用混合架构(如AUTOSAR Classic + Adaptive)。

1379

1379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?