1 引言

现代CPU中,为了提高CPU的执行效率,高速缓存必不可少。关于Cache工作原理可以参考我之前的文章

与ARM等架构相同,MIPS架构CPU也是采用多级cache。我们这里关心的是L1级缓存:I-cache和D-cache。通过这种哈弗结构,指令和数据读取可以同时进行。

2 Cache工作原理

从概念上讲,Cache是一个关联性内存,数据存入其中,可以通过关键字进行查找。对于高速Cache而言,关键字就是完整的内存地址。因为想要查询高速Cache,就必须与每一个关键字进行比较,所以合理使用Cache非常重要。

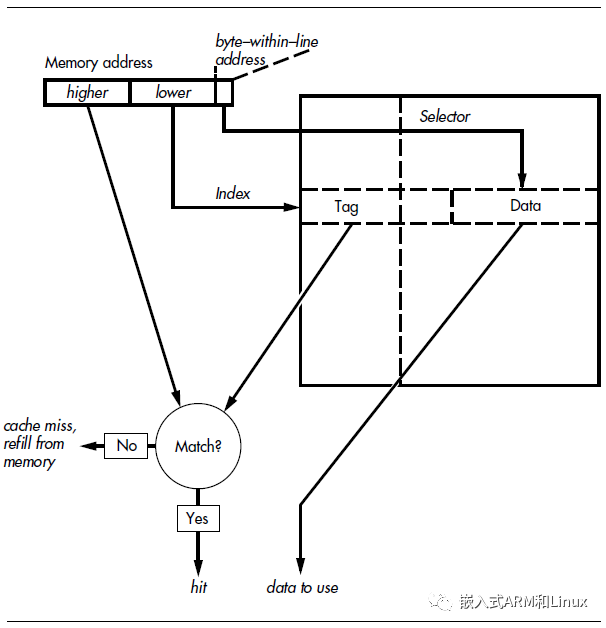

下图是一个直接映射的Cache,这是MIPS架构早期使用的Cache原型。这种原型的好处就是简单直接好理解,也是后来Cache发展的垫脚石。

它的工作方式就是,使用地址中的低位作为index,索引在Cache中的位置,也就是位于哪一行。当CPU发出某个地址后,使用地址中的高位与Cache中的tag位进行比较,如果相同,则称为”命中”;否则,”未命中”。命中,则将Cache中的数据拷贝到CPU寄存器中;如果没有命中,则重新从内存中读取数据,并将其加载到对应的Cache位置中。如果每行包含多个Word数据的话,则使用地址的最低几位进行区分。

这样直接映射的Cache有优点也有缺点:优点是,一一直接映射,遍历时间肯定短,可以让CPU跑的更快。但同时也带来了缺点,假设你正在交替使用2个数据,而且这2个数据共享Cache中的同一个位置(它们地址中的低位刚好一样)。那么,这2个数据会不断地将对方从Cache中替换出来,效率将急剧下降。

关于全关联Cache和直接映射Cache的概念可以参考文章Linux内核2-Cache基本原理

如果是全关联高速缓存不会存在这种问题,但是遍历时间变长,而且设计复杂。

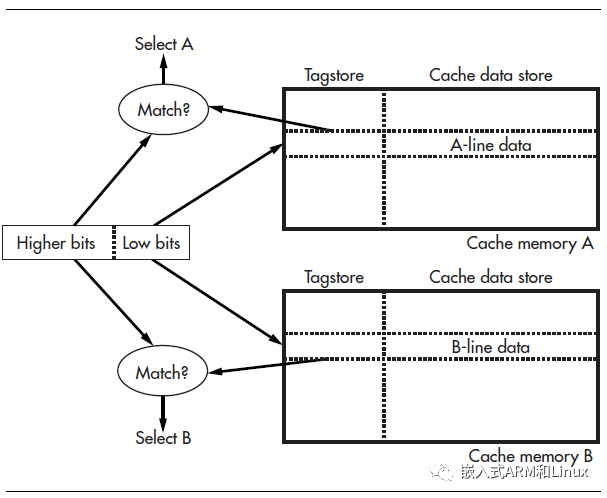

折中的方案就是,使用一个2路关联Cache,效果相当于运行了两个直接映射的并行Cache。内存中的数据可以映射到这两路Cache中的任意一个上。如图4.2所示:

如图所示,对于一个地址,需要比较两次。四路组相关联的Cache在片上高速缓存中也比较常见(比如ARM架构)。

在多路相关联的Cache中,替换Cache中的哪个位置具有多路选择。理想的方法肯定是替换”最近最少使用”的缓存line,但是要维护严格个LRU原则,意味着每次读取Cache时,需要更新每个Cache line的LRU位。而且对于超过4路组相关联的Cache,维护严格的LRU信息变得不切实际。实际的缓存都是使用”最近最少填充”这样的折中算法来选择要替换的缓存line。

当然,这也是有代价的。相比直接映射的Cache,多路组相关联的Cache在缓存芯片和控制器间需要更多的总线进行连接。这意味太大的Cache无法集成到单个芯片中,这也是放弃直接映射Cache的因素之一。

当运行一段时间后,Cache肯定就会填满,再获取新的内存数据时,需要从Cache中替换数据出去。这时候就要考虑Cache和内存的一致性问题。如果Cache中的数据比内存中的新,就需要将这些数据写回到内存中。

这就带来一个问题:Cache如何处理写操作。

3 早期MIPS架构CPU的write-though缓存

上面的讨论中,好像假定从内存中读取数据。但是CPU不只是读,还有写。write-though缓存就是不管三七二十一,数据总是写入内存中。如果数据需要在Cache中有一个备份,那么这个备份也要更新。这样做,我们不用管Cache和内存的数据是否一致。直接把Cache中替换出的数据丢弃即可。

如果写数据很多,我们等到所有的写操作完成,会降低CPU的执行速度。不过这个问题可以修正,通过使用一个称为write-buffer(写缓冲器)的FIFO方式的缓存区保存所有要写入内存的数据。然后由内存控制器读取数据,并完成写操作。

早期的MIPS处理器有一个直接映射的Cache和一个write-buffer。只要主存系统能够很好地消化这些以CPU平均速率产生的写操作即可。但是,CPU的发展速度太快了。很快,CPU的速度就超过了主内存系统可以合理消化CPU所有写操作的临界点了。

4 MIPS CPU的回写高速缓存

尽管早期的MIPS架构的CPU使用简单的透写Cache,但是,CPU的频率提升太快了,很快透写Cache就无法满足CPU写操作的需求,大大拖慢了系统的运行速速。

解决方案就是把要写的数据保存到Cache中。且在对应的Cache行中标记dirty位。后面根据这个标志位再写回到相应的内存中。如果当前Cache中没有要写入地址对应的数据,我们可以直接把数据写到内存中,不用管高速缓存。

5 高速缓存设计中的一些其它考虑

上世纪的80年代后期和90年代初期,研究人员开始研究如何构建Cache。下面我们看看,Cache的发展都经历了哪些历程:

关于物理寻址/虚拟寻址:

我们知道,CPU正在运行OS时,应用程序的数据和指令地址都会被转换成物理地址,继而访问实际的物理内存。

如果Cache单纯地工作在物理地址上,很容易管理(后面我们再介绍为什么)。但是,虚拟地址需要尽快的

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

283

283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?