Lattice Diamond目前支持Lattice大部分器件的开发工作,也是用户使用最频繁的软件,相关软件可以从Lattice官网下载到,这次仅仅粗略讲一下用户使用Diamond软件开发FPGA的大致流程。

1. 建立新工程

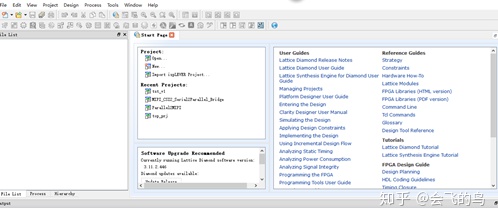

以Lattice Diamond 3.11版本为例,安装免费的license,打开Diamond软件后,可以观察到如下界面,Start Page右侧是Lattice Diamond相关文档说明,点击中间New…,建立新工程。

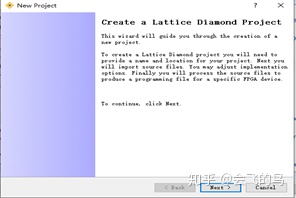

点击Next。

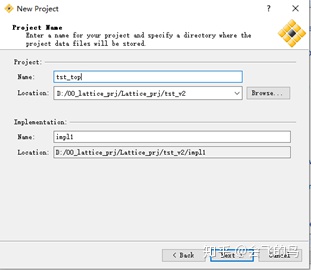

手动选择FPGA工程所在文件夹位置,并给工程命名,然后点击Next。

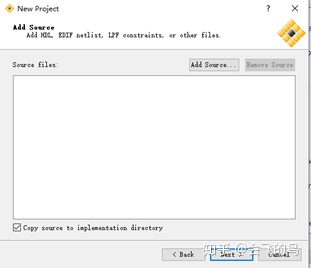

新出现的对话框,用户可以导入之前写的一些Verilog文件,这里由于是新工程,所以就不导入了,直接点击Next。

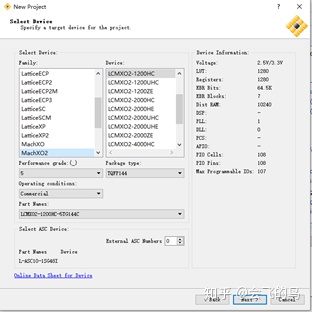

选择FPGA后者CPLD型号,这里我们随便选择Lattice的MachXo2-1200系列,然后点击Next。

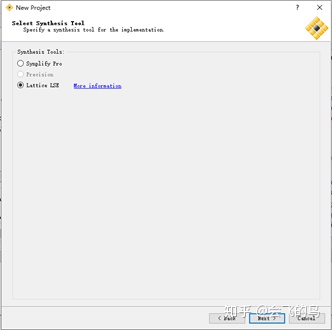

出现综合工具选择界面,Lattice Diamond综合工具有两种可选,Synplify Pro为第三方综合工具,早期Diamond只有这么一个综合工具,后来Lattice这边自己开发了一个Lattice LSE综合工具。这两个用户可以随便选一个,然后点击Next。

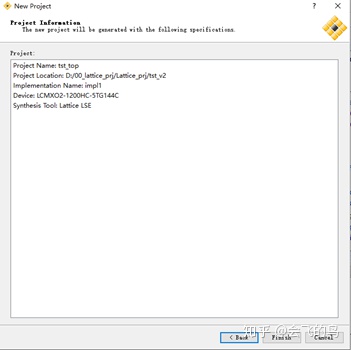

新出现的对话框是对Lattice建立工程的一个总结,点击Finish,新的工程就建立好了。

2. 编写Verilog代码

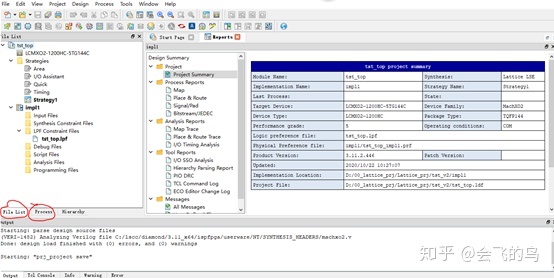

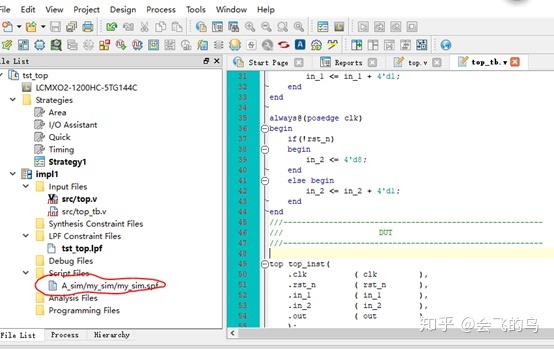

以下是Diamond软件建立好的工程,File List用于显示工程器件信息和各种代码文件,Process是工程进行综合、编译、布局、布线以及下载文件生成的地方。

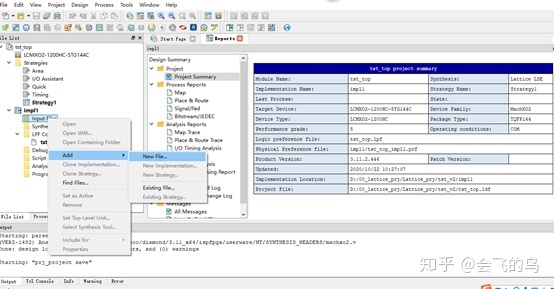

有多种向工程中添加Verilog文件的方式,我习惯于之间右击Input Files,然后选择Add,点击New File…,当然用户也可以选择Existing file…,然后从新出现的对话框中选择要导入的Verilog文件。

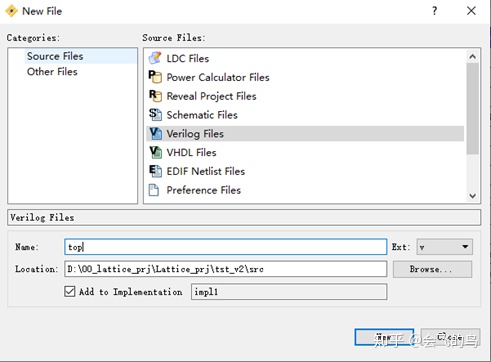

点击New File…后,出现以下对话框,文件夹路径中的src文件夹原本是没有的,我这边是想把所有的Verilog代码都放在一个文件夹中,所以先新建了一个叫Src的文件夹,我将新建的Verilog文件命名为top,点击New。

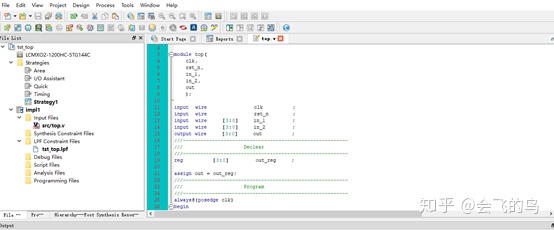

打开input files下面的src/top.v文件,出现右侧见面,原本top.v文件是什么都没有的,图中所示代码是我这边刚刚写完的,功能是out = in1+in2.

3. 编写仿真文件

很多用户没有仿真的习惯,有些是因为仿真激励太难编写,有些认为后面硬件调试的时候也可以调整代码,还有些纯粹认为仿真可有可无。不过,这里还是建议用户在有条件的情况下,仿真一下工程,这样可以规避大多数问题,节省后续调试时间。

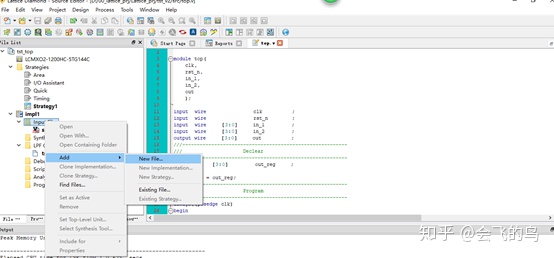

那么工程的仿真tb文件如何编写呢,仍然是右击Input Files。

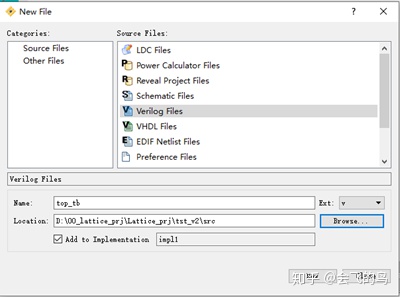

和新建Verilog文件流程一个,只不过名称改为了top_tb,点击New。

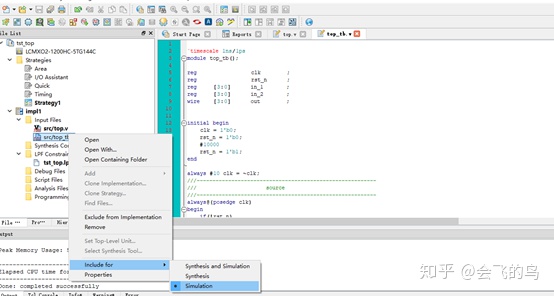

然后右击新建的src/top_tb.v文件,选择include for,然后点击Simulation,这就告诉Diamond软件,这个文件仅仅用于仿真,并不参与实际的综合、编译等。

① 打开仿真工程

编写好src/top_tb.v文件后,就可以打开仿真软件了,Lattice Diamond自带的仿真软件为Active-HDL,当然用户也可以用第三方仿真软件Modelsim,这里以Active-HDL为例进行讲解。

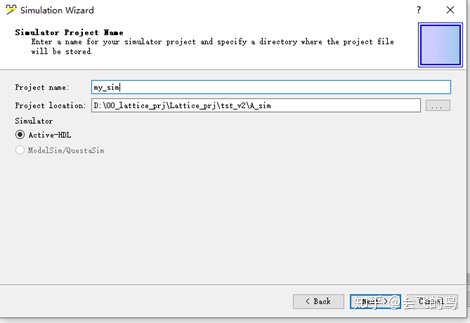

点击下图红圈所示图标,或者Tools菜单下打开Simulation Wizard,点击Next。

在工程所在目录新建A_sim文件夹,Project location选择该文件夹路径,Project Name输入仿真工程名称my_sim,点击Next。

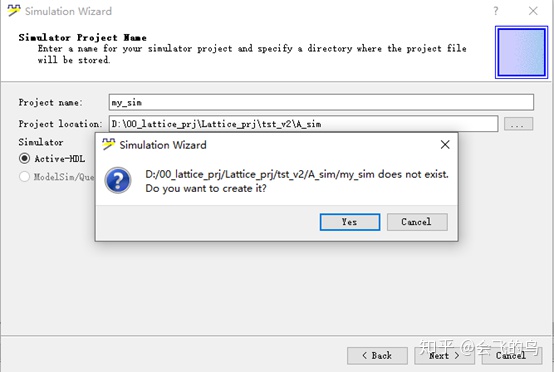

点击Yes。

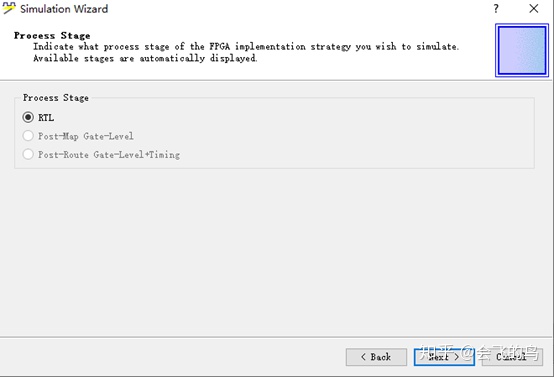

点击Next。

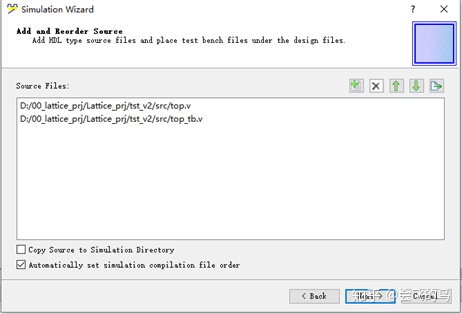

在这里,用户可以选择将src文件夹下的Verilog文件拷贝到A_sim文件夹下,也就是仿真工程目录,也可以不拷贝,直接仿真工程关联src文件夹下Verilog文件。我们这里选择不拷贝,直接关联,点击Next。

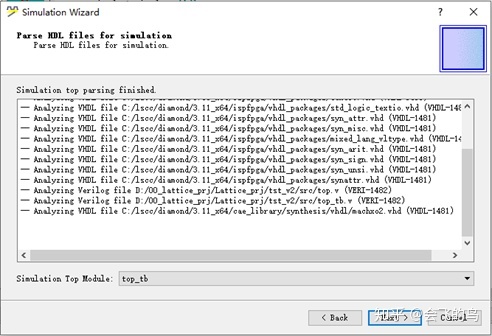

选择合适的仿真顶层文件,这里默认选择了top_tb,点击Next。

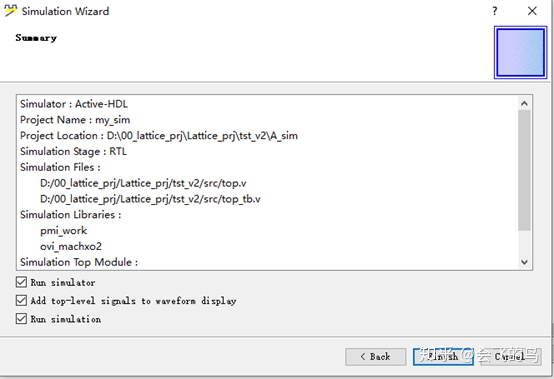

这个界面是对仿真工程的一个总结,点击finish。

点击finish以后,Diamond界面会出现两种变化,一是File List多了一个my_sim.spf仿真工程文件(双击这个文件可以打开Active-HDL仿真工程),二是Active-HDL自动弹出。

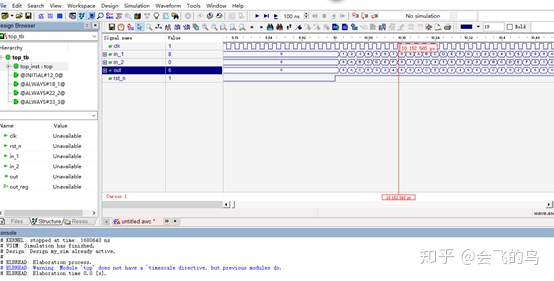

② Active-HDL

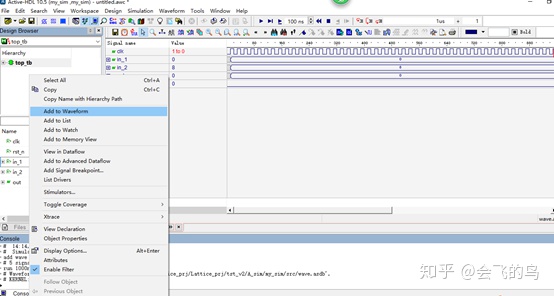

下图Active-HDL界面,在左侧窗口Design Browser的Structure选取top_tb,右击需要观测的信号,点击Add to Waveform,可将其添加到右侧时序观测波形界面。

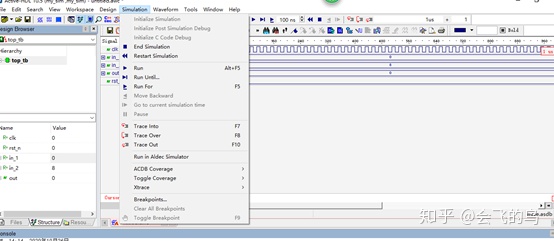

此外,Simulation菜单栏下,有对波形仿真的各种操作,一般来说经常用到的只有Run、Pause、End Simulation、Restart Simulation。

这里有个小技巧,用户重新修改Verilog文件后,不想重新关闭Active-HDL,然后再打开,可以首先点击下图红圈处Build,然后再点击Simulation菜单栏下的Restart Simulation。

本文介绍了使用Lattice Diamond软件开发FPGA的基本步骤,包括建立新工程、编写Verilog代码和仿真文件。在建立工程时,详细讲解了选择器件、设置综合工具的过程。接着,演示了如何添加和编辑Verilog代码,以及创建仿真文件。最后,阐述了使用Active-HDL进行仿真,包括添加波形和控制仿真过程的关键操作。

本文介绍了使用Lattice Diamond软件开发FPGA的基本步骤,包括建立新工程、编写Verilog代码和仿真文件。在建立工程时,详细讲解了选择器件、设置综合工具的过程。接着,演示了如何添加和编辑Verilog代码,以及创建仿真文件。最后,阐述了使用Active-HDL进行仿真,包括添加波形和控制仿真过程的关键操作。

2457

2457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?