前言

英文名Lattice Semiconductor (Shanghai), Ltd. 莱迪思(NASDAQ: LSCC)是低功耗、可编程器件的领先供应商。我们为不断增长的通信、计算、工业、汽车和消费市场客户提供从网络边缘到云端的各类解决方案。

lattice的官方产品指南:https://www.latticesemi.com/zh-CN/Products

lattice的官方软件使用手册:Lattice Radiant | FPGA Design Software | Lattice Semiconductor

lattice软件license:Lattice Radiant | FPGA Design Software | Lattice Semiconductor

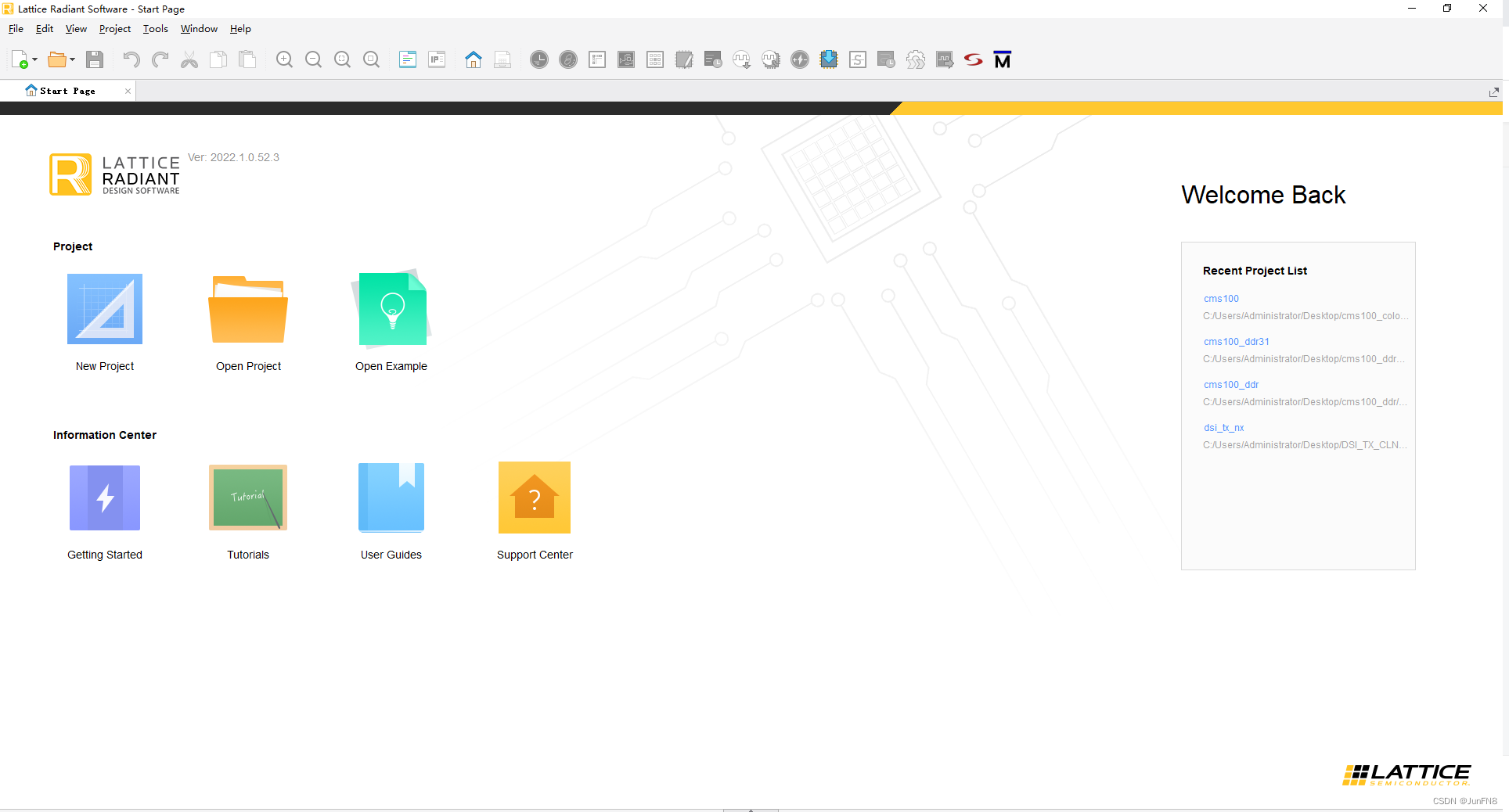

步骤一:安装好Lattice软件并打开

步骤二:创建Lattice工程

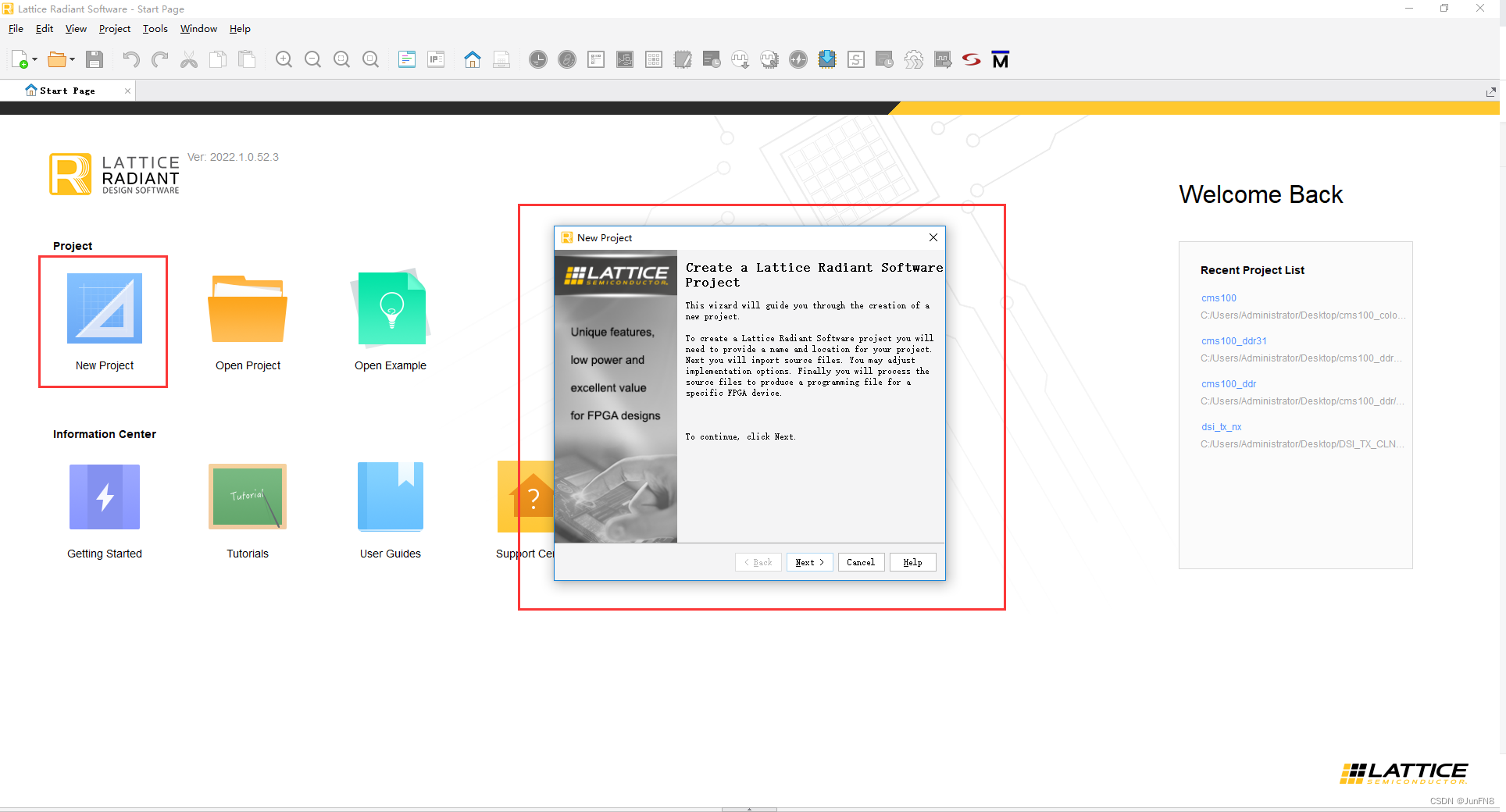

点击New Project,然后Next

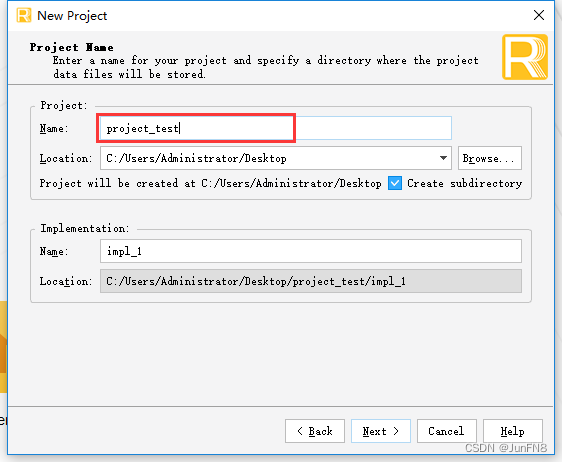

在红框中输入自己的工程名,例如:project_test

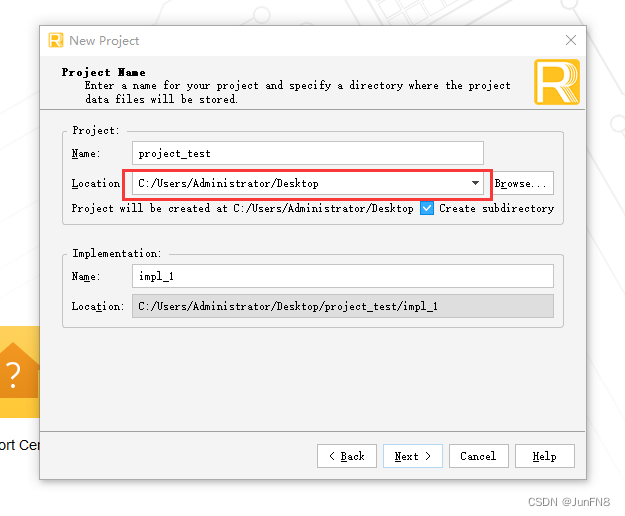

选择创建工程的目录,作者是创建在桌面上。

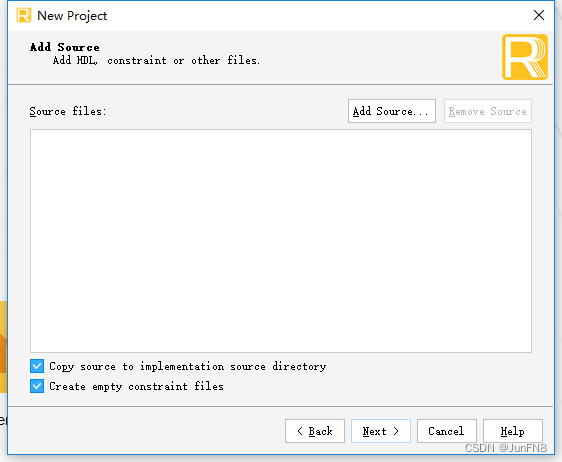

是否要添加源文件,作者这里先不添加。勾选下面两个选项创建约束文件。然后Next

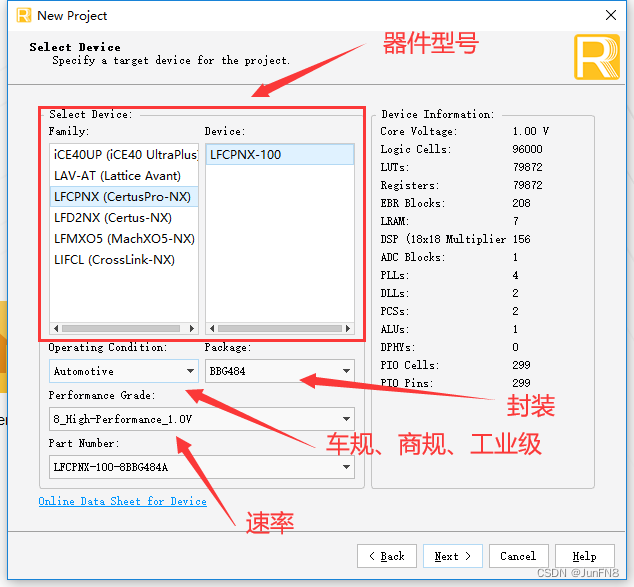

选择器件以及规格,Next

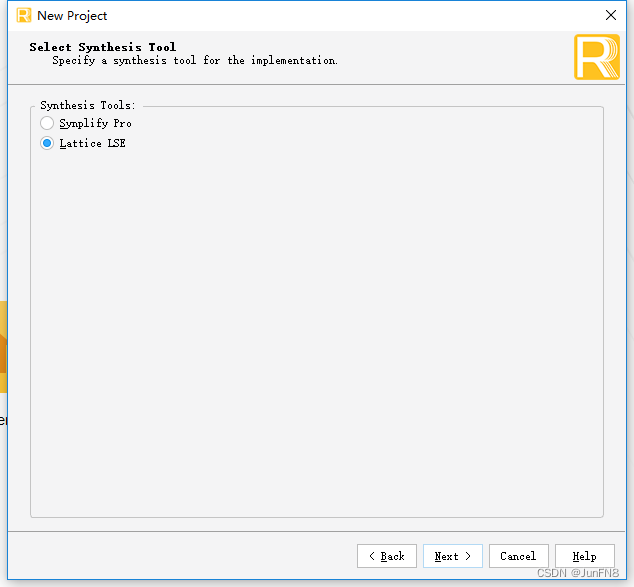

综合工具选择LSE,然后Next

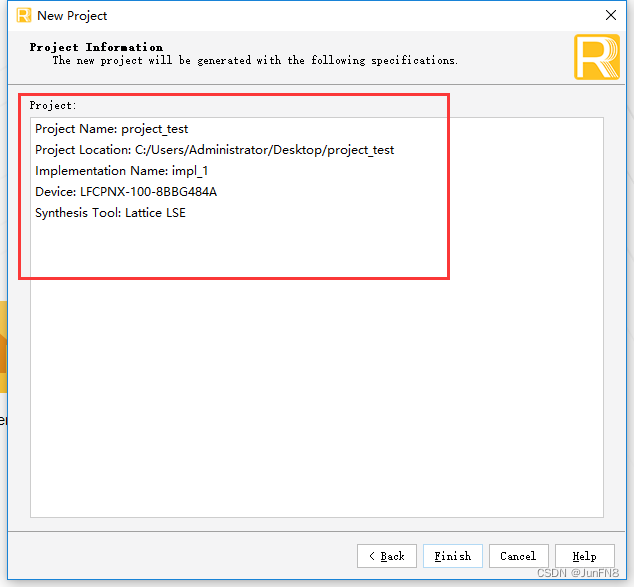

最后会出现你选择的所有信息,让你确认。没问题就Finish

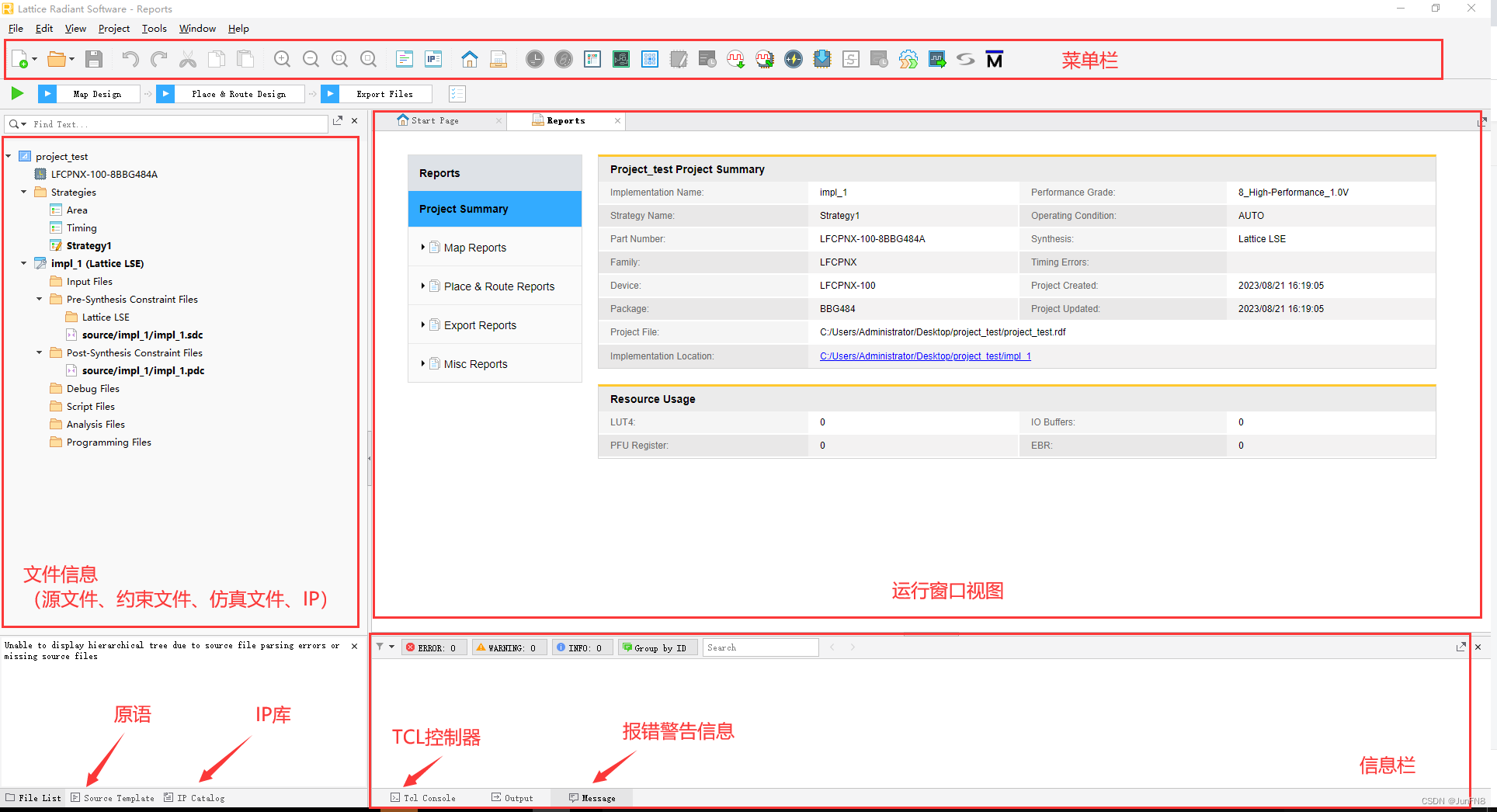

步骤三:熟悉开发环境

工程创建成功后的初始页面

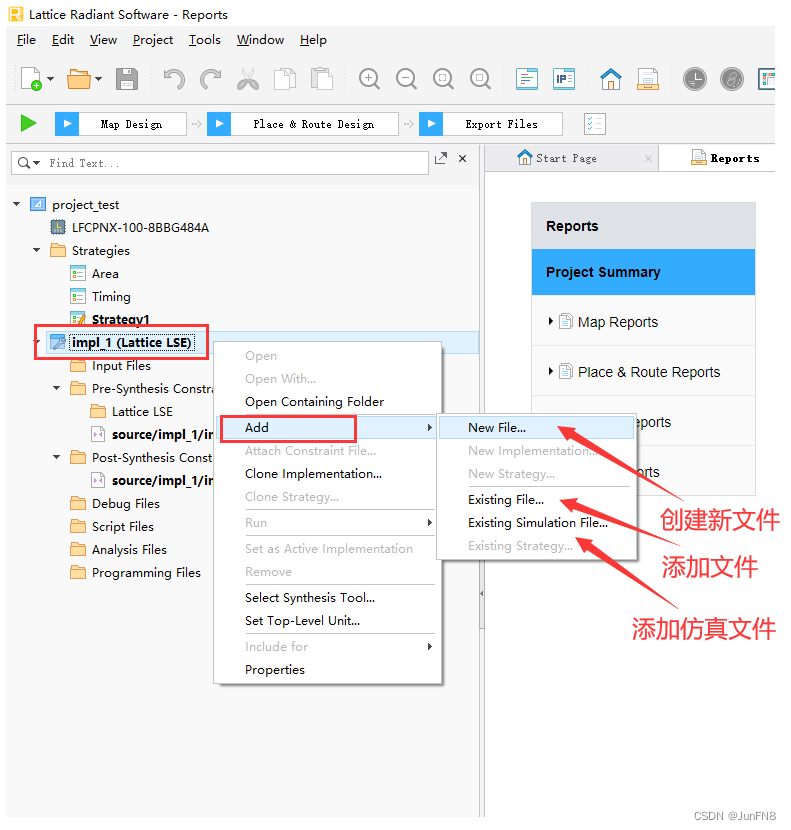

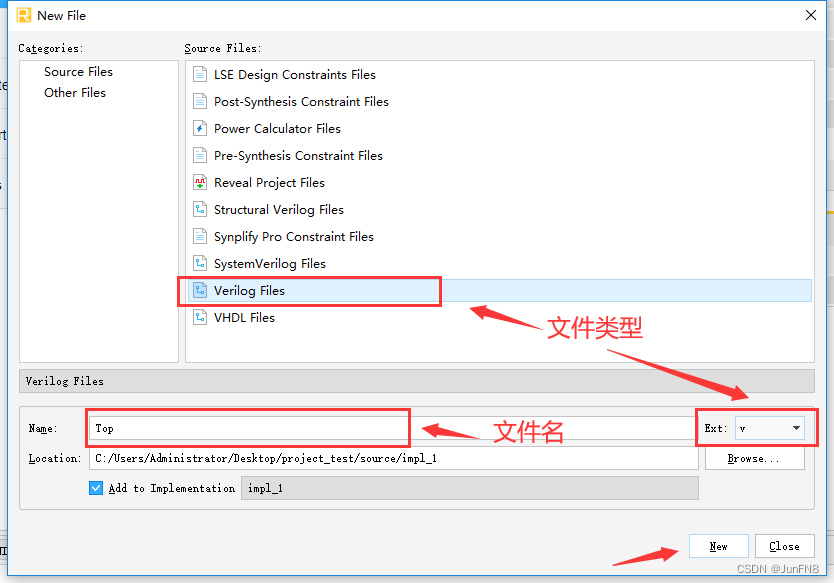

先来创建/添加一个.v源文件,如下图

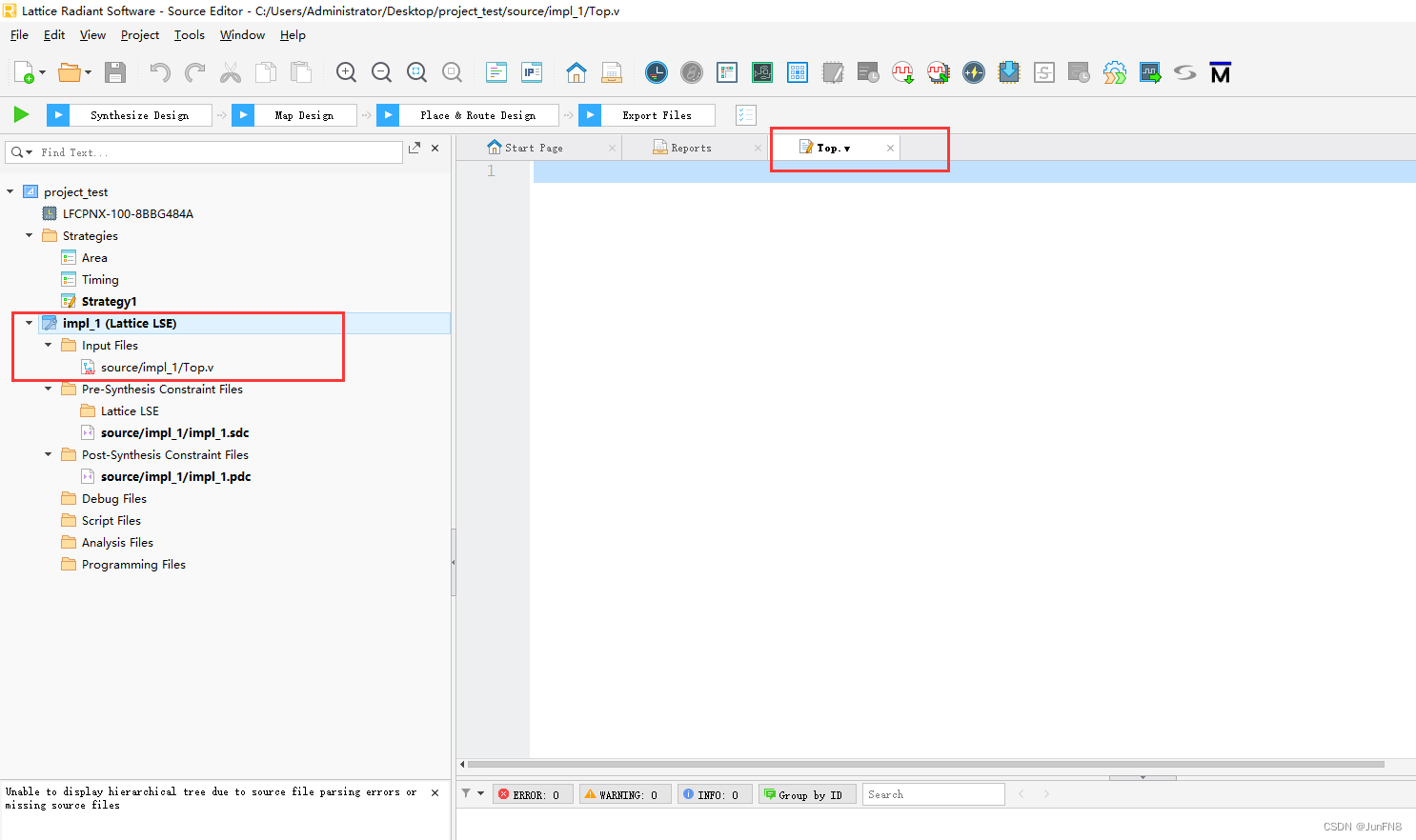

创建后会到input Files文件夹下,并打开。

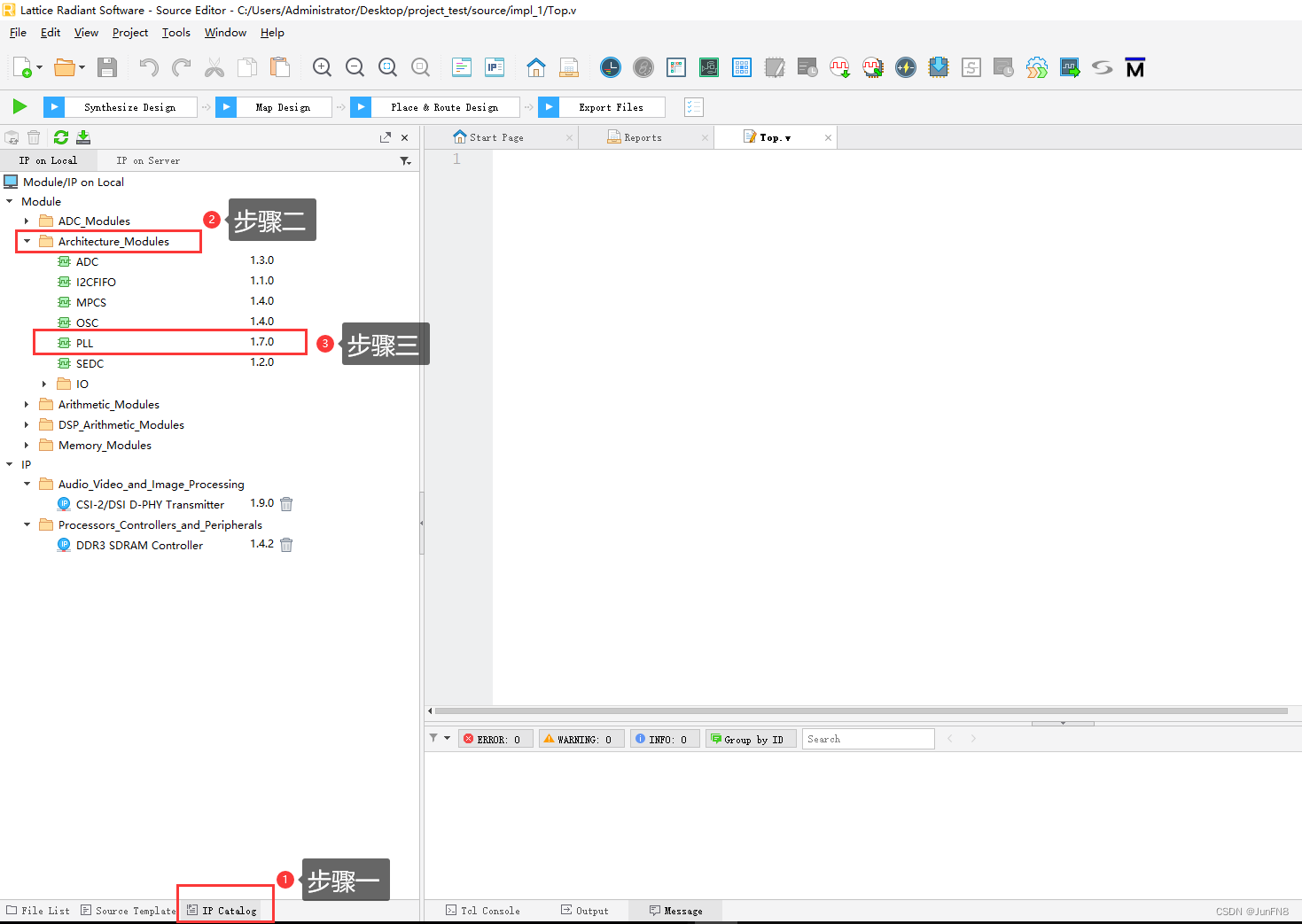

添加IP到工程,例如PLL锁相环这个IP添加步骤。

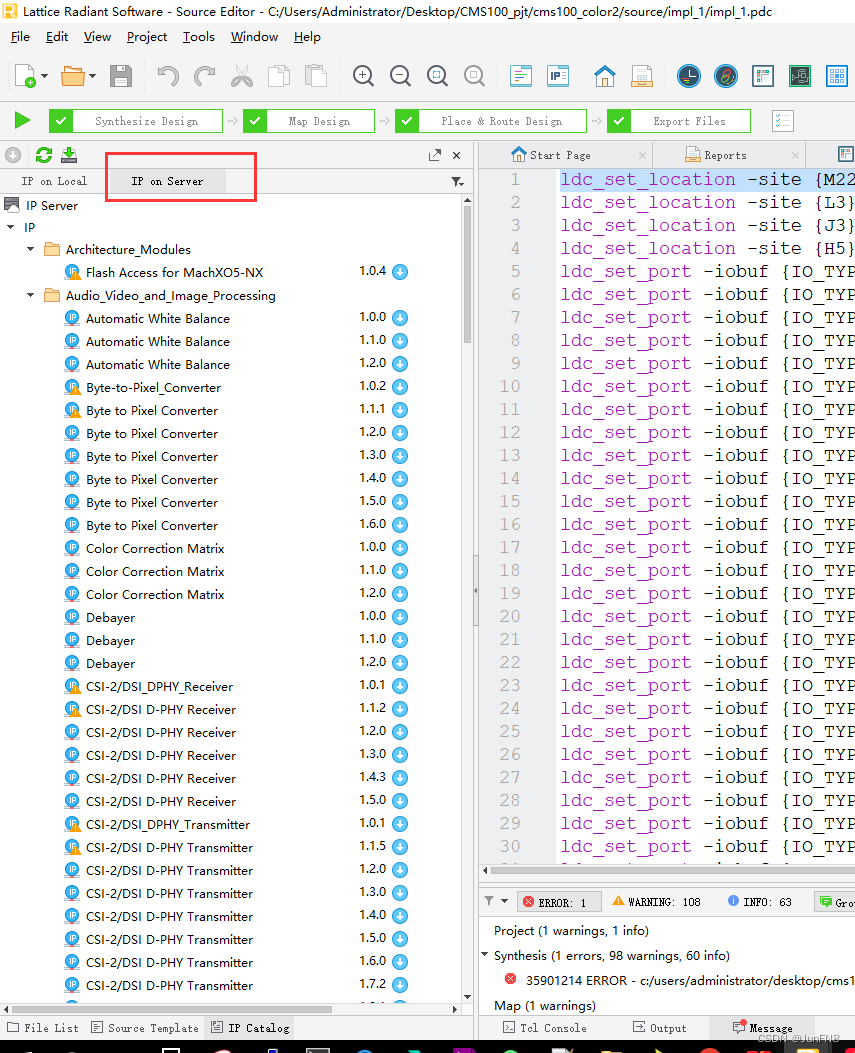

当然还有更多复杂的IP,lattice软件需要你自己选择安装。

IP如果不会使用,每个IP也对应有官方的使用手册可以找到,如下图。

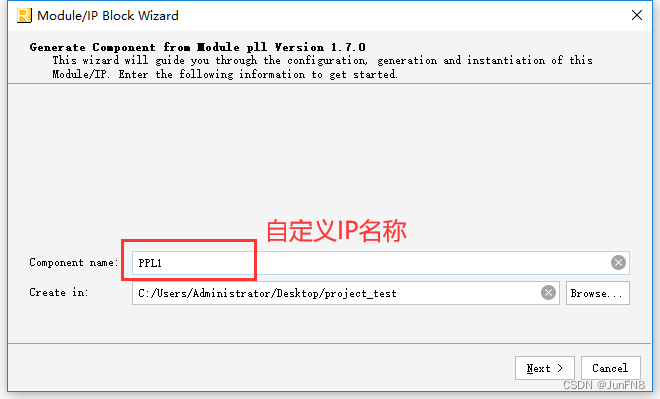

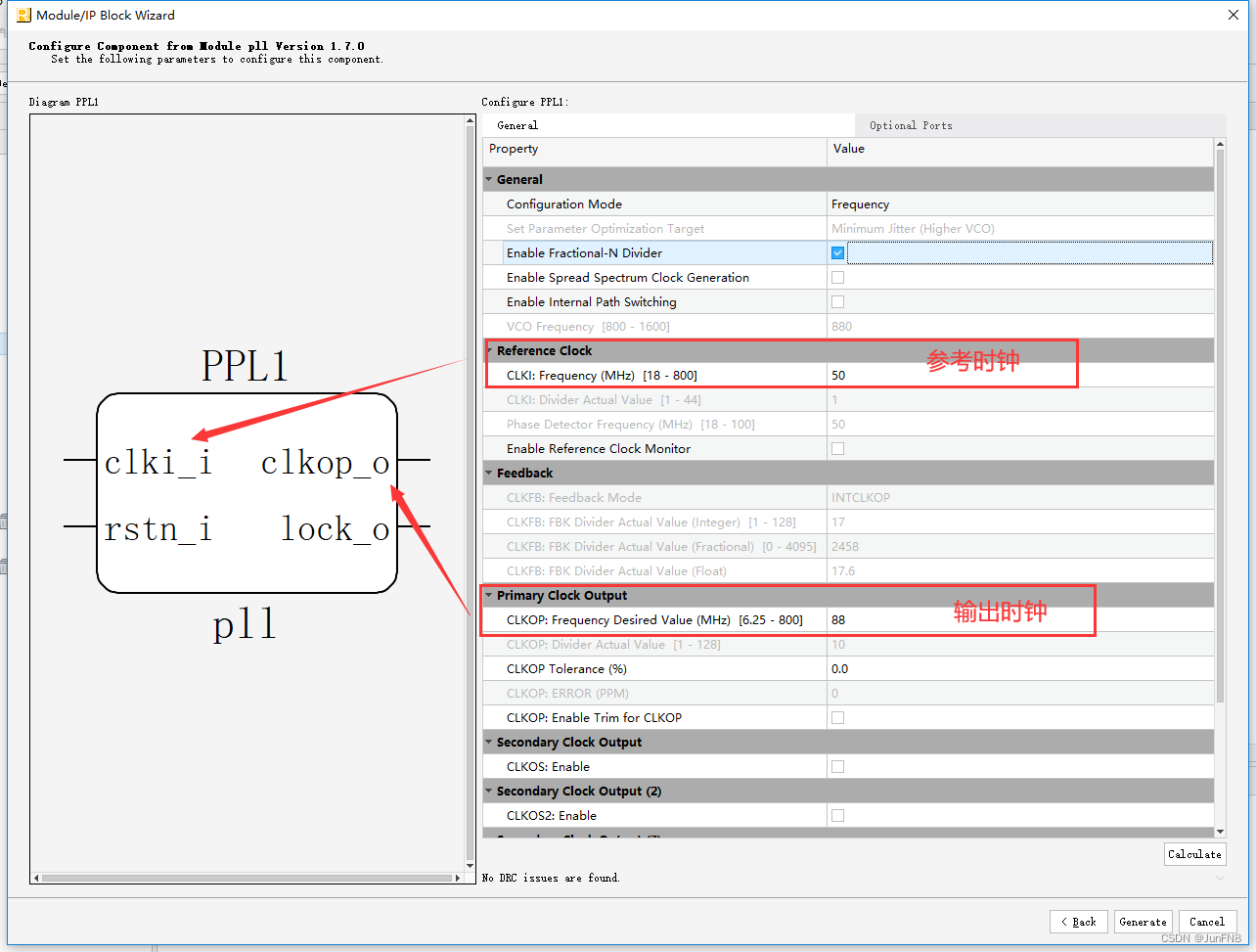

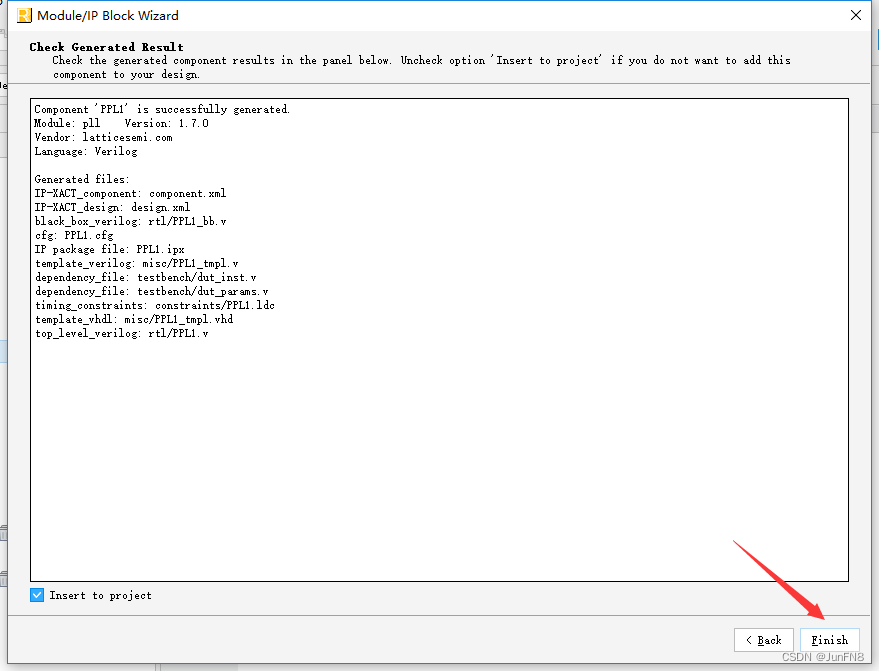

继续PLL的创建。

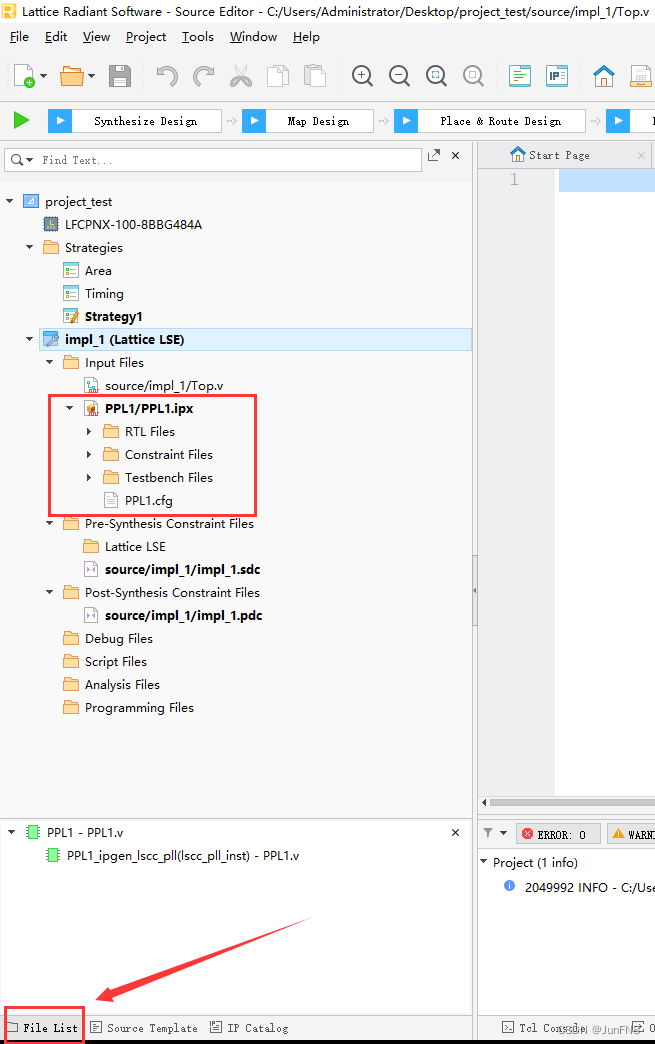

然后点击File List回到文件列表,就能看到刚刚添加的IP信息了。(在testbench里有官方自动生成的仿真源文件,可以自己修改修改进行仿真使用)。

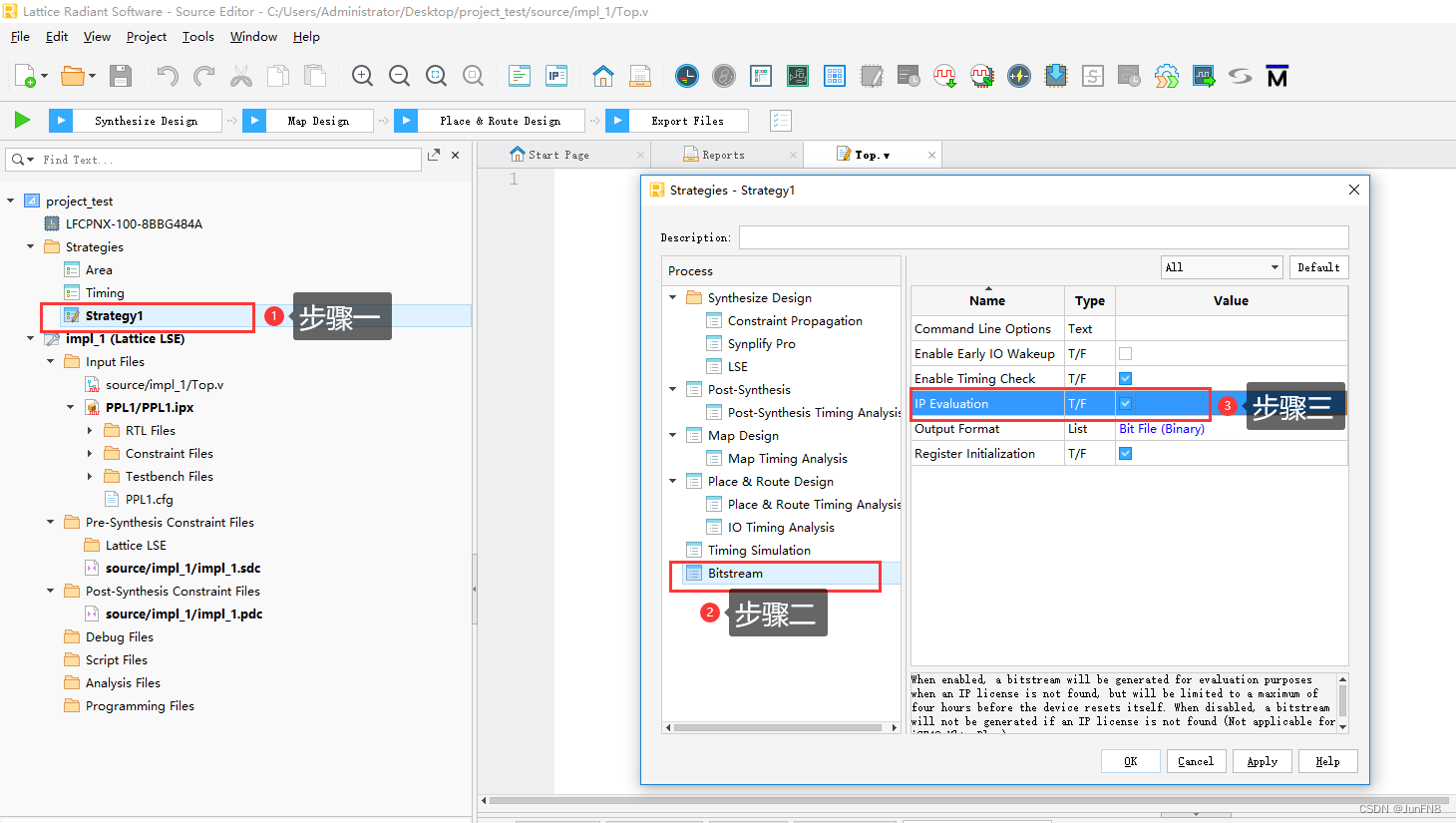

注意:lattice每次新建工程添加IP后都要打开IP许可,在生成bit流的时候才不会报错。(在strategy中还有很多权限,在用到的时候再详细说明)

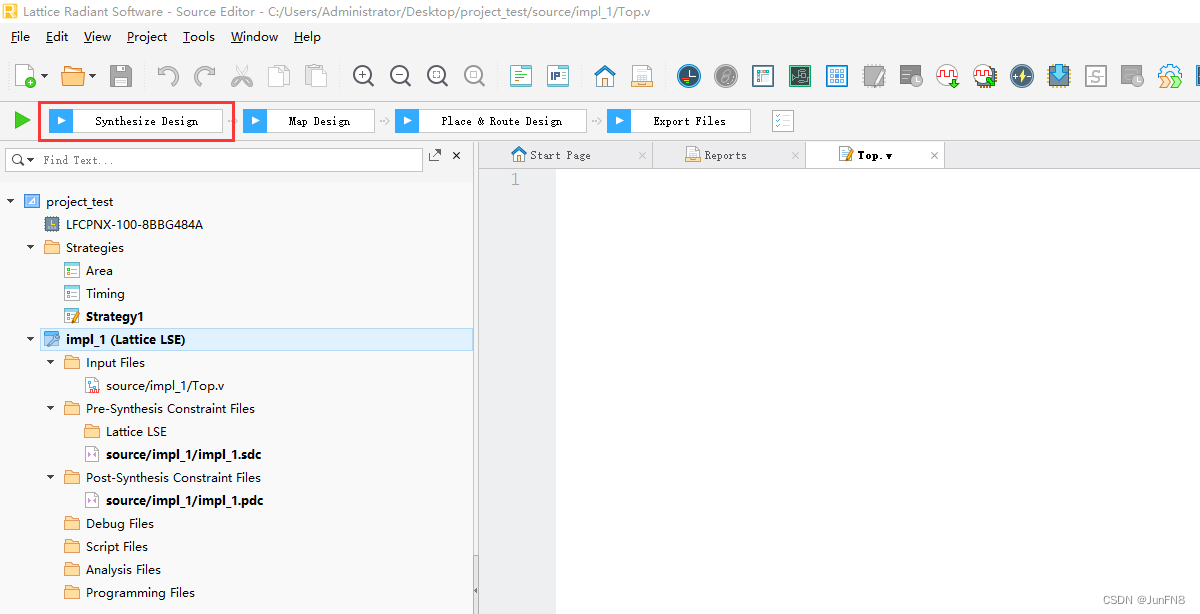

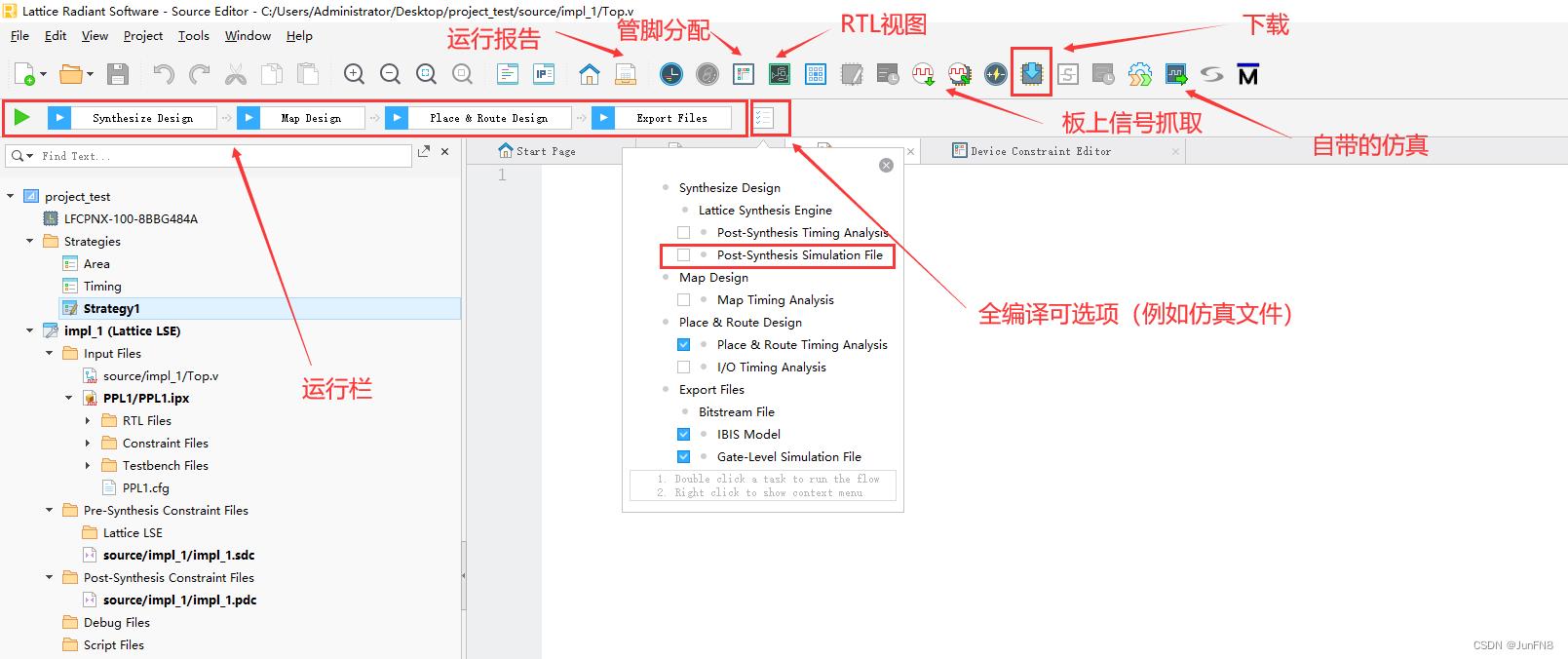

逻辑编写好之后,就可以综合看逻辑有无报错(绿色箭头是全编译,蓝色箭头是指定运行)我们选择蓝色箭头运行综合。

如果有报错会在下面的信息栏中显示报错信息。

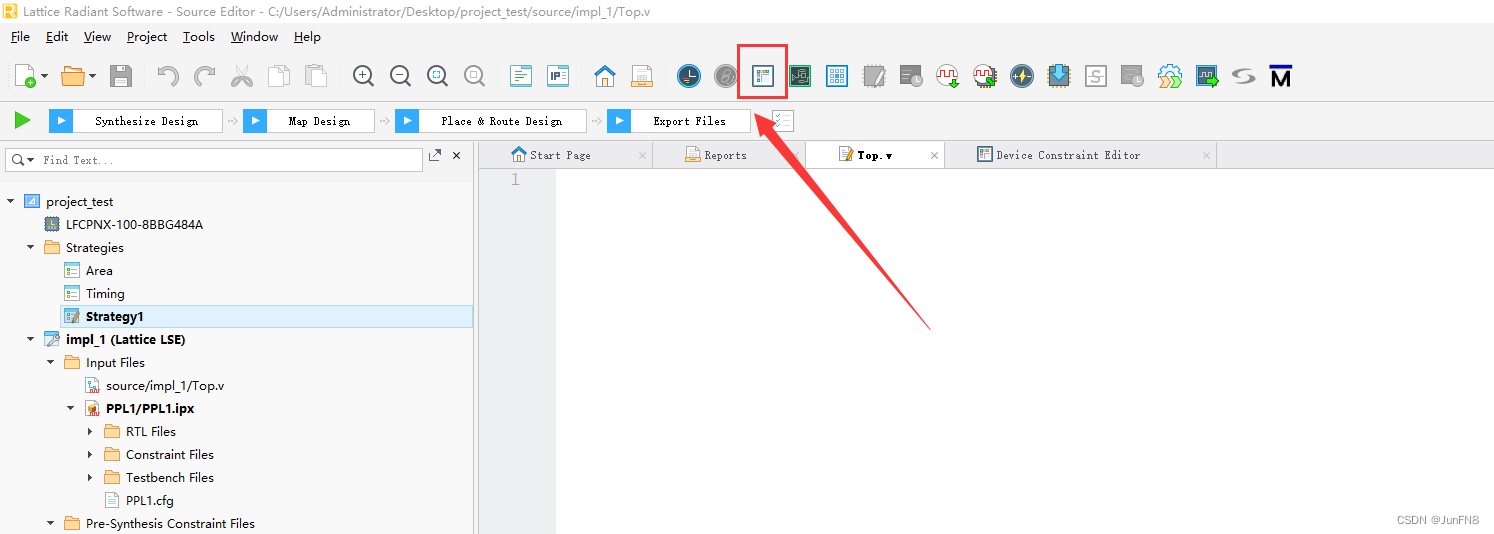

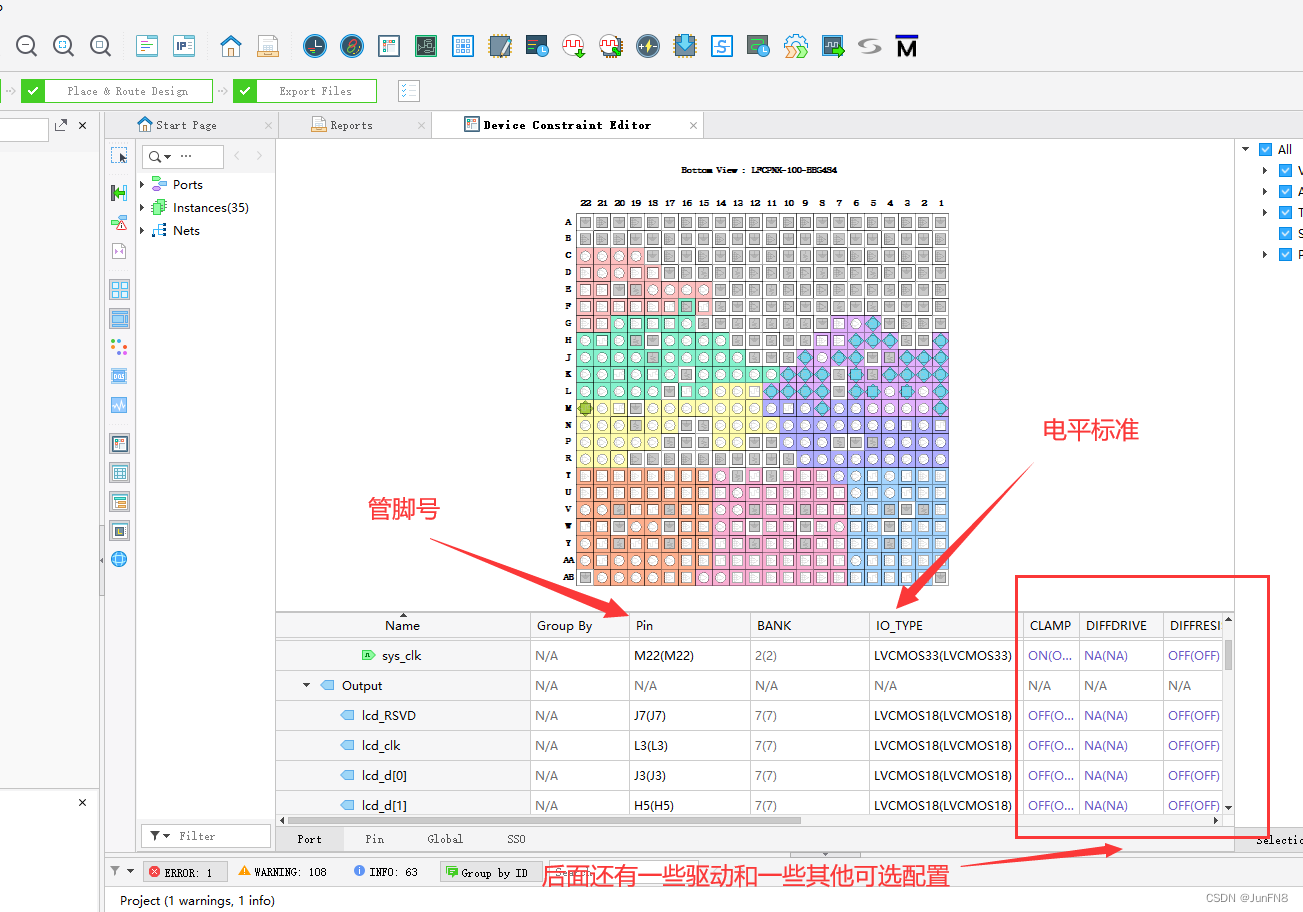

接着就可以进行管脚绑定,在管脚绑定之前先熟悉一下菜单栏中都有些什么吧。

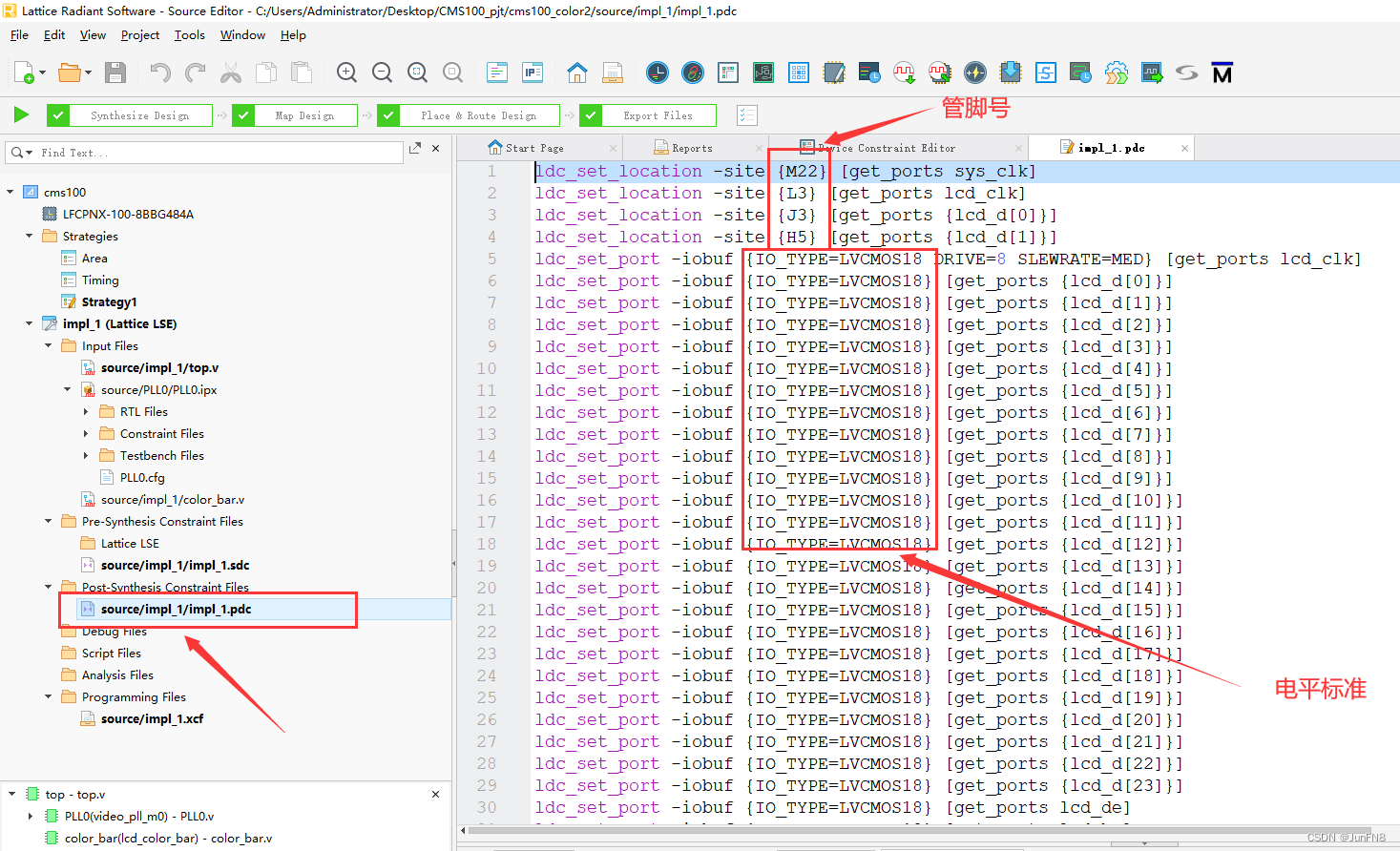

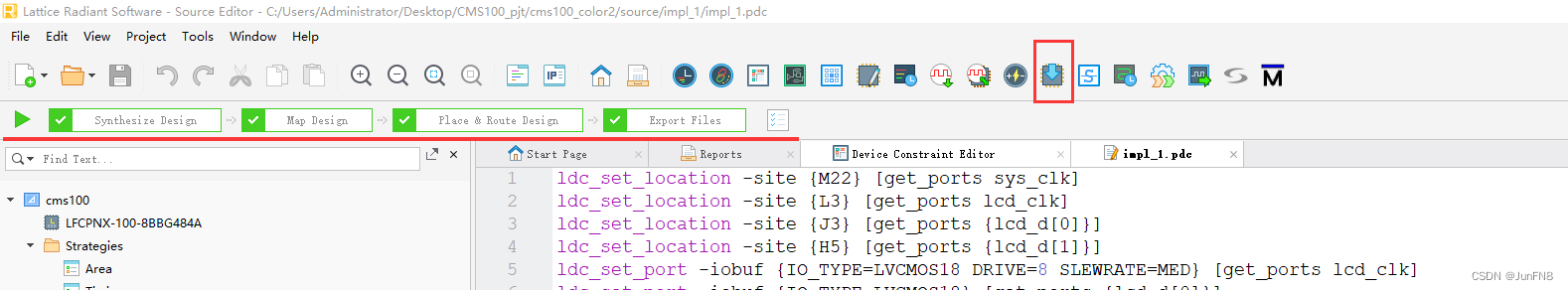

也可以通过.pdc约束文件来配置管脚

步骤四:全编译生成bit流,然后下板

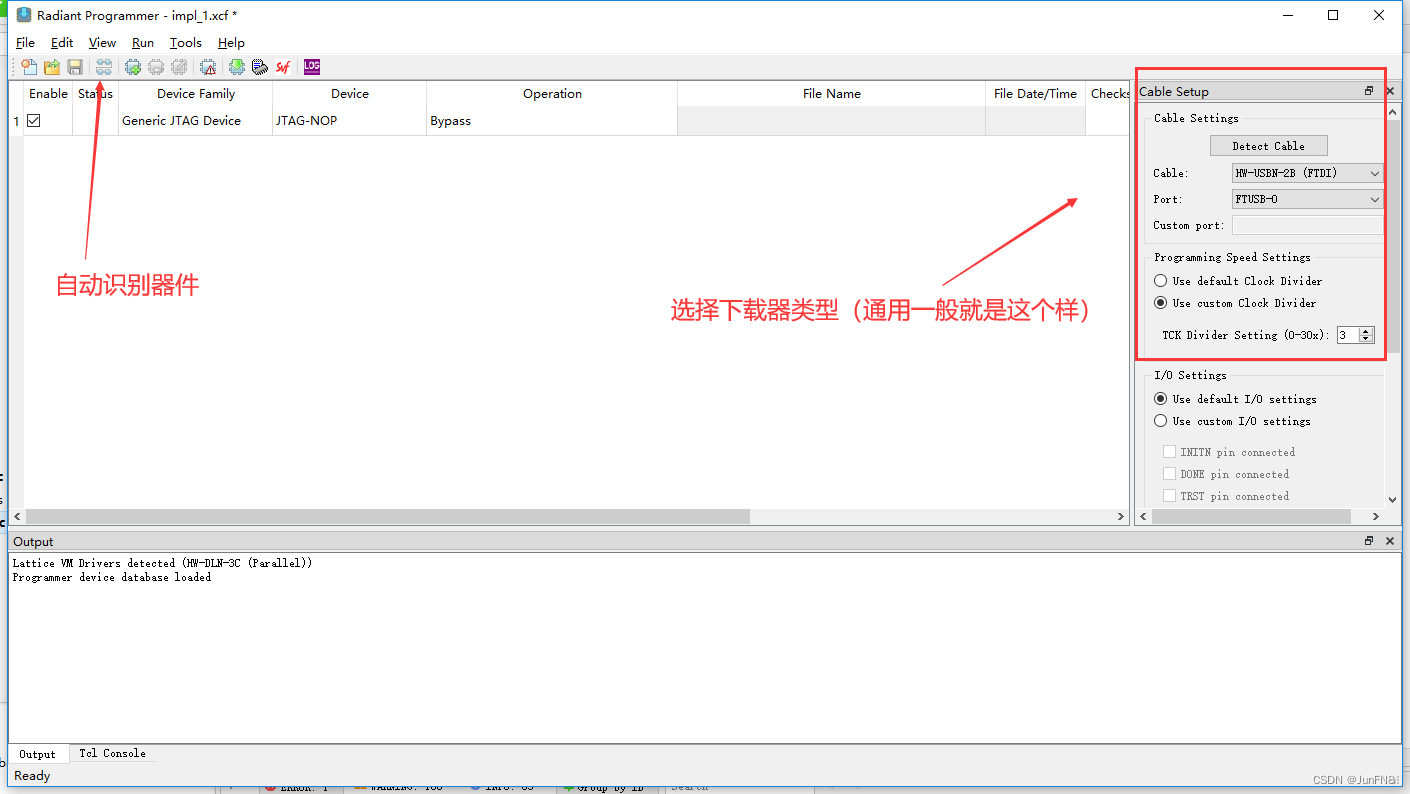

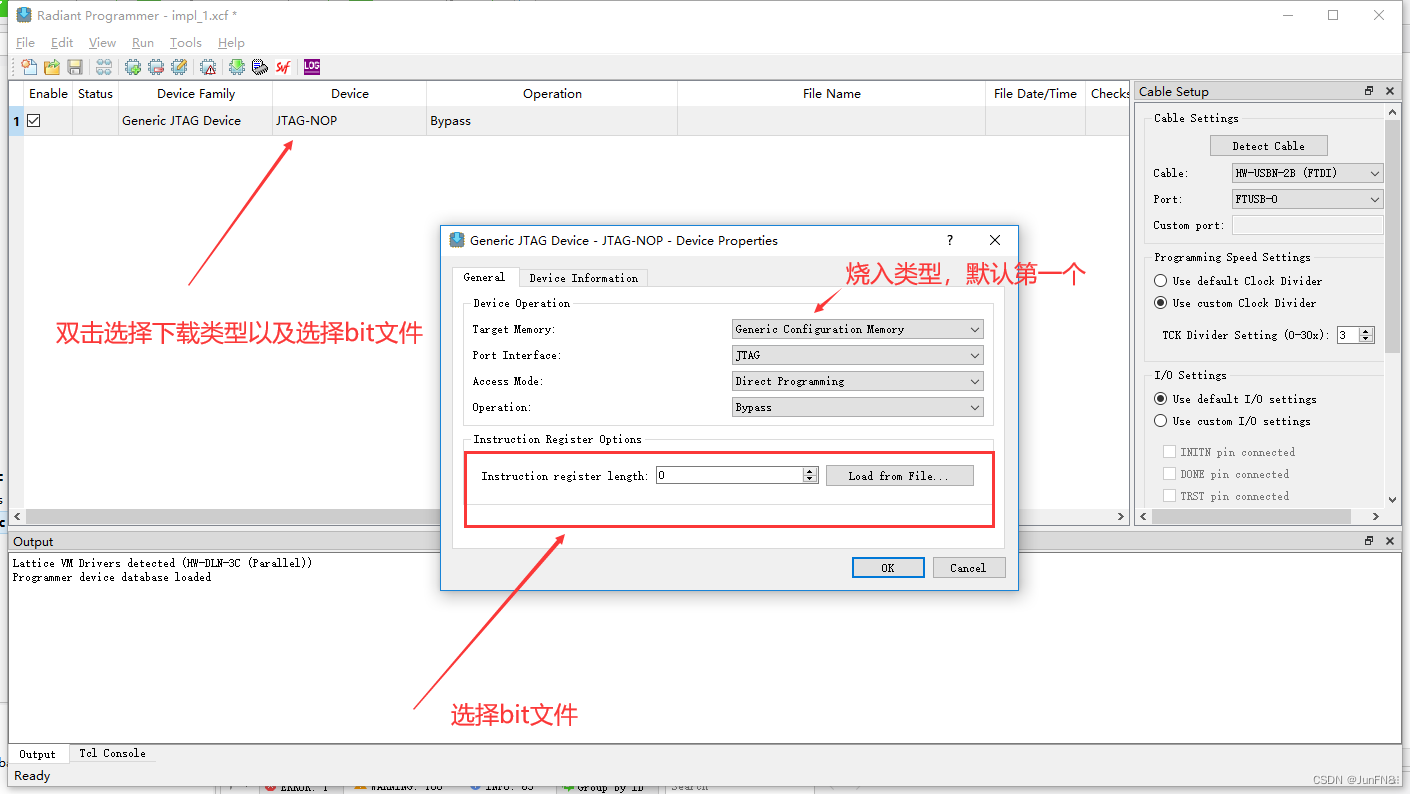

编译通过如下,点击下载程序。

下载器类型不一样的话可以参考官方FPGA Programming Hardware

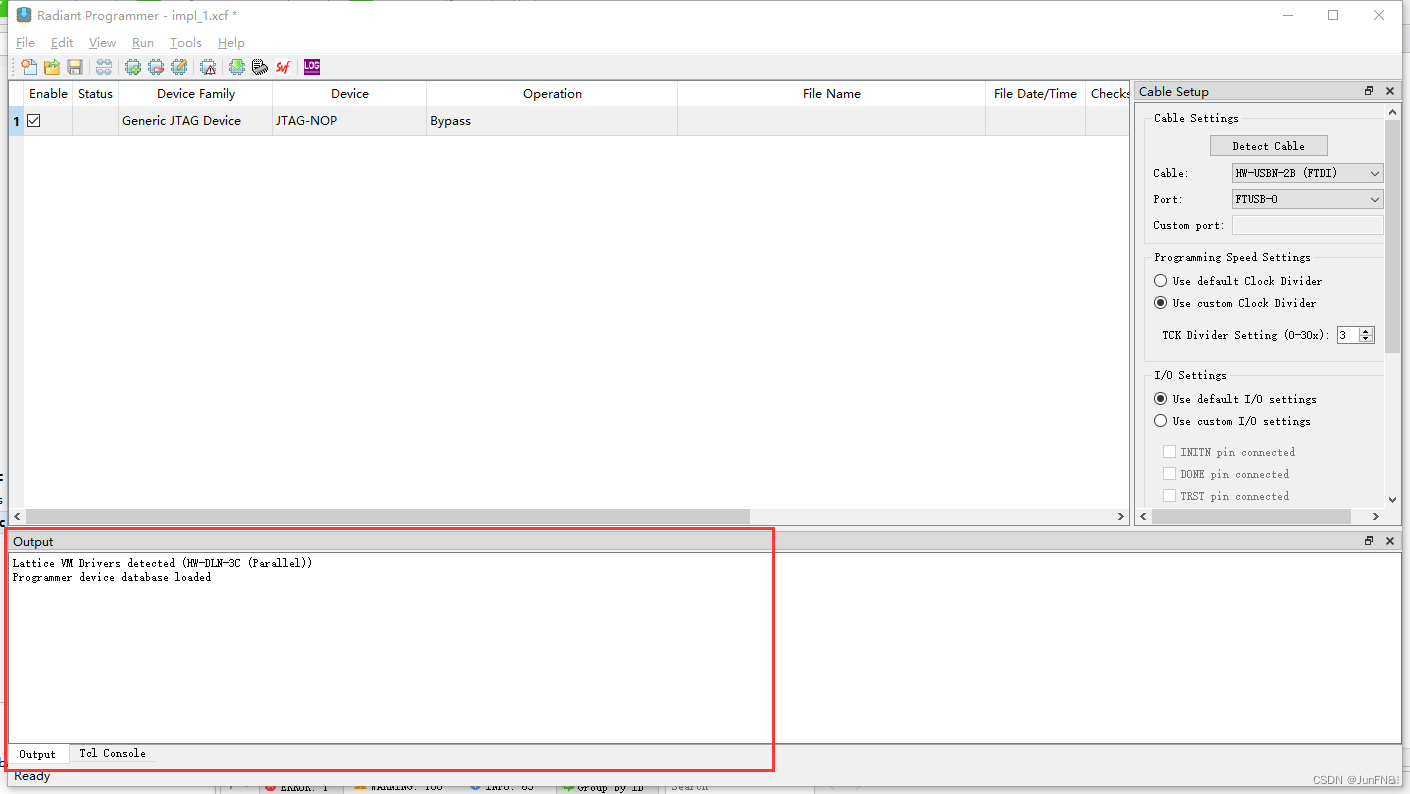

下载成功后会在下面的output信息栏出现success的打印信息。

总结

对于用过Xilinx和Altera的小伙伴来说,Lattice的开发环境也会很快就能熟悉起来。

不过虽然大同小异,很多细节不注意就会花大把时间去纠错。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?