关于ARM内存模型

ARM体系结构是一种弱ordered的内存体系结构,它允许内存的使用者和观察者以不同顺序完成对内存操作。

Note:

Memory ordering用来描述系统中的processor对内存的操作如何对其它processor可见。大多数文献都采用reorder这个表达方式,是从执行等价的角度来描述的:比如P1上执行两个写操作WRITE(A)和WRITE(B),如果对于观察者P2来说P1|WRITE(B)先于P2|WRITE(A)可见,那么就可以认为P1的写操作发生了reorder。对读操作也是类似的。

ARMv8内存模型的基本原理是:

- 提供一种与高级编程语言(例如C或Java)对应的弱order的内存模型。例如,允许其他访问者通过re-ordered查看正在使用中的内存。

- 大多数内存中避免涉及使用multi-copy atomicity。

- 提供指令和内存屏障,以弥补multi-copy atomicity在某些情况的缺陷。

- The use of address, data, and control dependencies in the creation of order so as to avoid having excessive numbers of barriers or other explicit instructions in common situations where some order is required by the programmer or the compiler(标个疑问,不太理解)

Note:Multi-copy atomicity,在多core环境下, store操作的顺序问题以及多个observer之间的交互问题。比如系统中有2个CPU core,每一个core都可以对内存系统中的某个特定的地址发起写入操作,如何保证操作的原子性。

ARMv8内存模型中的定义

Locations

A Location refers to a single byte in memory.

Locations指内存中每个byte位

Memory effect

The Memory effects of an instruction are the read, write, or barrier effects of that instruction.

Memory effects指对内存读、写和barrier指令操作。

Memory effects与以下有关(手册:B2.3.2 Ordering and observability):

Reads-from

A Reads-from relation that couples reads and writes to the same Location such that each read is paired with a single write in the program. A read R2 of a Location Reads-from a write W1 to the same Location if and only if R2 takes its data from W1. Coherence order

A Coherence order relation for each Location in the program that provides a total order on all writes from all coherent Observers to that Location, starting with a notional write of the initial value. Coherence-after

A write W2 to a Location is Coherence-after another write W1 to the same Location if and only if W2 is sequenced after W1 in the Coherence order of the Location.

A write W2 to a Location is Coherence-after a read R1 of the same location if and only if R1 Reads-from a write W3 to the same Location and W2 is Coherence-after W3. Overlapping accesses

Two Memory effect overlap if and only if they access the same Location. Two instructions overlap if and only if one or more of their generated Memory effects overlap. Observed-by

A read or a write RW1 from an Observer is Observed-by a write W2 from a different Observer if and only if W2 is coherence-after RW1.

A write W1 from an Observer is Observed-by a read R2 from a different Observer if and only if R2 Reads-from W1.

Observer

An Observer refers to either a processing element, or some other memory accessing agent that can generate reads from or writes to memory.

Observer指可访问(读、写)内存的进程组件或其他等。

Ordering和observability

ARMv8内存模型允许对内存访问进行重新排序。

本节使用以下方法定义对内存访问进行重新排序的约束:

• Register value dependencies to establish order between instructions on a PE

• Ordering constraints to establish order between accesses to a Location注册值相关性以在PE上的指令之间建立顺序。

排序约束,用于在访问位置之间建立顺序。

Register value dependencies

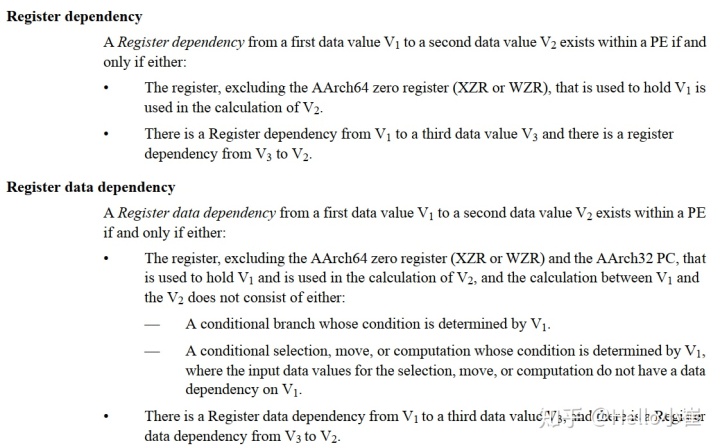

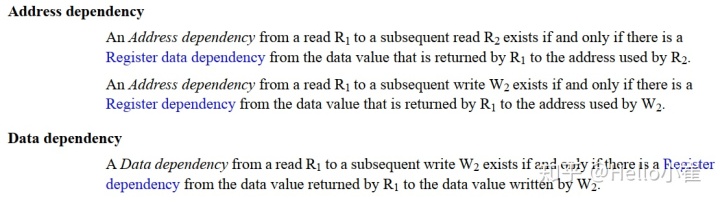

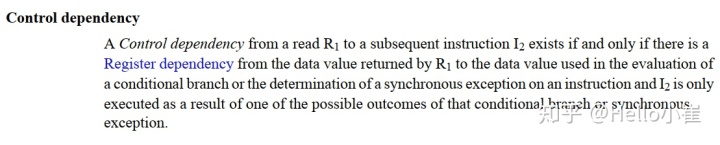

ARMv8内存模型定义了指令之间的以下依赖关系:

Ordering constraints(ordering限制)

Armv8内存模型被描述为Other-multi-copy atomic,Other-multi-copy atomic的定义如下:

Other-multi-copy atomic

In an Other-multi-copy atomic system, it is required that a write from an Observer, if observed by a different Observer, is then observed by all other Observers that access the Location coherently. It is, however, permitted for an Observer to observe its own writes prior to making them visible to other observers in the system.

Peripherals

可以通过Memory-mapped设备方式对外围设备进行读写(寄存器)。

Memory-mapped peripheral

Memory-mapped peripheral行为作用于一段指定的、可进行load&store指令的内存(外设内部内存、由外设提供)。对内存的影响(一般是外设寄存器写操作)可以触发外设的行为。

Peripheral coherence order

The Peripheral coherence order of a Memory-mapped peripheral is a total order on all reads and writes to that peripheral.

参考资料:

《ARM Architecture Reference Manual, for ARMv8-A architecture profile》B2.1 About the ARM memory model和B2.3 Definition of the ARMv8 memory model;

如有错误欢迎指正。

1232

1232

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?