有一天,作者君在看别人做的电路,忽然意识到一个问题:这个designer放电流源开关的位置,和作者君自己的习惯不一样。呃,到底哪种好一些呢?这得想想了……

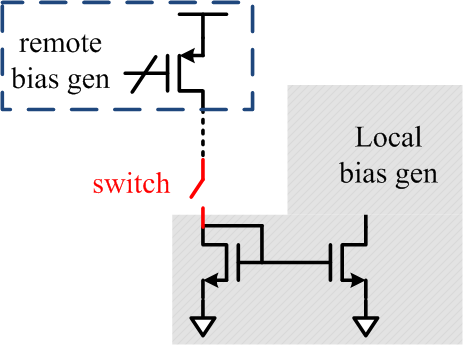

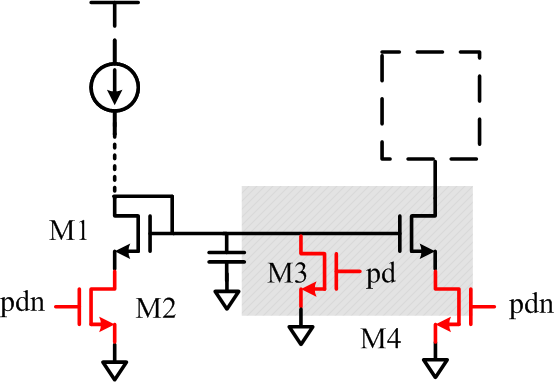

一般来说,我们内部电路的电流,一般是由bandgap之类的模块产生的。当然,bandgap可能本身的driving能力有限,后面一般配个buffer,然后再挂上一堆的PMOS电流源:

比如作者君这张图里面的remote bias gen,假设就是某个buffer的一部分。经过中间不知道有多么长(虚线)的金属走线,最后来到了一个local的模块,比如说一个ADC。当然,为了把这个远道而来的电路变成当地local群众喜闻乐见的好电流,旁边一般还加上诸如电容之类的小心思。不过,大致上的样子,就是作者君上面这张图里画的了。

回到正题,我们如果需要加入可控的功能,比如不想用这个local的ADC,就需要一个开关switch,可以随时关掉这个local bias gen。这个红色的开关,现在画在这里,大家有什么想法吗?

正常的开关当然是transistor,那么,到底要怎么放这个transistor呢?

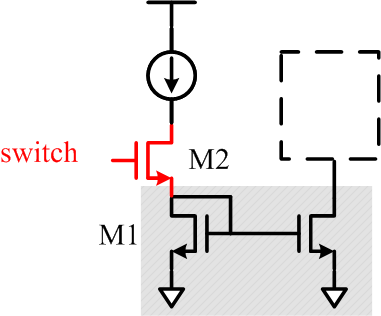

好了,一个直观的想法就是这样。这个M2就是我们需要的东西。不过,怎么看起来有点那个啥啥?如果在低电压的电源下工作,比如典型的65nm以下的工艺,CMOS的VDD一般也就1.2V,假设Vth是450mV,我们稍微算算:

下面的M1是diode connection,所以M1的drain上面的电压大概是450+200=650mV,同时,这个电压也是M2的source电压。一般M2需要导通的时候,M2的gate连到了最高的Vdd,也就是1.2V。这样一来,M2的Vgs=1.2V-0.65V=0.55V。

所以说,我们以为M2是个非常好的,有着很大的Vgs,完全工作在线性区的完美的开关。结果,人家的Vgs只有可怜兮兮的不到一半的vdd。人世如此艰难,若是再去个ss Corner,vth再大点,那这个小可怜M2还能导通吗?这是个问题……

除此之外,M2因为可能vgs不够大,但是电流Id又被远处的电流源给限定了。所以,vgs不够的情况下,怎么办呢?靠Vds了!很可能的情况,会是M2在绝境中开始施展拳脚,上下去豪取抢夺需要的Vds(M2的Vds可能大于200mV,不是我们以为的几mV)来满足Id的要求。因此,可能我们远处的电流源那个PMOS被M2压得Vd一直上升,导致说好的10uA的电流,变成了9uA或者更小。悲剧 啊!

总结一下:1)M2的Vgs可能不够;2)M2需要导通一定的电流,Vgs不够的情况下,Vds需要增大,因而减小了上下两个transistor的vds。

既然已经知道了问题所在,那么怎么做可以解决这个问题呢?

换个位置!

前面Fig.2的M2,祸源是因为它除了需要表现得像是一个完全的开关,可以正常的导通或者断开,还得承担一定的电流运输工作。前一项,我们可以认为是数字的功能,后一项,我们可以认为这是模拟的功能。也就是说:

- 数字功能:通路的on/off;

- 模拟功能:电流输送能力强or弱;

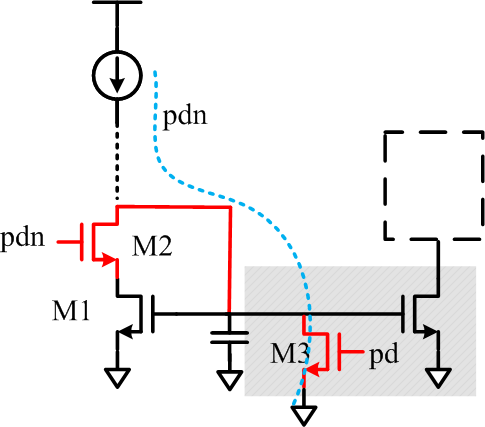

So,我们如果专注于其中一项功能,也就是关键的数字功能,fig.3的结构就很实用了。在这里,M2只控制M1的gate和drain。因为CMOS transistor的gate上面基本上没电流(leakage暂时不谈),这样一来,即使M2不能完美的实现最大的vgs(等于1.2V的Vdd的Vgs,比如大部分的逻辑电路),但是此时的M2没有输送电流的需求,即使等效于一个大的电阻,也并不会影响主要通路,也就是从上面的PMOS到下面的diode M1。

同时,有时候我们会在M1的gate上面加个电容,还能一定程度起到LPF的作用。毕竟后面的local bias gen,关心的就是M1产生的这个Vg嘛!

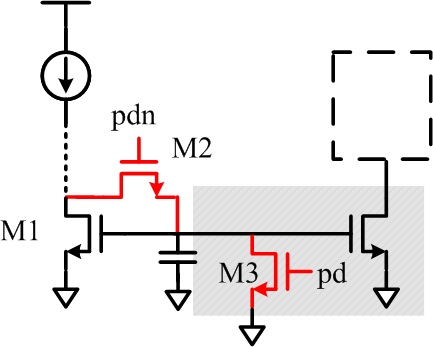

But!作者君最后想起来一个事情:要想在power off的时候,真正的完全关掉M1,Fig.3里面的M2可能还是不够用!一个floating gate的M1,听起来总是感觉有点人心惶惶的……再在M1的gate上面加一个power off的开关吧!也就是M3了。M3的控制信号跟M2是相反的,所以能够在M2断开的时候,把M1的gate拉到vss,防止M1的gate上面的残余电荷造成不必要的麻烦。

PS:评论里面有位同仁说还可以这样:

Fig.4的好处,在于M2的Vgs等于Vdd,保证了M2一定会fully on。(不像Fig.3里面的M2的Vgs可能还是不太够用)但是,为了让M1的source不至于太大(后面电路的source都是连着vss,所以M1的source最好也是Vss。刚刚评论说道matching,作者君就加了个M4,反正后续电路别用M1的gate电压,重新生成吧!),M2的尺寸还是大一些的好。so,有点浪费面积……

话说,一个简单的开关,作者君啰里啰嗦写了这么多,自己都有点嫌弃了……其实,作者君觉得,作为一门真正的工程学科,真的就是要考虑得面面俱到。有时候一点点小小的问题,实际量产的时候,可能就会被无数倍放大。大家一定要慎重!

最后放一个链接:

有哪些你觉得是常识,但大部分人好像并不知道的事?www.zhihu.com

不知道为什么这个回答没什么人看。作者君也是辛辛苦苦找的图好伐!泪流满面……

微信公众号:analogIC_gossip

评论已经有两个人提到这种结构了,我多说一句:

诚然,M2类似于cascode,在没有M3存在的前提下,M2的source是M1的drain,相比于前面fig.2的结构,M2更容易导通。但是!不能不加M3,so,M2关的时候M3打开,上面的电流源顺着M3流到了vss,这样的漏电不是我们想看到了……

微信公众号:analogIC_gossip

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?