Verilog HDLBits--Count Clock (Complement)

这篇文章延续上一篇HDLBits--(Verilog在线学习)--"105: Count Clock"。继常规 one-digit BCD编码,各位(如分钟的个位、十位等)分开单独显示 方法后,笔者提出一种十进制计数直接转BCD显示的方法。为强调两种方法的区别,本文方法取名为two-digit BCD(时钟计数中最高涉及到两位数)。相比 one-digit BCD 设计,two-digit BCD 需要额外的十进制计数器进行时钟计数,然后直接将该十进制数字转换成BCD编码。该方法常用于二进制转BCD编码类问题,涉及移位加3算法,笔者也会简要说明。

为方便阅读,这里先附上题目。

Problem105: Count Clock (Complement)

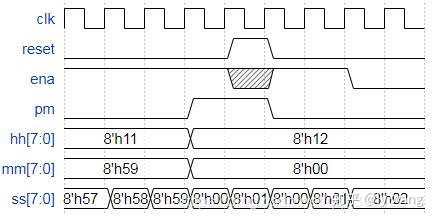

要求: 设计一个满足12小时计时的时钟系列计数器(包括am/pm指示)。该计数器由一个fast-running clk驱动,每当时钟需要增加计时时,ena信号则会发生脉冲信号(如:每秒一次)。 reset信号复位时钟到12:00 AM。pm信号为0时指示AM,为1时指示PM。hh、mm、ss都为两个BCD digits(8 bits),分别表示小时(01-12)、分钟(00-59)、秒(00-59)。reset 比 enable信号优先级更高,即使未使能,也要执行复位操作。 下面的时序图展示了时钟从11:59:59 AM 到12:00:00 PM的信号变化,以及同步复位和使能操作结果。

hint: 注意11:59:59 PM 在下一个时钟周期应为12:00:00 AM ;12:59:59 PM 在下一时钟周期应为 01:00:00 PM 。没有00:00:00这种形式。

1 正确答案

1 module top_module(

2 input clk,

3 input reset,

4 input ena

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6855

6855

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?